芯片设计流程中,验证是至关重要的,验证除了常规必备的Simulation还有非常重要的FPGA原型验证,但是,在对ASIC代码到FPGA移植过程中,这是非常关键的一环。

在对ASIC设计进行FPGA原型验证时,由于物理结构不同,ASIC的代码必须进行一定的转换后才能作为FPGA的输入。

现代集成电路设计中,芯片的规模和复杂度正呈指数增加。尤其在ASIC设计流程中,验证和调试所花的时间约占总工期的70%。为了缩短验证周期,在传统的仿真验证的基础上,涌现了许多新的验证手段,如断言验证、覆盖率驱动的验证,以及广泛应用的基于现场可编程器件(FPGA)的原型验证技术。

采用FPGA原型技术验证ASIC设计,首先需要把ASIC设计转化为FPGA设计。但ASIC是基于标准单元库,FPGA则是基于查找表,ASIC和FPGA物理结构上的不同,决定了ASIC代码需要一定的修改才能移植到FPGA上。但应该注意到这只是由于物理结构不同而对代码进行的转换,并不改变其功能,因此对代码的这种修改只能限制在一定范围内。

基于FPGA原型验证的流程

由于FPGA的可编程特性,基于FPGA的原型技术已经被广泛采用。和仿真软件相比,FPGA的硬件特性可以让设计运行在较高的频率上,加速仿真。另一方面,可以在ASIC芯片设计前期并行设计外围电路及应用软件,缩短了芯片验证周期。

FPGA原型验证和其他验证方法是不同的,任何一种其他验证方法都是ASIC验证中的一个环节,而FPGA验证却是一个过程。由于FPGA与ASIC在结构、性能上各不相同,ASIC是基于标准单元库,FPGA用的是厂商提供的宏单元模块,因此首先要进行寄存器传输级(RTL)代码的修改。然后进行FPGA器件映射,映射工具根据设置的约束条件对RTL代码进行逻辑优化,并针对选定的FPGA器件的基本单元映射生成网表。接着进行布局布线,生成配置文件和时序报告等信息。当时序能满足约束条件时,就可以利用配置文件进行下载。如果时序不能满足约束,可通过软件报告时序文件来确认关键路径,进行时序优化。可以通过修改约束条件,或者修改RTL代码来满足要求。

存储单元

存储单元是必须进行代码转换的,ASIC中的存储单元通常用代工厂所提供的Memory Compiler来定制,它可以生成.gsp、.v等文件。.v文件只用来做功能仿真,通常不能综合。而最后流片时,只需将标准提供给代工厂。如果直接将ASIC代码中的存储单元作为FPGA的输入,通常综合器是综合不出来的,即使能综合出来,也要花费很长时间,并且资源消耗多、性能不好。而FPGA厂商其实已经提供了经过验证并优化的存储单元。因此存储单元要进行代码转换。

时钟单元

数字电路中,时钟是整个电路最重要、最特殊的信号。在ASIC中,用布局布线工具来放置时钟树,利用代工厂提供的PLL进行时钟设计。FPGA中通常已经配置一定数量的PLL宏单元,并有针对时钟优化的全局时钟网络,一般是经过FPGA的特定全局时钟管脚进入FPGA内部,后经过全局时钟BUF适配到全局时钟网络的,这样的时钟网络可以保证相同的时钟沿到达芯片内部每一个触发器的延迟时间差异是可以忽略不计的。因此时钟单元也是需要进行转换的。

增加流水

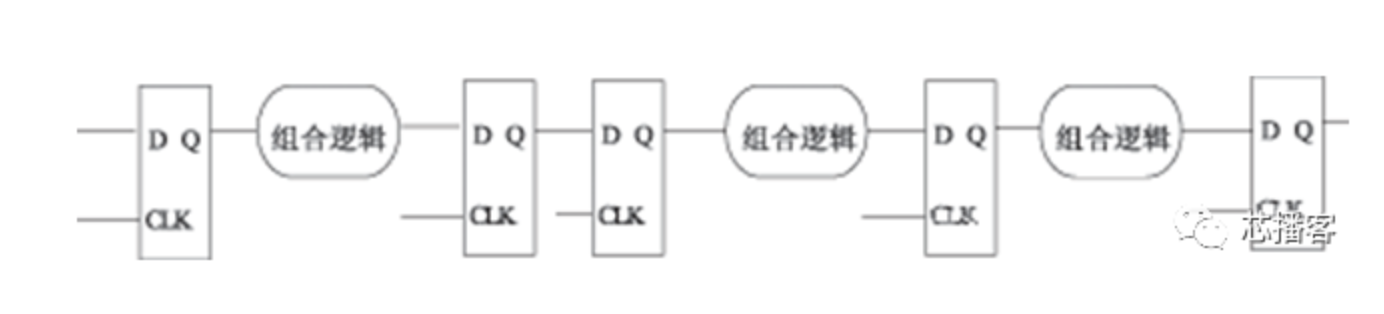

由于实现结构上的不同,FPGA器件内部的单元延时远大于ASIC的基本门单元延时。导致在同样设计的情况下,ASIC可以满足其时序,而FPGA有可能无法满足。为了验证的需要,修改ASIC代码实现FPGA原型时,对ASIC实现的流水结构在FPGA实现时需要适当增加流水。比如在一个很长的组合逻辑路径中加入寄存器。如图1所示。

在FPGA设计中,同步设计是应该遵循的重要原则。异步设计容易导致电路处于亚稳态,产生毛刺。当从ASIC设计转向FPGA设计时,应该进行仔细的同步。具体体现在主时钟选取、功能模块的统一复位、同步时序电路设计。

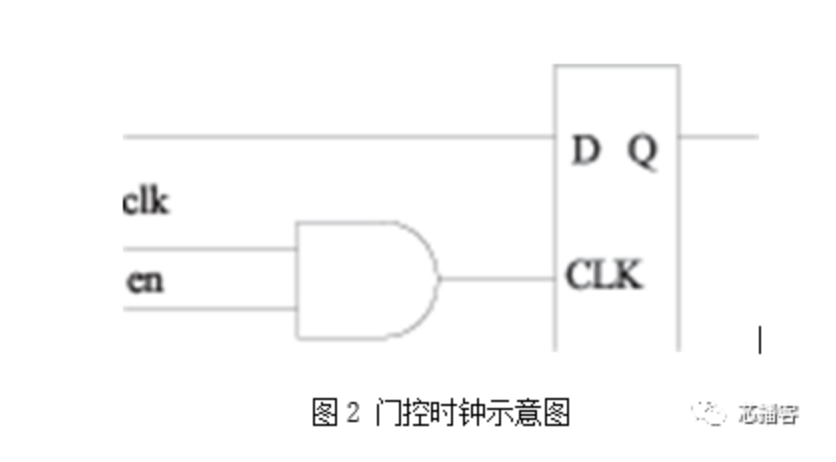

在FPGA设计中要使用时钟使能代替门控时钟。在ASIC的设计中,为了减少功耗,使用门控时钟(clock gating),门控时钟的结构如图2所示。当写有效时,数据才写进存储器,那么只有写有效时,寄存器才会发生翻转,这样可以减少功耗。

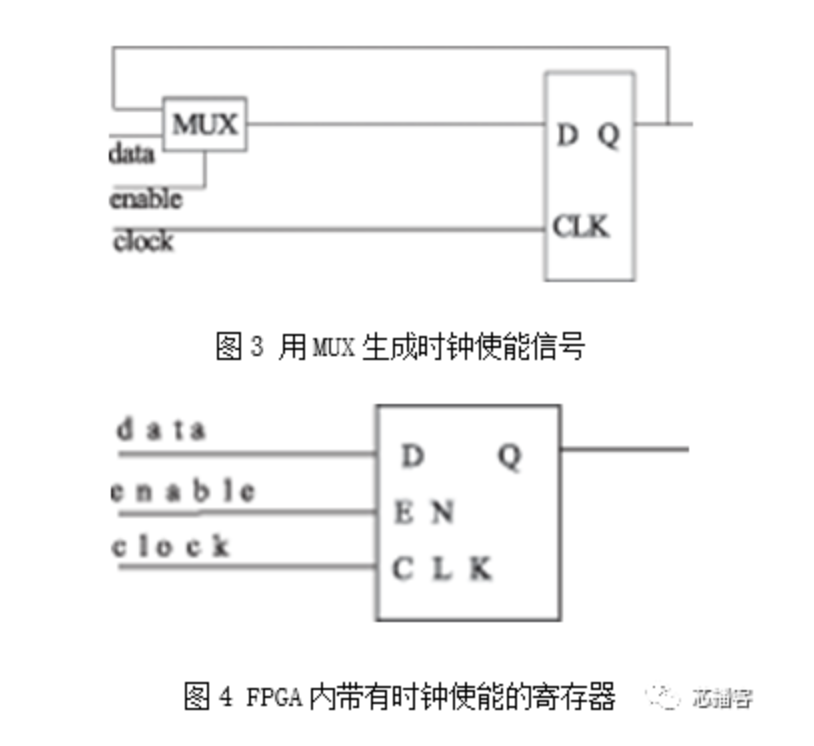

由于设计的异步特性,对于FPGA来说,使用这种门控时钟容易产生毛刺,导致数据不正确。所以在FPGA设计中,使用有使能信号的电路来替换门控时钟电路。可以在寄存器前面加上MUX来实现时钟使能信号,如图3所示。现在的FPGA厂商则提供可以直接有使能,同步SET和RESET引脚的寄存器,如图4所示。

充分利用FPGA中已有的IP核

FPGA厂商及第三方厂商已经实现并优化了很多典型的IP核,例如Xilinx提供了基础逻辑、总线接口与I/O、视频与图像处理、数字信号处理、存储器接口、微处理器、控制器等大量IP核。在代码转换时可以充分利用这些资源,对代码进行优化来提高设计性能。如在FPGA中使用SRL实现移位寄存器,用三态Buffer来替换三态总线和三态MUX,改进算术单元和有限状态机的编码。

作者: Jacky Yu

文章来源:芯播客

推荐阅读

芯片软硬件协同验证的痛点推动FPGA原型验证不断向前

从SoC仿真验证到FPGA原型验证的时机

细聊时钟树综合CTS阶段如何去降低Latency和Skew

更多IC设计请关注IC设计技术专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。