1. 定向激励测试和受约束随机激励测试有什么不同?它们各有什么优势和劣势?

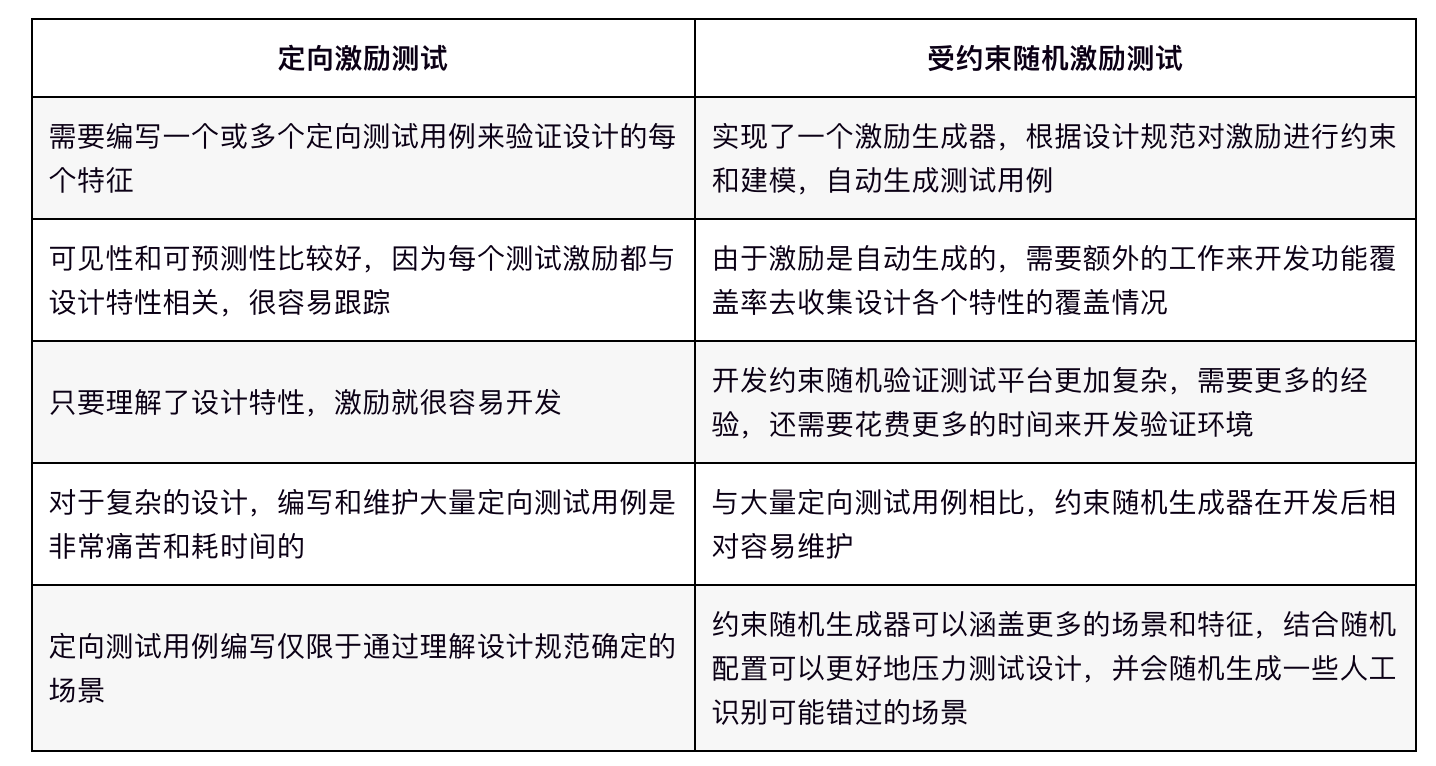

定向激励测试是一种为验证设计中的每个特性而编写定向测试用例的方法。受约束随机测试是一种使用约束随机生成器根据设计规范自动生成激励的方法。目前比较推荐的做法是两者一块用,使用受约束随机激励测试来覆盖大部分验证空间,然后定向激励测试覆盖难以到达的边界情况。

2. 解释下什么是自检测试(self-checking tests)?

自检测试是测试用例在测试结束时,可以通过某种方式对测试结果自动进行检查的测试。可以在测试中通过计算某些内存操作的结果或通过从DUT收集信息(比如状态寄存器或任何其它信息)来预测结果。

3. 什么是覆盖率驱动(CDV)的验证?

在覆盖率驱动的验证方法中,验证计划是通过将每个设计特性或场景映射到可用于在仿真期间收集覆盖信息的覆盖率监视器来实现的。

- 在基于覆盖率驱动的验证中,测试用例通常使用约束随机激励生成器产生,测试正确性由功能检查器保证,并且为所有实现的覆盖率监视器收集覆盖率;

- 通常需要在DUT上对多个测试用例或随机生成器的多个种子进行回归,并将从每个测试中收集的单个覆盖率合并以获得累积覆盖率。有时,在DUT中的边界场景需要使用定向测试去覆盖;

- 覆盖率信息提供了对随机激励生成器的约束质量的反馈,有助于调整约束来更有效地生成随机激励;

- 在这种方法中,覆盖率定义是跟踪验证执行的进展和完成的关键步骤,因此必须要根据验证计划和设计规范去检查覆盖率定义和实现的完备性和正确性;

- 覆盖率监视器可以是基于covergroups和property。

4. 什么是基于断言的验证(ABV)方法

基于断言的验证使用断言来捕获特定的设计意图,然后simulation、formal验证或emulation中使用这些断言验证设计实现是否正确。ABV方法利用断言的优点来补充其它功能验证方法,断言的一些好处如下:

断言可以从源头上检测设计错误,从而有助于提高可观察性并减少调试时间;

相同的断言既可以用于simulation,也可以用于formal验证,甚至可以用于emulation;

断言库中提供了许多针对通用设计的断言,并且可以很容易地移植到任何验证环境中;

作为property编写的SystemVerilog断言也可以用于覆盖率收集,因此有助于覆盖率驱动验证方法。

5. 给定一个具有单读写端口的RAM,需要验证哪些条件?

单端口RAM只有1个端口用于读写,因此它只能在任何给定的时间点进行读或写操作。需要考虑验证的其它设计规范是RAM大小、地址和数据总线宽度、支持的读写密度等。

基于此,以下是一些需要验证的场景:

- 单次读和写功能正确;

- 对同相同地址或重叠地址或不同地址进行多次读读、写写、读写和写读;(如果RAM是行列组成的结构,那么也要针对同行和同列的地址进行测试,以及跨行跨列等)

- 验证读和写访问RAM的边界地址;

- 验证对单端口进行不同的读写密度测试,比如背靠背、两笔操作之间小的延迟或非常大的延迟;

- 验证写入RAM位置的不同数据类型,比如写全0、全1、交替0/1等模式;

作者:谷公子

文章来源:CSDN

推荐阅读

更多IC设计干货请关注IC设计专栏。

迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。