前言

之前有记录过关于总线的概览学习:

- 【FPGA验证学习(五):SoC的总线架构】[1]

- 【SoC系统结构设计(三):SoC中常用的总线】[2]

- 【关于总线的学习(一):入门篇】[3]

本篇来详细学习一下关于AXI总线的相关知识

参考的资料博客链接已放在文末,感恩前辈优秀的分享。

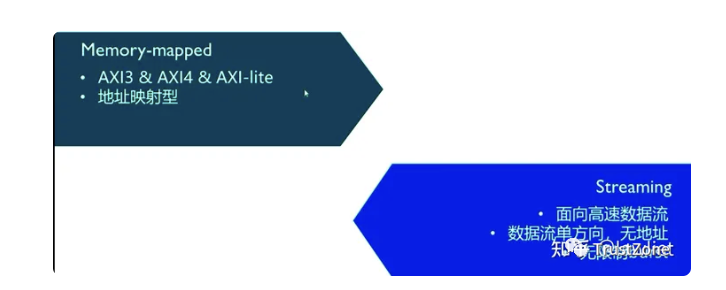

以AXI4为例,有AXI full/lite/stream之分。

在Xilinx系列FPGA及其有关IP核中,经常见到AXI总线接口,AXI总线又分为三种:

- AXI-Lite,AXI-Full以及AXI-Stream,其中AXI-Lite和AXI-Full都是基于memory map的形式实现数据传输(即包括地址总线),而AXI-Stream是以数据流的形式传输,无地址。

- 其中AXI-Lite是AXI-Full的简化版,适合小批量的数据传输,常用来进行命令的传输,IP核的初始化等。

- AXI-Full则适用于大批量,高性能的数据传输。

AXI是一种用于传输数据的模块或总线,用于两个模块或多个模块之间相互传递数据。它本身有很多优点,被SOC广泛采用了。

1.AXI传输数据的过程

AXI-full传输数据是全双工的,也就是说,读写是同时进行的。

一条AXI总线有5条通道,两个用于读,三个用于写。

首先描述一下AXI的写数据过程:

(1)Master主机通过写地址通道将地址传给Slave从机,从机收到地址可通过写数据通道往里送入数据,写完之后通过写回应通道给主机一个结束信号。

(注:写回应通道只需2个bit位就能代表四种状态,传成功了,传失败的几种状态)

(注:写回复是针对整个传输操作(transcaction)的,而不是针对每个写入数据(data transfer))。

AXI读数据的过程:

主机给从机一个地址,从机通过读数据通道给主机返回数据。

为什么读只需要两个通道?因为完成信号可以用读数据传输一并传输。

2.握手协议

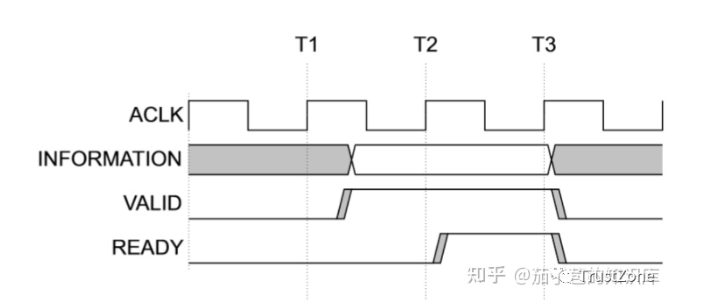

valid与ready信号分三种情况:

(1)valid信号先到达

主机valid信号早早就到了,T2时刻并没有见到接收方的ready信号。只能在T3时刻传输完成。

协议规定在这种情况下,valid信号一旦置起就不能置低,直到完成握手,至少传输一周期数据。 协议另外规定:发送方不能通过等待接收方 READY 信号来确定置起 VALID 信号的时机。

通俗来讲就是设计发送方逻辑时,不能将 READY 信号作为置高 VALID 逻辑的条件,比如将 READY 信号通过组合逻辑生成 VALID 信号,但接收方的ready信号按照协议可以依赖发送方的valid信号。

(2)ready信号先到达

ready信号很自由,可以等待valid信号到来之后再做响应,也可在valid信号到来前就置高,表示接收端已经做好准备。

而且,READY 信号与 VALID 不同,接收方可以置起 READY 之后发现:其实我好像还挺忙,然后置低 READY 信号。只要此时 VALID 信号没有置起,这种操作是完全可以。

(3)tips

上面提到了AXI总线是全双工的,全双工就意味着该总线的读写通道是分开的,互不影响,那就意味着每条通道都是单向传输,单向传输的通道就意味这两端节点的身份有差距,在AXI总线传输中,通道两端分为Master和Slave,主机总是发起读写请求的一方。

常见主机有CPU、DMA,而存储介质控制器则是典型的从机。主机可能通过从机读取或者写入存储介质。而显然从机不可能主动向 CPU 写入数据。

3.通道定义

(1)读&写地址通道(ARC&AWC):

写入本次传输操作所需的地址和控制信息,读写操作都拥有各自的地址通道。

(2)读数据通道(RC):

读数据通道上包括从机发送给主机的读数据,以及从机对于本次读传输操作的回复,具体的读操作状态回复情况会在之后讨论。总线数据位宽可以是 8,16,64,128,256,512 或者是 1024 比特。

(3)写数据通道(WC):

写数据通道用于将主机的写数据传输至从机,位宽和RC的数据位宽相同。WC 有一点 RC 所不具有的特性是拥有 STROBE 信号,用于标识写数据中有效的传输字节。即有些无效的数据,出于减少主机工作量的目的,或者在读写宽度不对称时,被放到写数据通道上和有效数据一起发送。而 STROBE 的信号的作用就是标识出这些无用的数据,告知从机不需要接收无用数据。(Master:我太懒,以至于把所有信号都送过来了)

写数据通道设计有缓存,可超前于从机响应本次传输操作,发起下一次写传输操作。

(4)写回复通道(RC):

用于从机将写操作响应回复给主机。所有写传输操作都需要以写回复通道上接收写响应作为完成信号。再次强调,写回复是针对一次传输操作(transcation)的,而不是针对每一次写数据(data transfer)。

那么问题来了,为什么只有写回复通道而没有读回复通道呢?

这个问题可以从数据流向看出来,主机在读取数据时,数据在读通道上传输,流向为从机到主机。而读回复由从机向主机报告读操作的情况,信号的数据流向也是从机到主机,所以读回复可以合并在读数据通道中,搭个顺风车。

但写回复通道的数据流向就和写数据相反。写数据是从主机到从机,而写回复为从机报告写操作的完成情况,流向为从机到主机,无法合并到写数据通道中,另一方面,写回复又是不可或缺的,所以就有了一条独立的写回复通道。

4.AXI4总线的突发传输机制

在手册的术语表中,与 AXI 传输相关的有三个概念,分别是 transfer(beat)、burst、transaction。用一句话串联就是:

==在 AXI 传输事务(Transaction)中,数据以突发传输(Burst)的形式组织。一次突发传输中可以包含一至多个数据(Transfer)。每个 transfer 因为使用一个周期,又被称为一拍数据(Beat)==

再展开一层,两个 AXI 组件为了传输一组数据而进行的所有交互称为 AXI Transaction,AXI 传输事务,包括所有 5 个通道上的交互。

AXI 是一个 burst-based 协议,AXI 传输事务中的数据传输以 burst 形式组织,称为 AXI Burst。

每个传输事务包括一至多个 Burst。每个 Burst 中传输一至多个数据,每个数据传输称为 AXI Transfer。我们 通过【深入AXI4总线(一)】[4]了解到,双方握手信号就绪后,每个周期完成一次数据传输,因此 AXI Transfer 又被称为 AXI beat,一拍数据。不严谨地说

- AXI Transaction =M * AXI Burst , M >= 1

- AXI Burst = N * AXI Transfer(AXI beat), N >= 1

5.传输事务结构

1、读写地址结构

在整个传输事务过程中,主机首先将接下来 burst 传输的控制信息以及数据首个字节的地址传输给从机,这个地址被称为起始地址。

在本次 burst 后续传输期间,从机将根据控制信息计算后续数据的地址。

控制信息以及起始地址在读/写地址通道(AWC/ARC)传输。

==注意:单次 burst 传输中的数据,其地址不能跨越 4KB 边界。 关于这点在笔者参考的一个来源这样表示,目前笔者觉得看上去很有道理: 协议中之所以规定一个burst不能跨越4K边界是为了避免一笔burst交易访问两个slave (每个slave的地址空间是4K/1K对齐的) 4K对齐最大原因是系统中定义一个page大小是4K, 而所谓的4K边界是指低12bit为0的地址。==

地址通道中传输的控制信息中包括三项突发传输相关的信号(AR/AW 均一致,下图为以 AR 为例):

(1)突发传输长度(burst length)

指一次突发传输中包含的数据传输(transfer)数量,在协议中使用 AxLen 信号控制。

突发传输长度在不同的模式(burst type ,将在后文中讨论)下有一些限制,包括:

- 对于 WRAP 模式,突发传输长度仅能为2,4,8,16

- 在一次突发传输中,地址不能跨越一个 4KB 分区

- 一次突发传输不能在完成所有数据传输前提前结束(early termination)

协议中多次强调,通信双方都不能在传输事务的所有 Transfer 完成前提前结束。哪怕发生错误,也得含泪走完整个传输事务的流程。

(2)突发传输宽度(burst size)

指传输中的数据位宽,具体地,是每周期传输数据的字节(Byte)数量,在协议中使用 AXSIZE 信号控制。

突发传输数据宽度不能超过数据总线本身的位宽。而当数据总线位宽大于突发传输宽度时,将根据协议的相关规定,将数据在部分数据线上传输。

传输宽度 = 2 ^ AXSIZE(3)突发传输类型(AxBURST)

类型共有 3 种,分别为 FIXED,INCR 以及 WRAP。使用 2 位二进制表示。

FIXED 类型中, burst 中所有数据都使用起始地址。该模式适合对某个固定地址进行多次数据更新,比如读写一个 fifo 时,读写地址就是固定的。

INCR 类型最为常用,后续数据的地址在初始地址的基础上进行递增,递增幅度与传输宽度相同。适合对于 RAM 等通过地址映射(mapped memory)的存储介质进行读写操作。

WRAP 类型比较特殊,首先根据起始地址得到绕回边界地址(wrap boundary)与最高地址。当前地址小于最高地址时,WRAP 与 INCR 类型完全相同,地址递增。但到递增后的地址到达最高地址后,地址直接回到绕回边界地址,再进行递增,就这样循环往复。

2、读写数据结构

在 AXI 数据传输过程中,主要涉及到

- 窄位宽数据传输(Narrow Transfer)

- 非对齐传输(Unaligned Transfer)

- 混合大小端传输(mix-endianness)等问题。

(1)窄位宽数据传输

当本次传输中数据位宽小于通道本身的数据位宽时,称为窄位宽数据传输,或者直接翻译成窄传输。

在窄位宽写传输中,主机需要告知从机数据通道中哪些bit(原文写的是字节,应该是写错了)是有效的,需要使用到写数据通道中的 WSTRB 信号。WSTRB 信号中的单个 bit 置起,表示对应位置上的字节有效,对应关系为:

WSTRB[n] 对应 WDATA[8n+7:8n],也就是:当 WSTRB[n] 为 1 时,WDATA[8n+7:8n]有效。

WSTRB 信号比特位宽等于数据通道位宽的字节数量,比如 32bit 位宽的数据通道,对应 WSTRB 信号位宽为 4bit。

根据该图可直观的看出WSTRB信号的作用。上图的窄位宽传输有以下特点:

- burst 传输长度为 5

- burst 传输位宽为 8bit

- 起始地址为 0x0

- 数据总线位宽为 32bit

- 突发类型为 INCR

引用部分可帮助理解窄位宽传输的情况:

个人理解该设计的意义在于,当主机是因为从机或者其他客观条件限制,需要进行窄传输时,可以一次性将数据放置于数据总线上,只需在每次传输期间改变 WSTRB 信号即可。

以上图为例,主机将 D[31:0] 防置于总线,在接下来的四个周期中,仅需对 WSTRB 进行移位,即可依次完成 4 个字节的传输。

该结构有利于 memory 类型的从机进行写入处理,这里设想一种实现方式,结合下图讲解,在 64bit 位宽的总线上进行 32bit 位宽传输,起始地址为 0x4 。此时假设存储介质位宽与总线位宽一致,为 64 bit。

在 transfer 1st 中,从机获取整个总线上的 64bit 数据存储至存储介质中,比如 DDR,并利用 wstrb 作为 mask 信号屏蔽无效的低 32 bit(比如 DDR 的 DQM 信号)。

这时候存储介质的写入地址为 0x0,但实际只从地址 0x4 开始写入了 32bit 数据。在后续的 transfer 继续按以上模式工作。

6.AXI outstanding

1.什么是outstanding?

从字面理解,outstanding表示正在进行中的,未完成的意思,形象地说就是“在路上”。

比如现在需要传输一段数据,假设没有outstanding,必须等到地址握手成功才能传输数据,而每一次握手过程中都不能保证主从机此刻都准备好,那这样在数据传输过程中就难免会有气泡,难以实现真正的全流水和满性能。

所以从设计的角度,我们就有多发几个地址的需求,比如我们可以发出去10个地址,尽管我们还没给数据,但是可以让从机知道,我们接下来要向这些地址写数据,这样就可以不用刻板地遵循,每次都要写地址握手成功再写数据。

所以在这个例子中,outstanding就是发出去的地址数量,未处理的地址可以先存放在AXI总线的缓存里,等完成一次传输事物之后,无需再握手传输地址,即可立即进行下一次的数据传输,所以outstanding本质上是为了实现数据传输的pipeline。

简单讲,如果没有outstanding,或者说outstanding能力为1,则总线Master的行为如下(AHB总线就没有outstanding能力):

- 1)读操作:读地址命令 -> 等待读数据返回 -> 读地址命令 -> 等待读数据返回 -> 。。。。。

- 2)写操作:写地址命令->写数据->等待写响应返回->写地址命令->写数据->等待写响应返回。。。。。

而如果outstanding能力为N>1的话,则:

- 1)读操作:可以连续发N个读地址命令,这期间如果读数据没有返回,则需要等待读数据返回,如果有读数据返回,则返回了几个,那么仍然可以接着发几个。也就是说,“在路上” 的读命令(或者读数据)最多可以是N。 多说一点,可以看出,如果数据返回得比较慢,那么IP需要等待,效率就会比较低,因此,为了提高效率,有必要提高outstanding能力,以弥补”路上“(总线)引入的延时。但是也不能无限制地发,否则有可能会引起总线拥塞,把其他IP给堵住。

2.如何计算outstanding?

首先,对于AXI而言,outstanding能力分为读outstanding能力和写outstanding能力。

如何计算outstanding能力呢?

首先对一些概念进行类比:

- burst传输的长度为一列高铁的节数,8节高铁对应的burst length=8。

- 一节高铁载的乘客数就是AXI的数据位宽,常见的AXI的数据位宽有64bit,128bit等等。

- 高铁的速度就是AXI总线的时钟频率,好比AXI的频率有的是200MHz,有的是300MHz。

- 从高铁站触发,到终点的线路长度就是AXI的总线延迟,即AXI的Master 到Slave的延迟拍数(Clock Cycle)固定了,一节高铁可以等效为AXI的一个Cycle。

类比之后,以一段高铁线路为例,起点为A,终点为B,从A到B的高铁线路如果要达到最高效率,需要在线路上排满高铁,首尾相接。那么需要多少列高铁才能达到最大效率呢?

假设需要X列高铁,(1列有N节)

X=(高铁线路总长度*2)/(N节高铁的长度),所以X可变换为((高铁线路总长度/1节高铁长度)* 2)/N,其中(高铁线路总长度/1节高铁长度)为高铁总节数,因为一节高铁对应一个AXI的cycle,所以高铁总节数对应该线路的延迟Cycle总数。

X=线路延迟Cycle数目*2/N,X即为AXI outstanding,其中线路延迟Cycle数目* 2为Round Trip Latency(cycle)(往返总延迟),N为burst length。

(补充:最大传输带宽=AXI Clock Frequency x AXI Data Width)

7.乱序传输

AXI的控制和数据通道分离,可以带来很多好处。地址和控制信息相对数据的相位独立,可以先发地址,然后再是数据,这样自然而然的支持显著操作,也就是 outstanding 操作。

Master访问slave的时候,可以不等需要的操作完成,就发出下一个操作。这样,可以让slave在控制流的处理上流水起来,达到提速的作 用。

同时对于master,也许需要对不同的地址和slave就行访问,所以可以对不同的slave 连续操作。而这样的操作,由于slave 返回数据的先后可能不按照master 发出控制的先后进行,导致出现了乱序操作(out of order )。

乱序传输需要依赖ARID来完成,乱序传输是针对transaction而言的,可以认为ARID是transaction的ID。

若支持乱序传输,当存在多个transaction时,从机可以不按照transaction的发起顺序进行返回数据,主机通过从机返回的BID(写)或RID(读)来判断返回的数据属于哪个transaction。

另外,拥有相同AWID与ARID的transaction, 其返回数据需要按照transaction发起的顺序进行返回数据。乱序传输的数据传输过程如下图所示:

8.interleaving 交织

写交织使用WID来实现,interleaving用来实现不同transaction中的beat的交替传输,但同一transaction的beat是需要按照顺序进行传输的。

AXI4中已经取消了WID信号的使用,不再支持写交织。interleaving的输出传输过程如下:

其中数据0与数据1属于同一transaction的不同beat,地址A与地址B表示两个transaction。

关于AXI4不支持写交织是一个非常自然地过程。为了提高效率,AXI总线的写数据通道并不依赖写地址通道,这就是说,写数据可以先于写地址发送,但是总线不知道写地址,没办法将数据发送出去,只能暂存在buffer中,等待写地址。比较理想的方案是总线为每个master预留一个写地址通道buffer和写数据通道buffer。

在这种方案下,若支持写交织,地址通道buffer和数据通道buffer的数据可能永远都对不上(AWID与WID),这会造成该master的所有数据都被堵塞。当然可以采用其他方案来解决这个问题,比如说为每个master分配多个buffer,但实现起来会比较复杂。

合理地设计可以减少写交织被取消带来的影响,master应该在某个transaction的数据准备好之后再向总线发起写请求,否则mater可能长时间占用总线,大大降低总线的效率。因此,设计人员本就应该避免写交织十分高效时的场景,设计合理的情况下,写交织的取消并不会给系统带来明显的效率影响。

9.参考资料

- https://zhuanlan.zhihu.com/p/560467196?utm_id=0

- https://blog.csdn.net/qq_35396239/article/details/1239451https://blog.csdn.net/tbzj_2000/article/details/88042890

- https://zhuanlan.zhihu.com/p/45122977

- https://blog.csdn.net/weixin_42790063/article/details/124867702

- https://zhuanlan.zhihu.com/p/642670753?utm_id=0

References

[3] 【关于总线的学习(一):入门篇】

[4] 【深入AXI4总线(一)】

作者:Hcoco

文章来源:TrustZone

推荐阅读

更多Arm AMBA 协议集技术干货请关注Arm AMBA 协议集技术专栏。

迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。