NVME

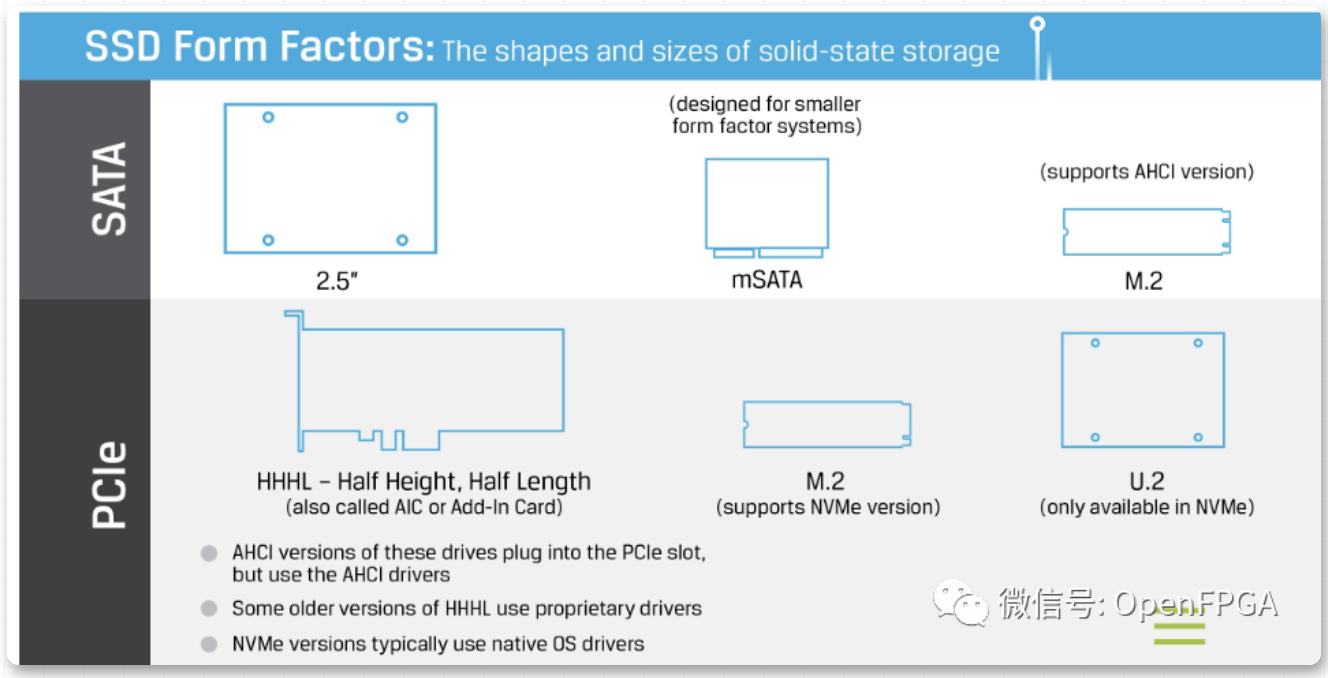

NVM Express ( NVMe ) 或 Non-Volatile Memory Host Controller Interface Specification( NVMHCIS ) 是一种开放式逻辑设备接口规范,用于访问通过PCI Express总线连接的计算机非易失性存储介质。NVM 的缩写代表非易失性存储器,通常是 NAND 闪存,具有多种物理外形,包括固态驱动器(SSD)、PCIe 附加卡和M.2( mSATA的后继者 )。

从架构上讲,NVMe 逻辑物理存储在 NVMe 控制器芯片内并由该芯片执行,该芯片与存储介质(通常是 SSD)物理位于同一位置。NVMe 的版本更改(例如 1.3 到 1.4)已合并到存储介质中,并且不会影响主板、CPU 等 PCIe 借口兼容组件。

SATA和NVME外形区别 图片来源:金士顿官网

FPGA实现NVME

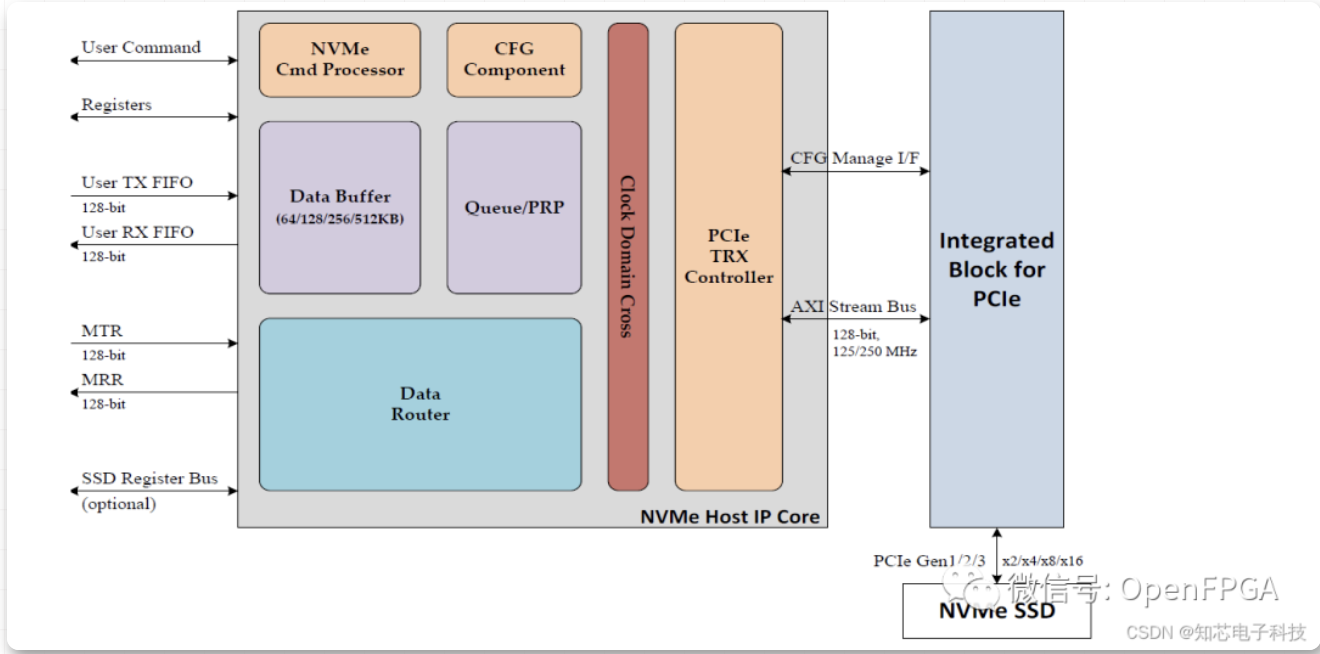

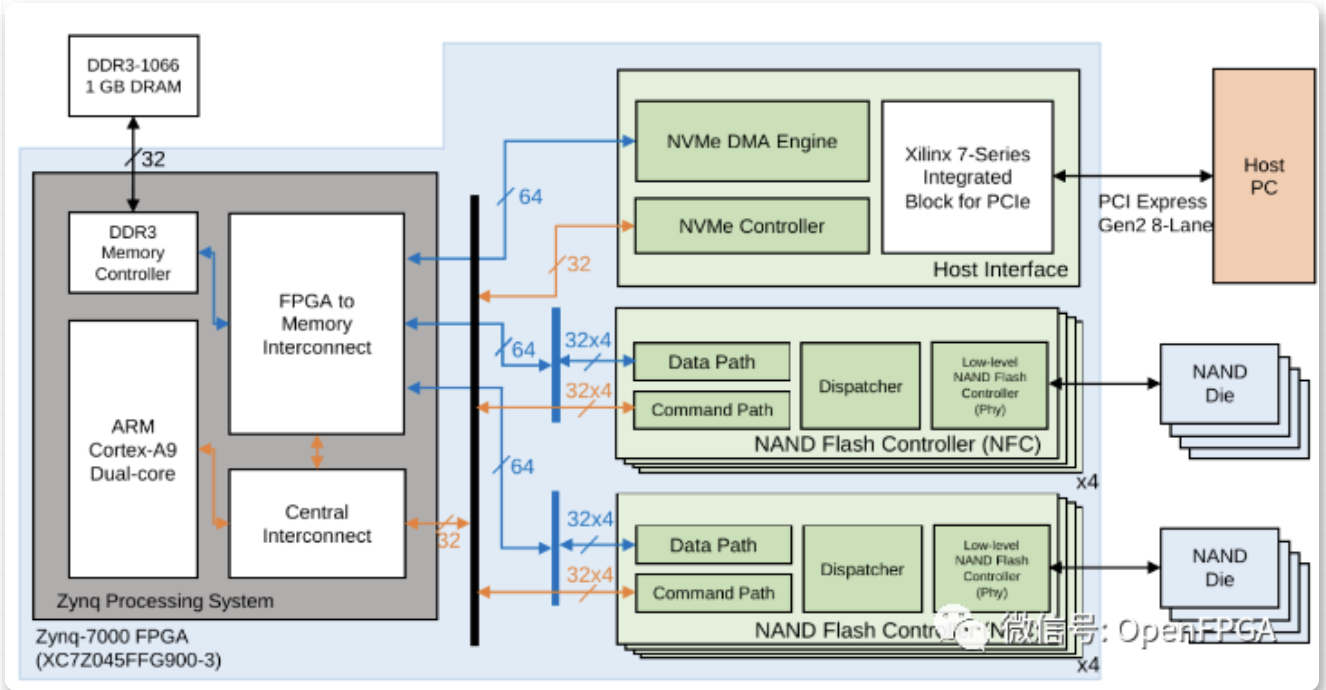

NVMe协议基于PCIe协议之上实现NVMe Host与NVMe SSD之间高速数据通信。FPGA实现的简单架构如下:

FPGA实现NVME控制(图片来源见水印)

下面介绍几个NVME协议的实现的开源项目。

OpenSSD+nvme storage

介绍

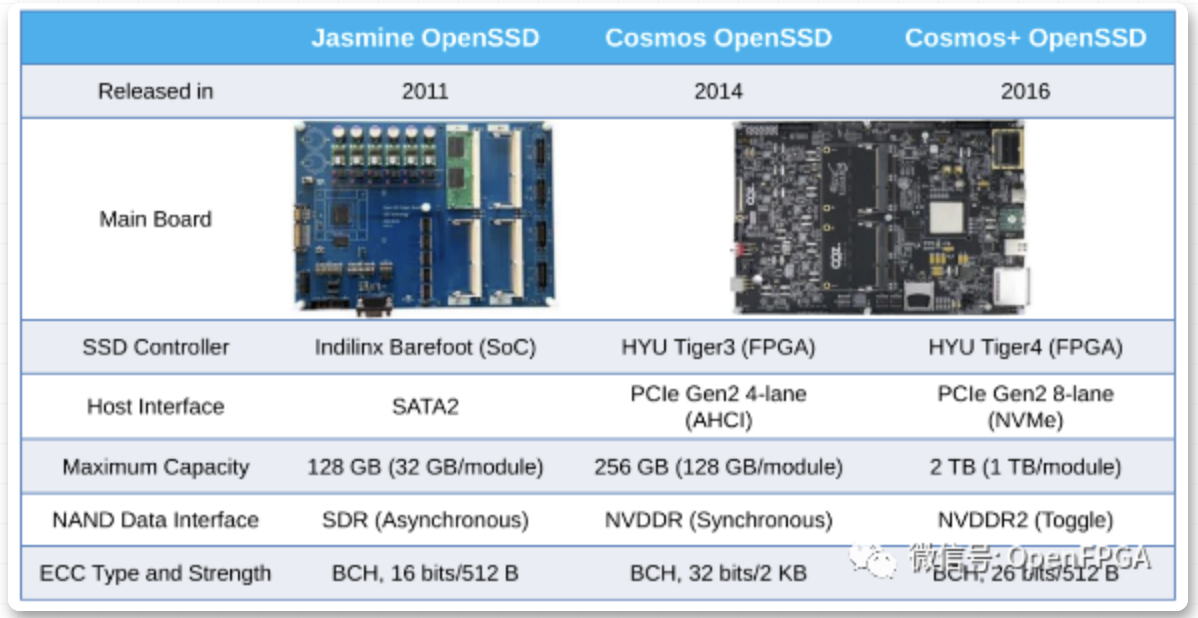

OpenSSD的发展历史如下:

nvme_comp_storage项目是基于OpenSSD的存储系统,详细的架构如下:

两个项目都有异常详细的文档介绍,链接如下:

❝

https://github.com/Cosmos-OpenSSD/Cosmos-plus-OpenSSD/tree/master/doc

❞❝ https://github.com/giuseppedongiovanni/nvme_comp_storage/blob/master/Project_Documentation.pdf

❞

其中OpenSSD是有官方网址的,截止发文前,官网访问受限~

antmicro for nvme

该项目和上面项目类似,唯一的区别就是该项目从底层PCIe到顶层所有的代码都是自己写的(在PCIe项目中有介绍),不想借助官方IP的项目,这个项目很具有借鉴意义。

该项目介绍的非常项目,就不赘述了。

NVMe

❝

https://github.com/mcrl/NVMe

❞

介绍

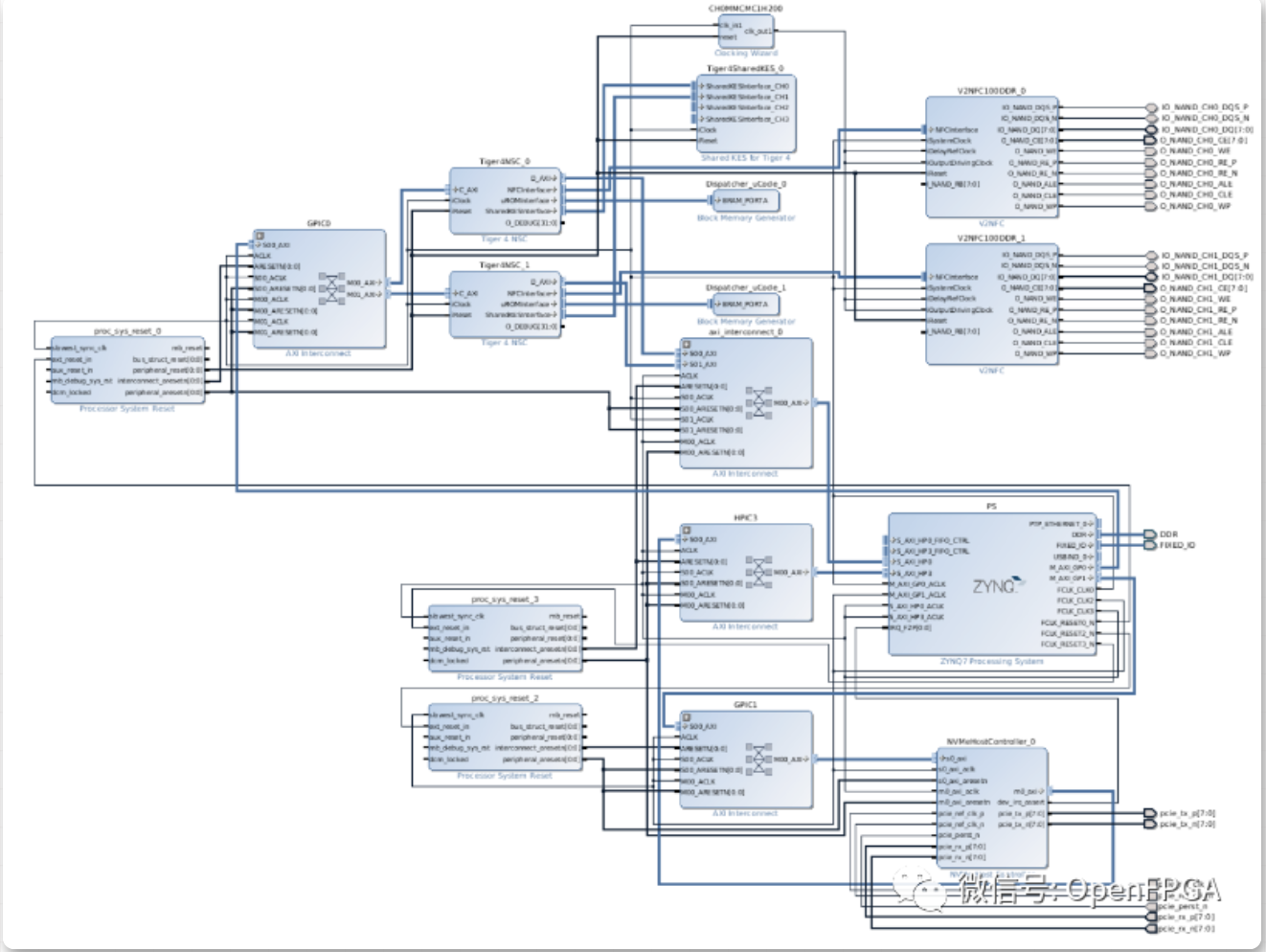

本项目基于AMD-XILINX FPGA XDMA的NVME控制器,详细的文件架构如下:

NVMe/

├── hw/ (RTL codes)

│ ├── COMSTRAINTS/ (Constraints : Board connections)

│ ├── IP/ (IPs : ILA, XDMA IP, Board design)

│ ├── RTL/ (NVMe Hardware Driver RTL codes)

│ ├── scripts/

│ ├── SIM/

│ └── SYNTH/ (NVMe Hardware Driver Project directories)

├── sw/ (NVMe suFile Library)

├── SIM/

├── README.md

├── LICENSE

└── CMakeLists.txt

具有硬件加速功能的 NVMe 控制器

❝

https://github.com/FDU-ME-ARC/NVMeCHA

❞

介绍

NVMeCHA 是一款超低延迟和高吞吐量的 NVMe 控制器,具有高度并行、流水线和可扩展的架构,具有一个管理控制器和多个完全硬件自动化的 I/O 控制器。管理控制器采用软硬件协同设计,其中 NVMe 管理命令的复杂处理由软件管理,而 PCIe 上的数据传输由硬件处理。这种混合架构结合了软件灵活性和硬件效率,减少了 CPU 资源并提高性能。I/O控制器采用高度并行和流水线的硬件架构设计,允许并行处理许多NVMe I/O命令,而无需任何软件干预。每个I/O控制器对应一个NVMe I/O队列对。

该项目在 Xilinx KCU105 FPGA 板上进行验证,该板通过 PCIe gen3 x8 接口连接到计算机。通过SPDK-Perf基准测试工具进行评估,该NVMe控制器的最大读写带宽均可达到7.0GB/s,占理论PCIe带宽的89%。最大4KB大小的读/写吞吐量可以达到每秒170万次I/O操作(MIOPS)。4KB大小的平均读/写延迟仅为2.4μs/3.2μs。

该项目也进行论文发表: IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems,doi:10.1109/TCAD.2021.3088784。

pl-nvme

介绍

这个项目也和上面项目类似,不过性能没有上面的架构强。

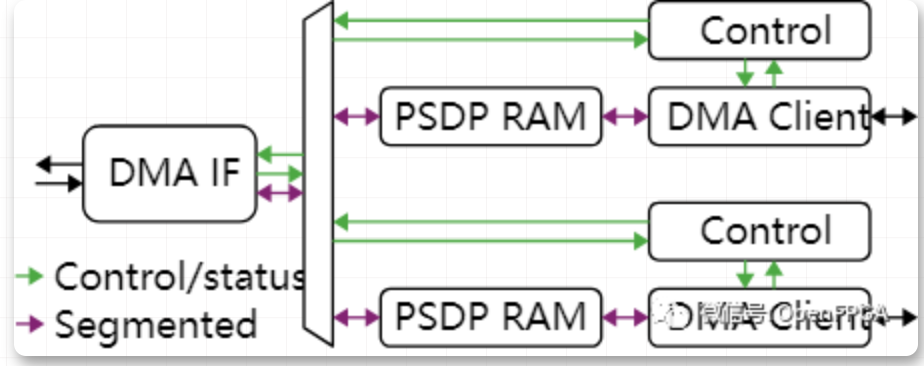

该项目包含 Dune NvmeStorage 系统的源代码以及简单的NVMe测试环境,允许使用低级Xilinx FPGA进行接口验证。

包含FPGA源代码、仿真环境或 Nvme 测试 FPGA 固件以及 nvme_test 主机软件。

总结

NVME部分因为基本和FPGA PCIe息息相关,所以基本和PCIe项目同时出现,对于想从底层开始实现的,强烈建议 antmicro 项目。

最后,还是感谢各个大佬开源的项目,让我们受益匪浅。后面有什么感兴趣方面的项目,大家可以在后台留言或者加微信留言,今天就到这,我是爆肝的碎碎思,期待下期文章与你相见。

原文:OpenFPGA

作者:碎碎思

相关文章推荐

更多FPGA干货请关注FPGA的逻辑技术专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。