1.为什么需要debug时钟频率

在芯片设计中,为了便于定位故障,有时候需要确认部分时钟频率是否正确,需要部分debug手段。常见的方式是:将时钟信号引到芯片管脚,通过仪器测量。这类方式必须要测量仪器,并且需要熟练使用,耗时较长。还有一种简单的方式,通过时钟计数的方式判断时钟频率是否正确。

2.Debug时钟频率原理

本文以serdes用户侧并行接口的恢复时钟为例,说明一下如何判断serdes恢复时钟频率是否正常。

本文以host_clk(100MHz)时钟为基准时钟,进行判断。host_clk为100MHz,以serdes_clk为830.078125MHz进行分析

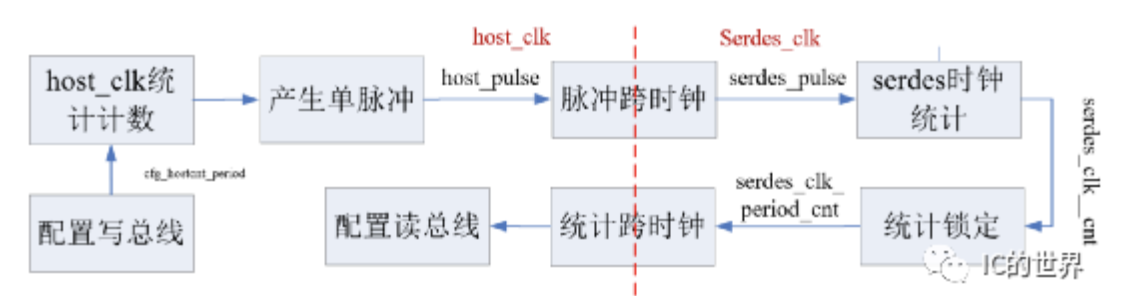

配置cfg_host_cnt_period为10000(10进制),则在10000个host_clk周期里,serdes_clk应该跳变了8300781次。首先在host_clk时钟域下,存在递增循环计数host_clk_cnt,host_clk_cnt在0~cfg_hostcnt_period-1范围内递增,不断循环。在serdes_clk时钟域下,存在计数serdes_clk_cnt,serdes_clk_cnt不断递增,直到存在有效脉冲serdes_pulse则清零。

每次host_clk_cnt计数到cfg_hostcnt_period-1,则产生一个有效脉冲host_pulse。host_pulse通过脉冲跨时钟模块输出serdes_pulse。serdes_pulse下一个周期将serdes_clk_cnt清零,并且将serdes_clk_cnt当前值锁存到serdes_clk_period_cnt,serdes_clk_period_cnt通过跨时钟模块同步到host_clk时钟域并且送到host_clk下的配置读总线(配置读写总线通常是一个模块)。

此方法的精度虽然有限,但是却能很方便地判断时钟频率是否稳定,能够判断目标时钟频率范围。

作者:IC小鸽

文章来源:IC的世界

推荐阅读

- IC设计:接口X态隔离设计

- IC设计思维01_复用思维:增加复用性的6种方法

- IC设计:一种IP控制信号的处理方式

- 4种常见的流控机制(三) 以太网MAC的pause流控

- 4种常见的流控机制(二)主动管理的流控

更多IC设计干货请关注IC设计专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。