IP一般指IP核,是芯片中具有独立功能的电路模块的成熟设计。该电路模块设计可以应用在包含该电路模块的其他芯片设计项目中,从而减少设计工作量,缩短设计周期,提高芯片设计的成功率。该电路模块的成熟设计凝聚着设计者的智慧,体现了设计者的知识产权,因此,芯片行业就用IP核(Intellectual Property Core)来表示这种电路模块的成熟设计。IP核也可以理解为芯片设计的中间构件。

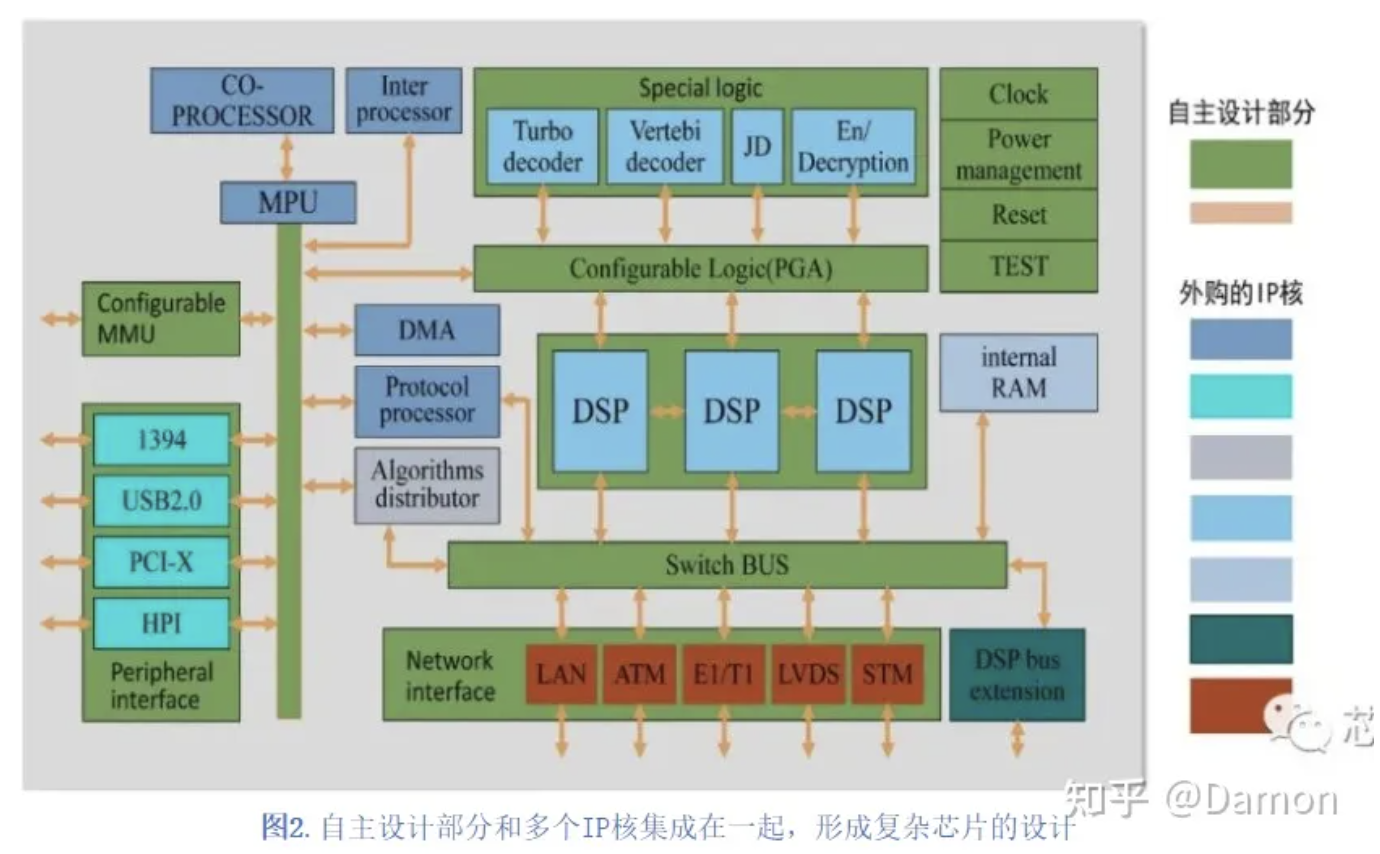

一般说来,一个复杂的芯片是由芯片设计者自主设计的电路部分和多个外购的IP核连接构成的。如图所示,要设计这样结构的一款芯片,设计公司可以外购芯片中所有的IP核(不同颜色模块),仅设计芯片中自己有创意的、自主设计的部分(用绿色表示),并把各部分连接起来。

图中的芯片设计过程就像下图的系统电路板开发过程一样,是用已有的IP核(或者芯片)进行布局、摆放和信号连接的过程,这种过程可以称为对IP核(或者芯片)的复用。不同的是,系统电路板上除了芯片和连接线之外,系统开发者很少自主开发自己的芯片。而在芯片设计过程中,芯片上除了采用外购的IP核之外,一般说来,芯片设计者还要设计一部分自己的电路,并完成各部分之间的信号连线,最后还要对整个芯片的功能、性能进行制造前的反复检查和验证。

芯片设计需要考量IP核的许多参数和指标,并要把各个IP核和自主设计部分正确连接,保证整个芯片的功能和性能正确无误。

IP核被其他芯片设计公司采用,行业内称为IP复用。专门设计相对独立电路功能模块,目的是推广给其他芯片设计公司进行复用,这种设计工作称为IP开发。专门从事IP开发的公司称为IP厂商,或者IP提供商。IP厂商把IP销售给芯片设计公司是一种IP交易行为。

IP的作用主要有四个方面,一是使芯片设计化繁为简,缩短芯片设计周期,提高复杂芯片设计的成功率。二是IP开发和IP复用技术使小公司设计大芯片成为可能;三是使系统整机企业可以设计自己的芯片,提升自主创新能力和整机系统的自主知识产权含量;四是使芯片设计行业摆脱传统IDM模式,成为产业链上独立的行业,促进了芯片设计业迅猛发展。

IP的种类和举例

IP核有行为(Behavior)级、结构(Structure)级和物理(Physical)级三个层次的分类,对应着三个种类型的IP核,它们是由硬件描述语言设计的软核(Soft IP Core)、完成结构描述的固核(Firm IP Core)和基于物理描述并经过工艺验证的硬核(Hard IP Core)。

1.IP软核:它是用硬件描述语言(HDL)设计的独立功能的电路模块。从芯片设计程度来看,它只经过了RTL级设计优化和功能验证,通常是以HDL文本形式提交给用户。所以它不包含任何物理实现信息,因此,IP软核与制造工艺无关。

用户购买了IP软核后,可以综合出正确的门电路级设计网表,并可以进行后续的结构设计,具有很大的灵活性。借助于EDA综合工具,用户可以很容易与其它IP软核,以及自主设计的电路部分合成一体,并根据各种不同半导体工艺,设计成具有不同性能的芯片。

2.IP固核:它的设计程度介于IP软核和IP硬核之间,它除了完成IP软核所有的设计外,还完成了门级电路综合和时序仿真等设计环节。一般地,它以门级电路网表的形式提供给用户。

3.IP硬核:它提供了电路设计最后阶段掩模级的电路模块。它以最终完成的布局布线网表形式提供给用户。IP硬核既具有结果的可预见性,也可以针对特定工艺或特定IP提供商进行功耗和尺寸的优化。

三种类型的IP核是电路功能模块设计在不同设计阶段的产物

用户经过精心评测和选择,购买了IP厂商的IP核后,开始设计自己的芯片。一个复杂芯片一般由购买的IP核和用户自主设计的电路部分组成。芯片设计过程包括了行为级、结构级和物理级三个阶段。行为级和结构级设计阶段的工作一般称为前端设计,物理级设计阶段的工作一般称为后端设计。图6的示意图说明,不同类型的IP核是在不同的设计阶段中加入到整个芯片设计中去。

三种类型的IP核各有优缺点,用户会根据自己的实际需要来选择。以下是三种IP核的优缺点简要总结。

IP软核:它以综合源代码的形式交付给用户,其优点是源代码灵活,在功能一级可以重新配置,可以灵活选择目标制造工艺。灵活性高、可移植性强,允许用户自配置。其缺点是对电路功能模块的预测性较差,在后续设计中存在发生错误的可能性,有一定的设计风险。并且IP软核的知识产权保护难度较大。

IP固核:它的灵活性和成功率介于IP软核和IP硬核之间,是一种折中的类型。和IP软核相比,IP固核的设计灵活性稍差,但在可靠性上有较大提高。目前,IP固核是IP核的主流形式之一。

IP硬核:它的最大优点是确保性能,如速度、功耗等达到预期效果。然而,IP硬核与制造工艺相关,难以转移到新的工艺或者集成到新的结构中去,是不可以重新配置的。IP硬核不许修改的特点使其复用有一定的困难,因此只能用于某些特定应用,使用范围较窄。但IP硬核的知识产权保护最为方便。

IP核的举例,最典型有ARM公司的各种类型的CPU IP核。许多IP供应商提供的DSP IP核、USB IP核、PCI-X IP核、WiFi IP核、以太网IP核、嵌入式存储器IP核等,五花八门,品种十分繁多。

如果按大类分,大体上可分为处理器和微控制器类IP、存储器类IP、外设及接口类IP、模拟和混合电路类IP、通信类IP、图像和媒体类IP等。

全球大的EDA供应商中,有些也是IP供应商。例如美国新思科技(Synopsys)可提供上千种各类IP。涵盖逻辑电路(Logic Libraries)、嵌入式存储器(Embedded Memories)、模拟电路(Analog Libraries)、有线和无线通信接口(Wired and Wireless Interface)、安全(Security)、嵌入式处理器(Embedded Processors) 和子系统(Subsystems)等方面的IP。

IP开发和应用

IP核开发与芯片设计过程比较相似,都需要紧跟芯片技术的发展趋势,不断积累芯片设计技术,了解芯片制造工艺发展步伐。所不同的是,芯片设计公司的商业模式是设计完整的芯片,并推向市场,实现芯片销售利润。而IP开发商不设计完整的芯片,他们只设计芯片局部的某些功能模块,追求这些功能模块(IP核)的设计是最优化的,并要实现IP核在多种复用场合的适应性、便利化。IP开发商谋求这些IP可以被众多芯片设计公司购买采用,并实现IP的销售利润。

但是,IP开发的技术难度和要求很高,并不是任何芯片设计公司想为即可为的事情。这主要体现在,一是IP的完备性要求。IP核作为芯片设计的构件,可以与软件设计的构件(中间件)作比较。软件构件中可以隐藏小瑕疵,集成后的系统软件还可以在投入实际应用时,通过打补丁升级的方式不断完善。但IP核必须非常完善,一点瑕疵都不能有。因为,IP核的任何小瑕疵都有可能影响到整个复杂芯片设计的成败,影响到花费了数百万元甚至上亿元整个芯片研发的投入产出。因此,复杂IP核的售价极为昂贵,从数十万元到上百万元不等。为了便于推广,IP厂商一般采用收取前期IP许可费(IP License)+后期按芯片出货量计算的版权费(Royalty)的商业模式,以降低用户的研发投入。二是IP的多参数需求,包括工艺节点、电源、功耗、性能等。这些都要求IP开发者对芯片设计、制造工艺和行业应用等非常熟悉。三是用户对IP提供商的信誉度要求,包括公司技术实力、影响力和稳定度等。用户很难接受一家规模较小,发展不稳定的IP厂商提供的IP,哪怕这些IP很便宜,甚至免费。用户宁愿购买著名的、大的IP厂商提供的较贵的IP,因为这样的IP才有质量保障和后续服务的保障。

作者:Damon

文章来源:知乎

推荐阅读

IC设计:寄存器写保护的以一种实现方式

systemverilog:logic比reg更有优势

IC设计:RR调度原理

更多IC设计干货请关注IC设计专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。