在systemverilog协议中,logic定义四态值,即向量(vector)的每个位(bit)可以是逻辑0, 1, Z或X,与verilog协议中的reg很接近。但是logic有个很明显的优势,不允许多驱动。

多驱动对关键字logic而言是语法错误,在VCS编译阶段就能够发现,能够更早得发现错误。

而在Verilog协议中,并没有强调reg是不允许多驱的,因此VCS等编译工具不会主动报错。

需要在spyglass lint才能检查出来,或者通过VCS 仿真发现。

在芯片设计中,更早的暴露问题一直是设计和验证人员追求的目标,因此在RTL编码时,如果正常设计是不允许多驱动的场景中,建议使用logic替代reg。

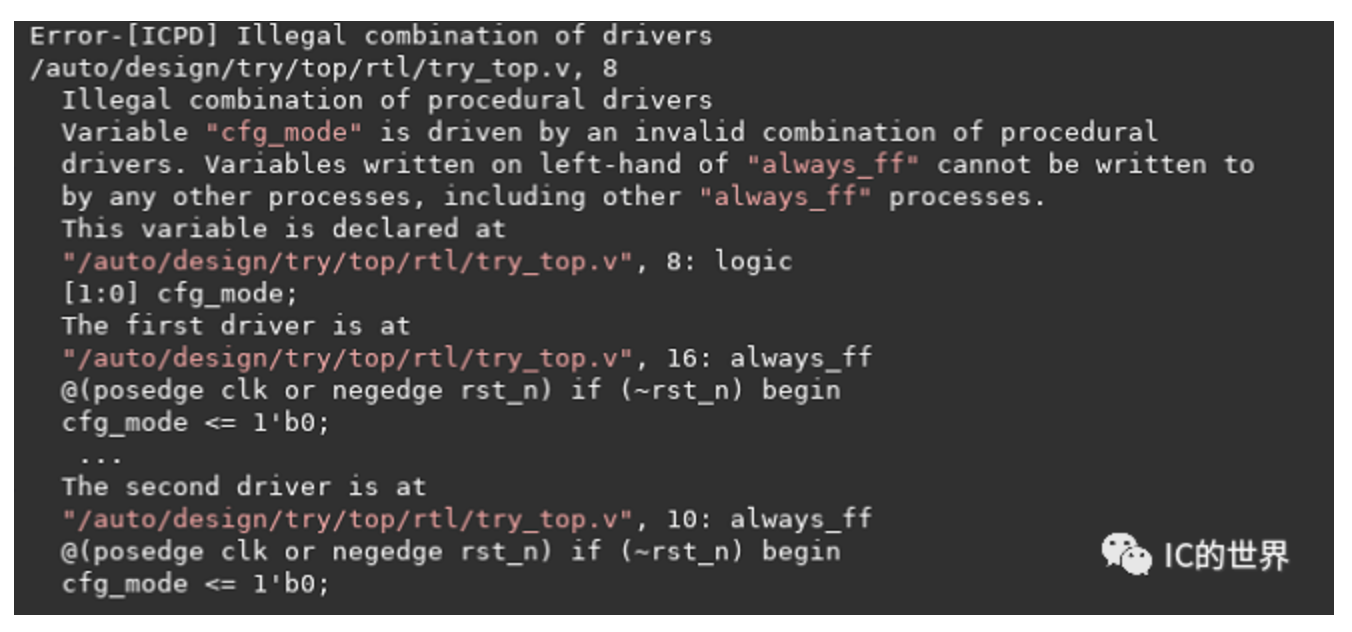

如下案例中:cfg_mode 被多驱动,在实际项目设计中,多驱动的问题往往更加隐蔽,更不容易发现。

module try_top (

input clk , //

input rst_n , //

input [1:0] cfg_mode_in //

);

logic [1:0] cfg_mode ;

always_ff@(posedge clk, negedge rst_n)

if(~rst_n)

cfg_mode <= 1'b0;

else

cfg_mode <= cfg_mode_in;

always_ff@(posedge clk, negedge rst_n)

if(~rst_n)

cfg_mode <= 1'b0;

else

cfg_mode <= cfg_mode_in;

endmodule

VCS报错:

如下案例中:cfg_mode 被多驱动,但是申明成reg类型,因此VCS不会报ERROR。

module try_top (

input clk , //

input rst_n , //

input [1:0] cfg_mode_in //

);

reg [1:0] cfg_mode ;

always@(posedge clk or negedge rst_n)

if(~rst_n)

cfg_mode <= 1'b0;

else

cfg_mode <= cfg_mode_in;

always@(posedge clk or negedge rst_n)

if(~rst_n)

cfg_mode <= 1'b0;

else

cfg_mode <= cfg_mode_in;

endmodule

作者:IC小鸽

文章来源:IC的世界

推荐阅读

更多IC设计干货请关注IC设计专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。