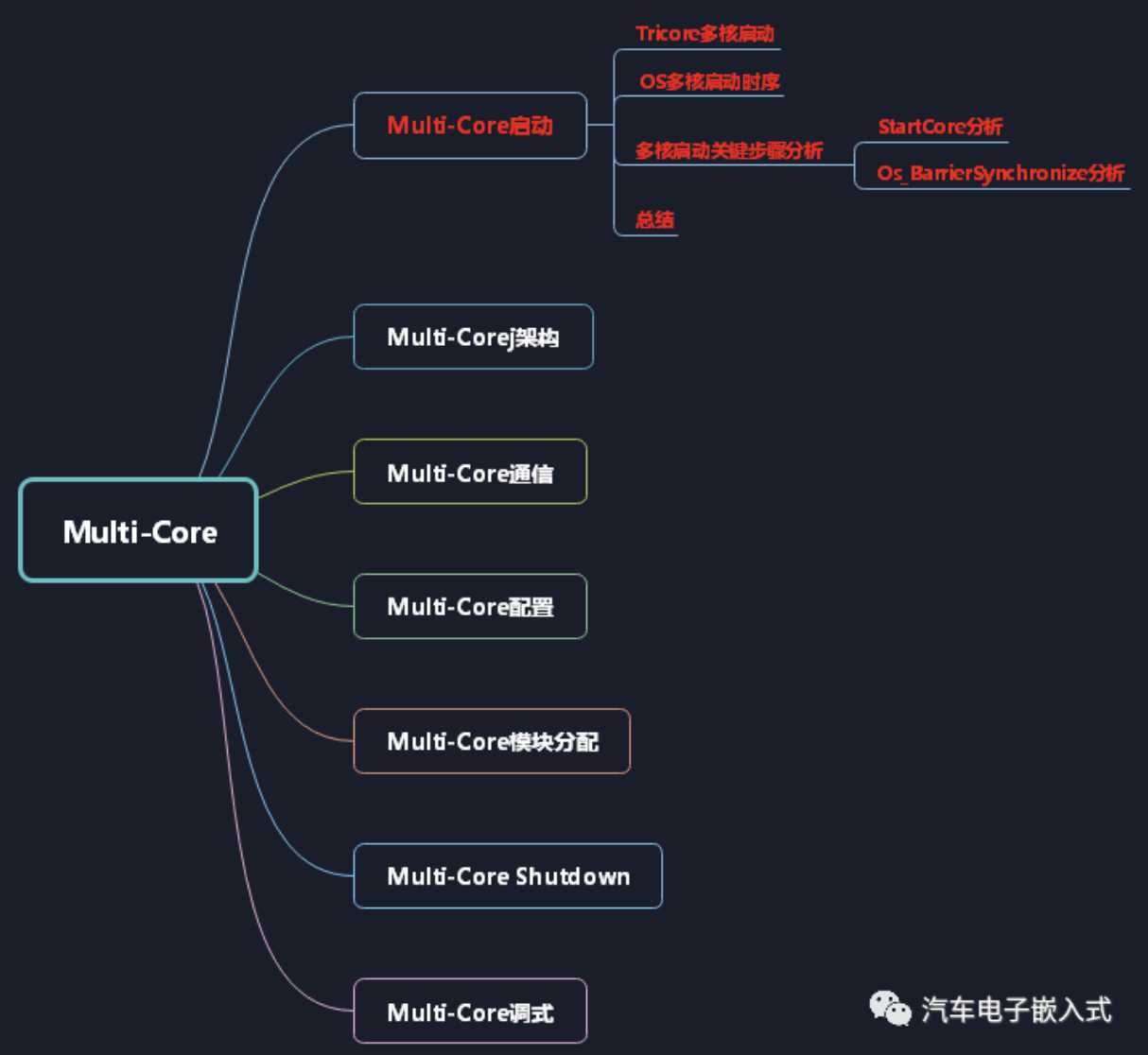

前言

随着汽车ECU迅速的往域控制器方向发展,ECU要出来任务越来越多,单核CPU的负载越来越大,多核ECU势在必行。AUTOSAR架构下OS支持多核处理,本系列文章将详细介绍AUTOSAR架构下的多核机制。本文介绍基于Tricore芯片的AUTOSAR架构下的多核启动。

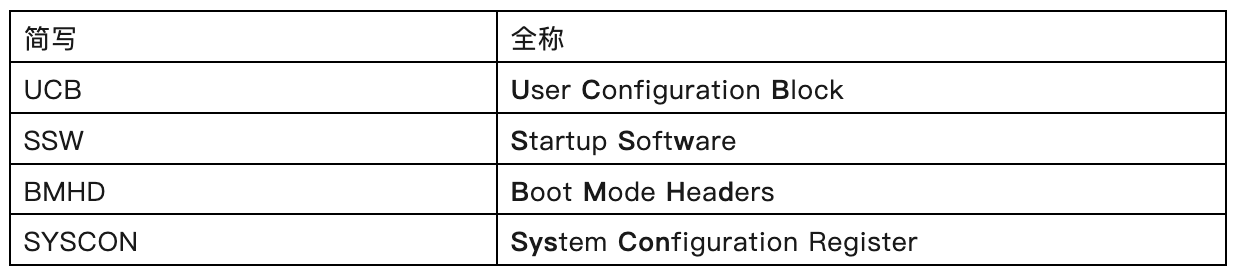

缩略词

参考文档

- TriCoreTM TC1.6.2 core architecture manual

- AURIXTC3XX_um_part1_v2.0.pdf

注:本公众号文章中使用了一些第三方工具和文档,若有侵权,请联系作者删除!

正文

1. Tricore多核启动

背景知识1:UCB_BMHD0_ORIN.STAT的启动地址是配置Tricore启动后SSW从用户程序的哪个地址开始运行,LD链接文件里面的入口地址Entry Point是配置链接器把上电就执行的用户入口代码地址链接到Entry Point,二者应该是同一个地址,也就是说:UCB_BMHD0_ORIN.STAT的启动地址 要等于LD链接文件中的Entry Point启动地址。

参考文档:

Note: 想arm-cotex M4芯片(e.g. S32K144),没有SSW这个固化程序,一上电默认就从0地址启动,所以我们的LD文件需要把我们的Reset_Handler放到0地址处。

参考文档:

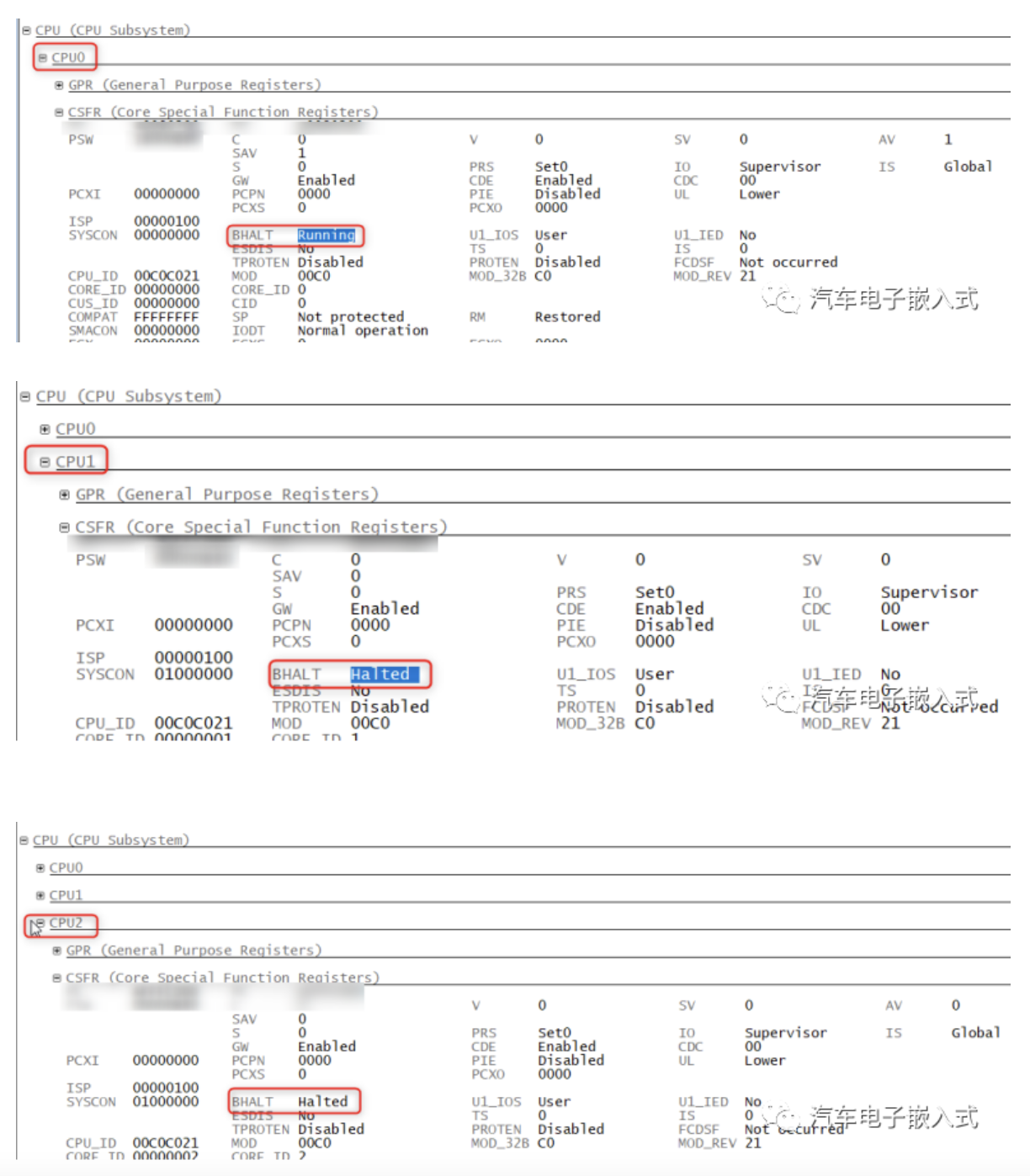

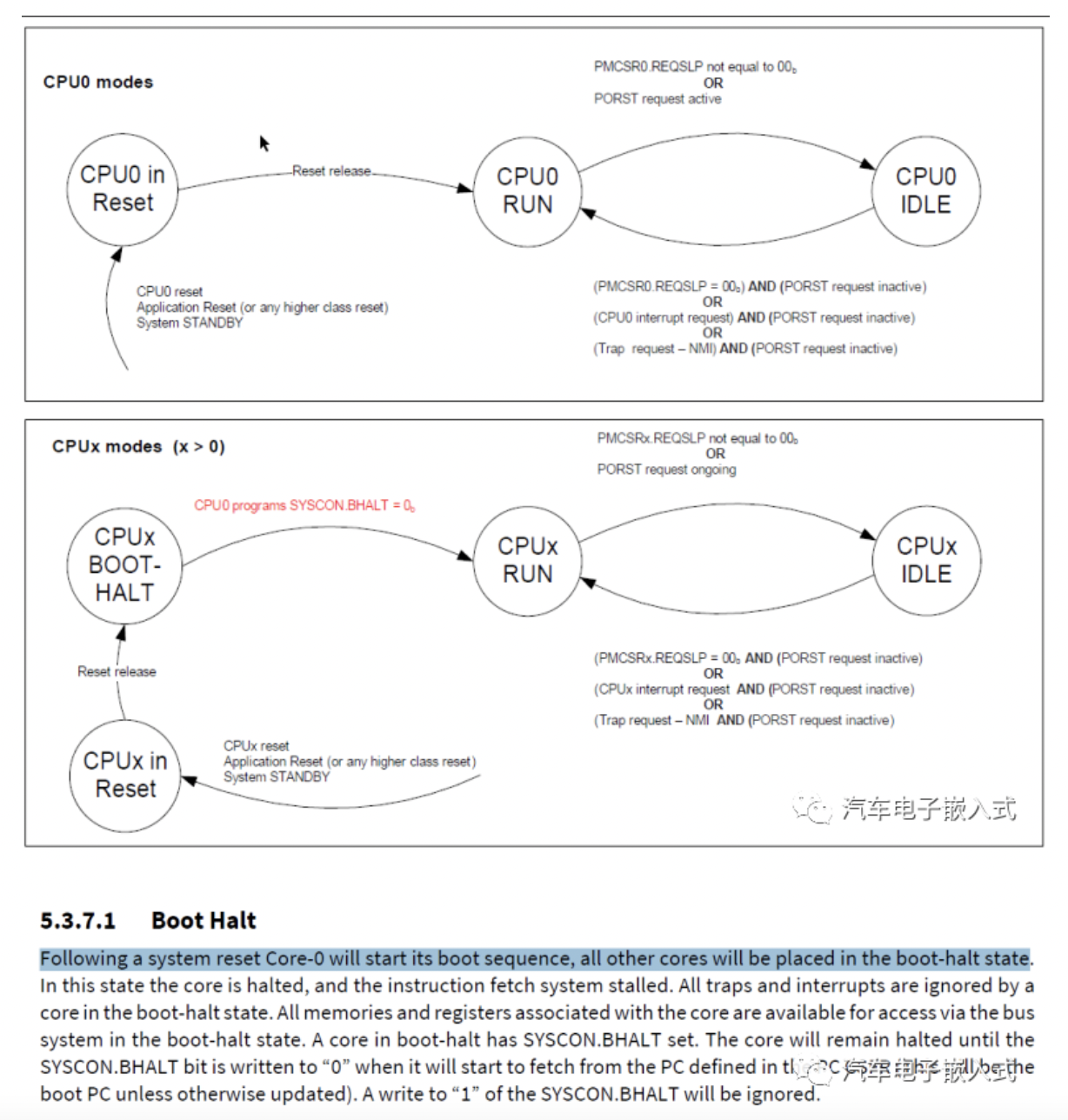

问题1:Tricore是多核ECU,为什么上电后只有Core 0在Runing状态? Core1/2/…是在halt状态?

如下三个图所示,Tricore上电后,CPU0默认进入RUN状态,CPU1和CPU2默认进入halted状态。

如下图所示,Tricore芯片的CPU0(Core0)在上电(Reset)后默认是进入RUN状态的,其他CPUx默认是进入HALT状态的,这是芯片特性。

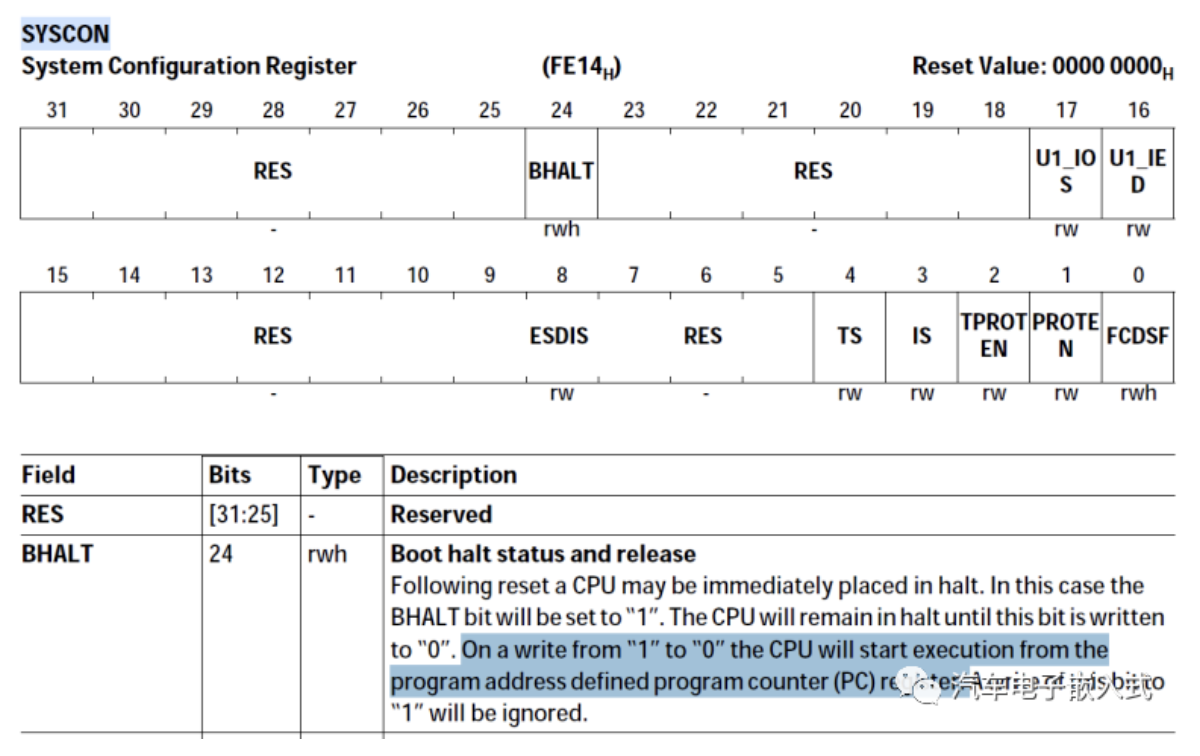

我们可以通过配置SYSCON寄存器的BHALT位\=0b使得CPUx进入RUN状态。

答:这是CPU芯片特性定义的。

背景知识2:我们可以在Core0启动后,通过配置SYSCON寄存器的BHALT位域来启动其他Slave核,在其实Slave核的同时应该配置Slave Core的PC指针到我们想要Slave Core启动的地址处。

2.OS多核启动时序

AUTOSAR架构下, 多核系统分主核(Mater Core,通常也是BSWCore,Tricore芯片下的CPU0)和从核(Slave Core)。系统启动后Master Core自动启动,Slave Core由Master Core启动OS后再通知启动。

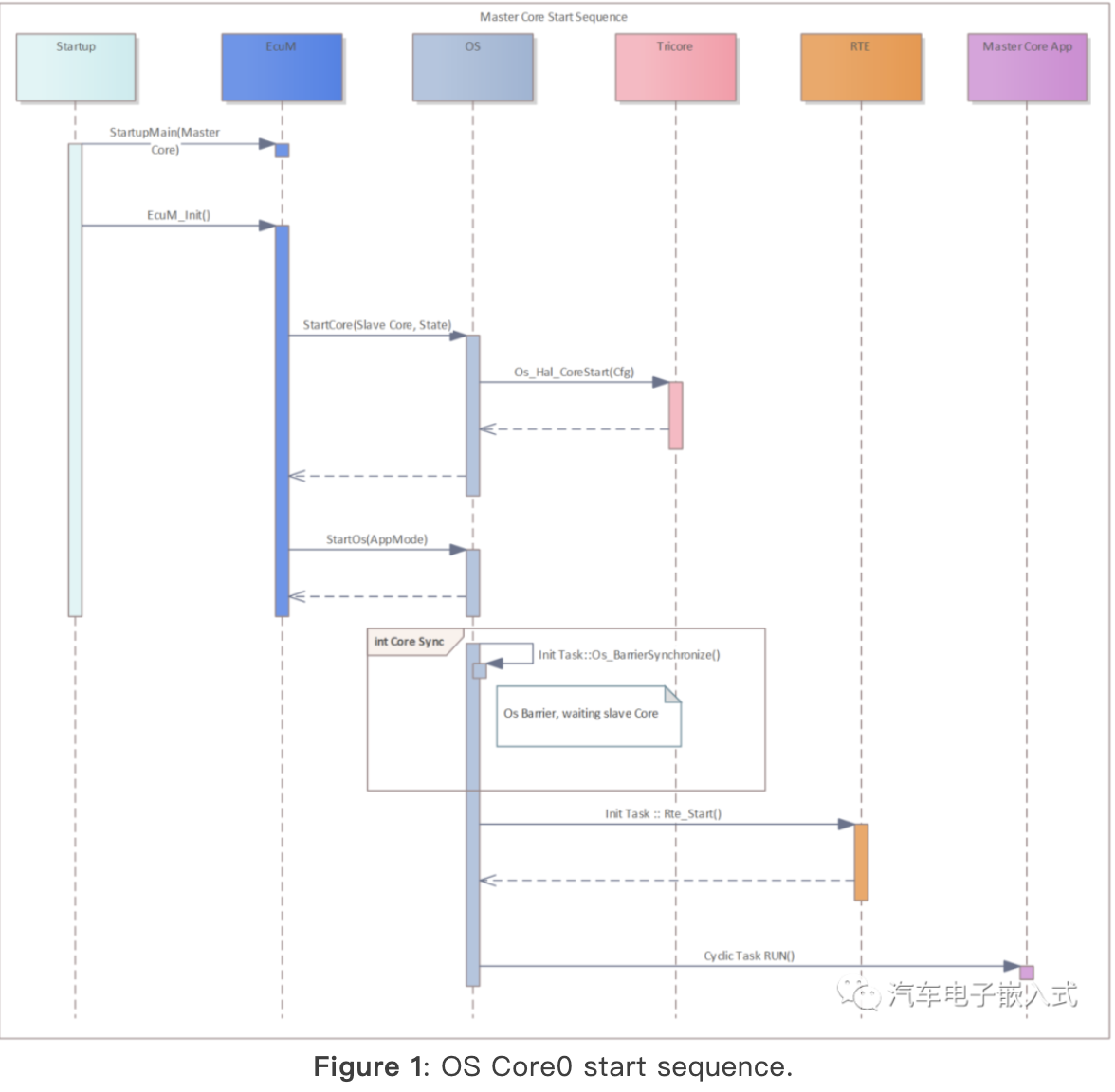

图一为Core0的启动时序,ECU上电后(或者Reset)只有Master Core会Run起来,Master Core的启动代码Startup()会跳转到main()函数,main函数调用EcuM_Init()开始Master Core 0的Start Sequence:

StartCore: 调用Os_Hal_CoreStart启动所有Slave Core.

Os_Hal_CoreStart: 配置芯片寄存器真正启动Slave Core(后文详细分析).

StartOS: 启动OS.

Os_BarrierSynchronize: 开始进行核同步,也就是等待Slave Core运行到这个地方,没有完成核同步钱,Master Core会阻塞在这个地方(后文详细分析OS Barriers机制)。

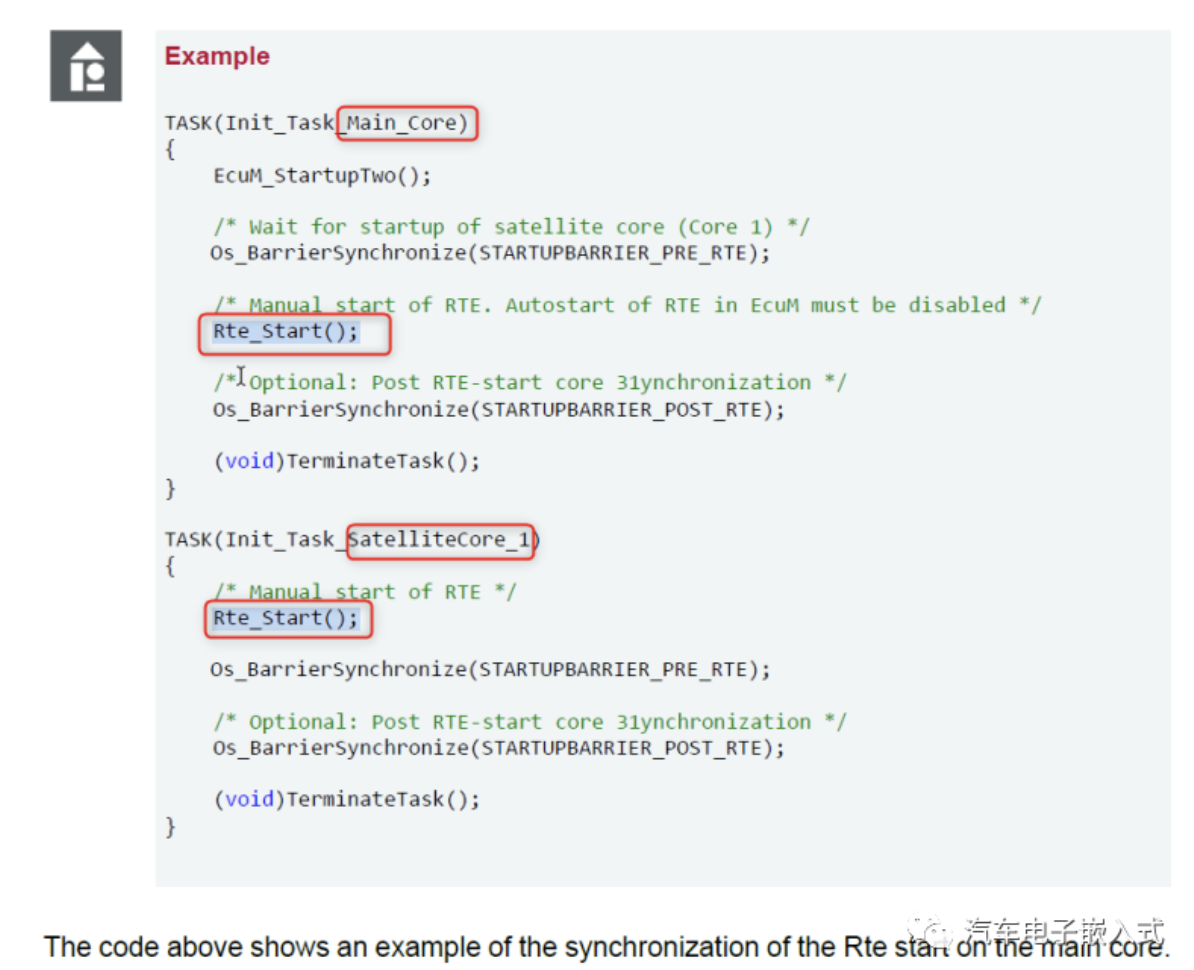

Rte_Start: 完成核同步后,OS调度进入Core0的Init Task,Init Task中调用Rte_Start。

Note:Core0 的Init Task一般不会mapping任何的SWC的Runnable,这样Init Task就需要手动实现(不会由RTE自动生成),在Init Task中就能手写我们想要运行的代码,比如:e.g. 调用Rte_Start().

完成以上的任务后,Core0完成了StartSequence,开始Cyclic Task的调度。

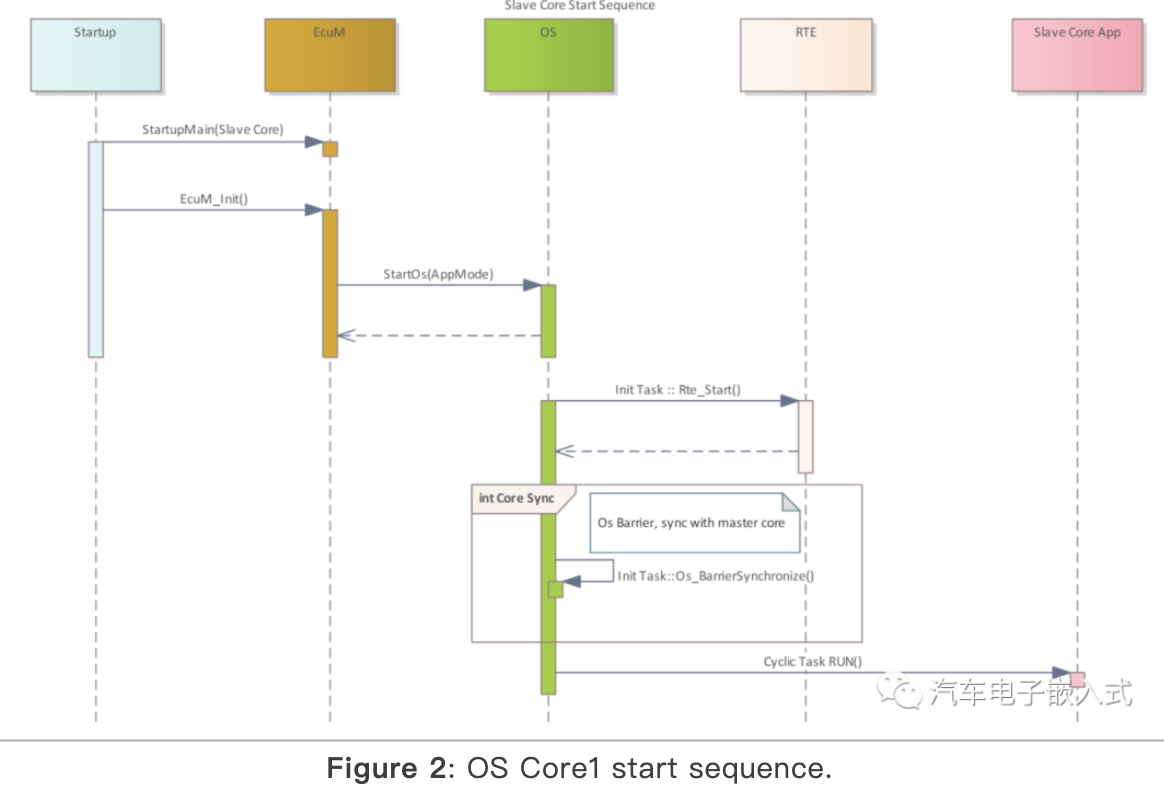

Master Core调用Os_Hal_CoreStart()后,Slave Core就会立刻启动,启动Sequence和Core0基本一样,只不过没有启动Slave的步骤。值得注意的是,Slave Core先调用Rte_Start(),而后再调用Os_BarrierSynchronize().

3.多核启动关键步骤分析

3.1 StartCore分析

StartCore()最后会调用Os_Hal_CoreStart()启动Slave Core, 代码如下所示,最主要的就是

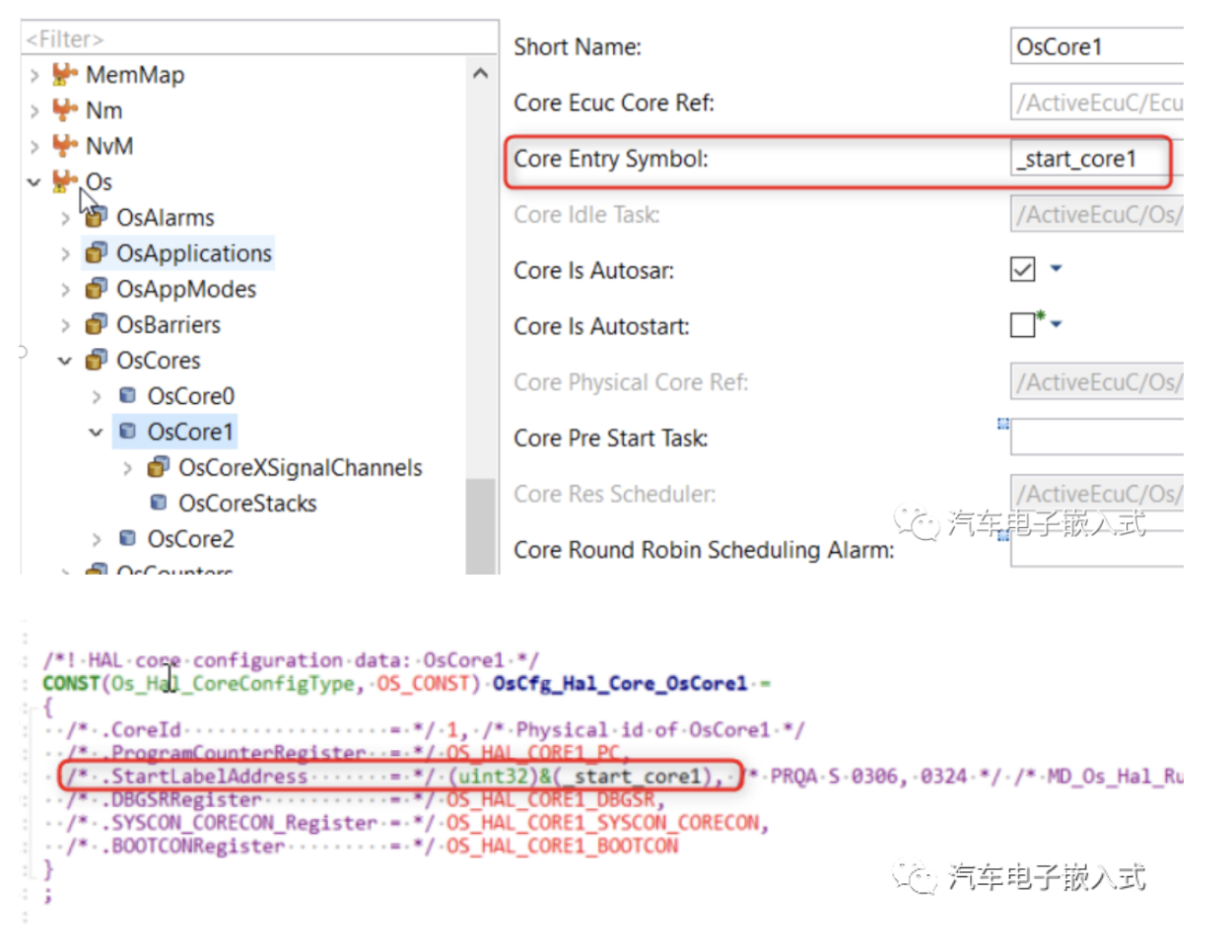

1. 配置PC指针指向Slave Core的启动地址,这个启动地址可以在Davinci工具中配置(_start_core1)。

2. 配置SYCON寄存器控制Slave Core从Halt状态切换到Run状态(SYSCON.BHALT位域写入0)。

OS_FUNC_ATTRIBUTE_DEFINITION(OS_LOCAL_INLINE void, OS_CODE, OS_ALWAYS_INLINE,

Os_Hal_CoreStart,

(

P2CONST(Os_Hal_CoreConfigType, AUTOMATIC, OS_CONST) Core

))

{

/* #10 Write the foreign PC with the startup code symbol for core 1. */

*((volatile uint32*)Core->ProgramCounterRegister) = (uint32)(Core->StartLabelAddress);

/* #20 Reset the core. */

*((volatile uint32*)Core->DBGSRRegister) = OS_HAL_DBGSR_START_CORE;

/* #30 Release the core. */

*((volatile uint32*)Core->SYSCON_CORECON_Register) &= ~OS_HAL_SYSCON_BHALT_MASK;

}3.2 Os_BarrierSynchronize分析

Os_BarrierSynchronize()就是OsBarriers的具体实现,如果一个Barrier被多个Task引用了,那么只有引用这个Barrier的所有Task都调用了Os_BarrierSynchronize(Same BarrierID)后Task才会跳出阻塞状态,这样就能实现核同步。

参考文档:MICROSAR Classic OS Technical Reference.

问题2:为什么要让Slave Core的Rte_Start先调用了?

答:Vector的推荐代码这么写的。

参考文档:How to deal with MICROSAR Multi-Core Projects.

4.总结

a. Tricore芯片Reset后只有Master Core0会进入到Run状态,Slave Cores处于Halt状态。

b. AUTSAR Master Core的OS调用StartCore()启动Slave Core.

c. StartCore()最终调用Os_Hal_CoreStart()配置Tricore芯片的PC指针和SYSCON寄存器启动Slave Core.

d. OS通过OsBarriers机制实现核同步。

END

作者:Tomas Li

文章来源:汽车电子嵌入式

推荐阅读

更多汽车电子干货请关注汽车电子与软件专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。