Perface

- ATE(Auto Test Equipment) 在测试工厂完成. 大致是给芯片的输入管道施加所需的激励信号,同时监测芯片的输出管脚,看其输出信号是否是预期的值。有特定的测试平台。

- SLT(System Level Test) 也是在测试工厂完成,与ATE一起称之为Final Test. SLT位于ATE后面,执行系统软件程序,测试芯片各个模块的功能是否正常。

- EVB(Evaluation Board) 开发板:软件/驱动开发人员使用EVB开发板验证芯片的正确性,进行软件应用开发。

前面我们一起看了SLT,对SLT的应用场景有了一定的认识:芯片测试:系统级测试(SLT)详解

今天来一起看看早有耳闻的ATE,了解一下内部的结构,以及ATE的向量是如何生成与作用的。

文章内容有五个部分:

- ATE/ATS内部结构简介

- IC测试基本原理与ATE测试向量生成

- 基于ATE的IC测试原理、方法及故障分析

- 浅谈基于ATE的IC测试精确度及稳定性问题

- DFT PLL向量,ATE怎么用?

挑喜欢的阅读即可。

ATE/ATS内部结构简介

ATE/ATS:自动测试设备/自动测试系统,也称测试机是测试工程师在IC测试中必须使用的工具,本文主要从技术层面对ATE/ATS的组成及软硬件及其接口要求进行了简明扼要的论述,以便测试工程师了解、掌握。

通常将在计算机控制下,能自动进行各种信号测量、数据处理、传输,并以适当方式显示或输出测试结果的系统称为自动测试系统,简称ATS(Automated Test System),这种技术我们称之为自动测试技术。

在自动测试系统中,整个工作都是在预先编制好的测试程序统一指挥下完成的,系统中的各种仪器和设备是智能化的,都可进行程序控制。

自动测试系统(ATS)是一个不断发展的概念,随着各种高新技术在检测领域的运用,它不断被赋予各种新的内容和组织形式。自动测试技术创始于20世纪50年代,从20世纪50年代至21世纪的今天,大致分为以下三代。

- 第一代自动测试系统是根据测量任务专门设计的,主要用计算机技术来进行逻辑定时控制,主要动能是进行数据自动采集和自动分析,完成大量重复数据的测试工作,承担繁重的数据运算和分析任务。系统中的仪器采用专用接口,因此系统较为复杂,通用性差,不利于自动测试系统的推广应用。

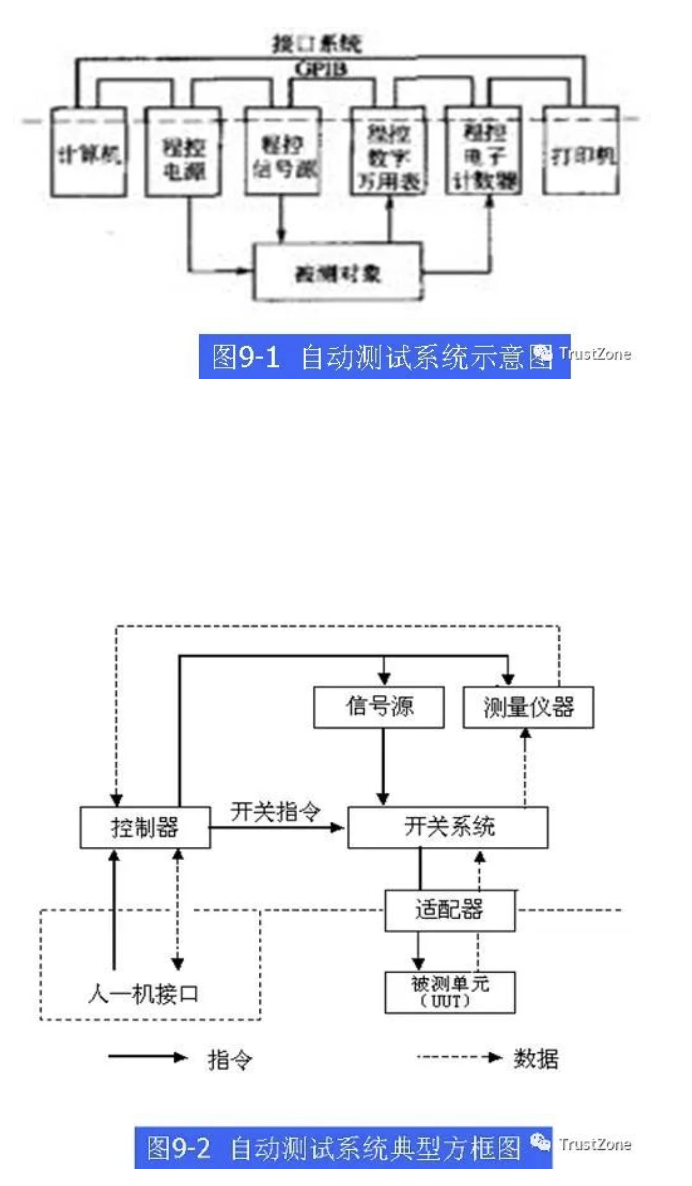

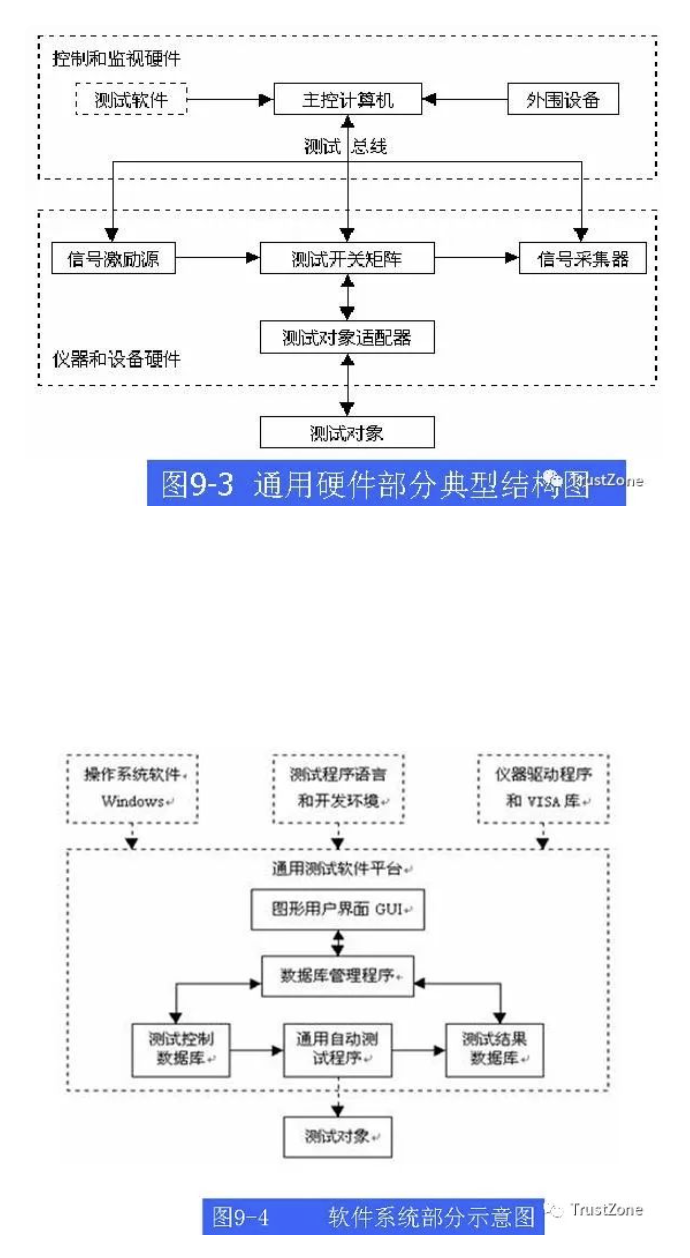

- 第二代自动测试系统是尽可能利用现成的仪器设备,再利用计算机来共同组建成所需要的自动测试系统。为了系统组建方便,第二代自动测试系统中的仪器采用了标准化的通用接口,这样就可以把任何一个厂家生产的任何型号的可程控仪器连接起来形成一个自动测试系统。第二代自动测试系统示意图如图9-1所示。系统的典型方框图9-2所示。

图中表明,当前的自动检测系统,通常包括以下几个部分。

- (1)控制器

- (2)激励信号源

- (3)测量仪器

- (4)开关系统

- (5)适配器

- (6)人机接口

- (7)检测程序

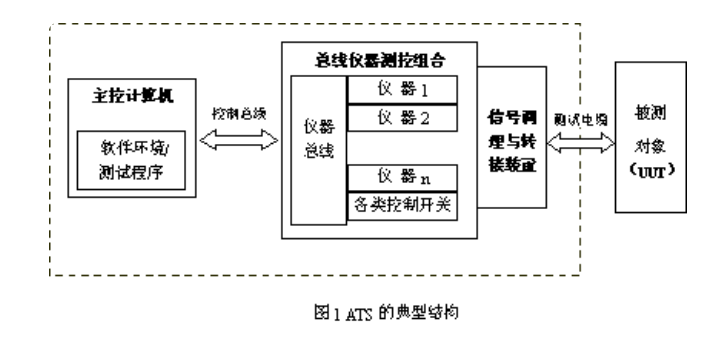

- 第三代自动测试系统 大体说来,它也是由微型计算机、通用硬件系统和软件系统三部分组成。但是,第三代自动测试系统主要体现以软件控制、以功能组合方式实现的合成仪器自动测试技术,以高速A/D、D/A和DSP芯片为基础组成通用测试仪器硬件系统(即通用硬件部分,结构如图9-3所示),而测试/测量任务的实现以及系统升级完全依靠软件来实现(即软件系统部分,如图9-4所示)。

通用测试系统架构

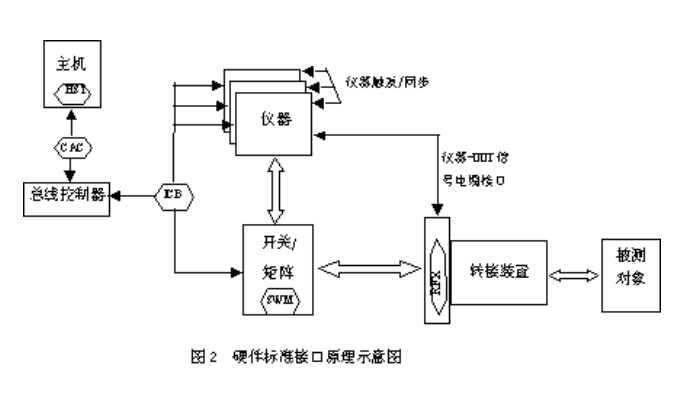

通用化自动测试系统(ATS)主要由图1所示的三个部分组成:

- 主控计算机、 其中“主控计算机”中的软件主要包括操作系统、编译器、测试执行程序(TP)。

- 总线仪器测控组合、 “总线仪器测控组合”中主要包括模块化测试测量仪器、各类控制开关、通讯总线等。

- 信号调理与转接装置。 “信号调理与转接装置”主要包括各类测量与激励控制信号的转接与适配。

主控计算机及系统软件提供TP的开发与运行环境,并通过控制总线控制测试测量仪器完成TP的执行、取回测试数据,生成测试报表。

值得一提的是,作为通用化的测试系统应该具有一个开放式的结构,系统软、硬件各组成部分均进行模块化分割,各模块之间应该是通过标准接口(或协议)相互联系。

为了保证系统的灵活性,同时充分发挥设计人员的创造力,只需从接口上对开放式系统进行定义,而不需要定义各模块的内部具体实现,同时还要考虑到系统功能的可扩充性和技术的可升级性。

因此,作为通用测试系统两大重要组成部分的硬件系统和软件系统均需要具备灵活、开放的体系结构与接口设计。

通用测试系统硬件架构

通用测试系统硬件设计的关键在于UUT接口的标准化设计,UUT接口标准化的目的在于提供一种能够在多个UUT之间方便转换的硬件连接结构。

这种结构通过对机械连接机构、接插件和连接器的标准化规定提供了可工作于宽频带信号范围内的接口连接方式。

为采用VME总线、VXI总线、PCI总线、PXI总线仪器的通用测试系统提供了标准化(IEEE P1505转接装置接口(RFI)系统标准)的有力支撑。

图2是通用化硬件组成及接口原理示意框图。其中:开关矩阵(SWM)接口和ATS转接装置(RFX)接口是ATS的重要组成部分,因为ATS仪器和UUT是通过SWM来连接的,大多数的激励和测量信号是通过RFX作用到UUT上的。

标准RFX接口限制了不同类型信号在接收器的不同位置上出现,SWM可实现多种仪器与由标准RFX接口所确定的多功能终端的连接。SWM接口与RFX的标准化提高了互操作性,并降低了重组费用,可以确保测试UUT所需要ATS仪器能被切换到转接装置所需要的任何管脚。

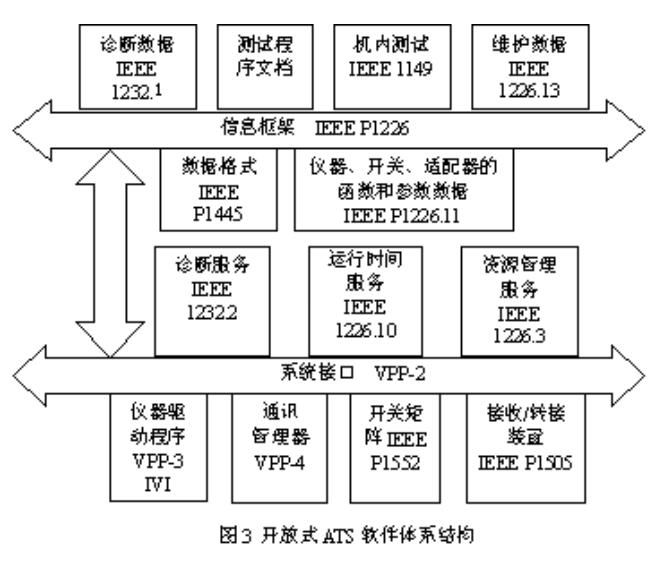

通用测试系统软件架构

自动测试系统的软件是TPS的重要组成部分,直接影响通用测试系统的性能和效率。自动测试软件结构也有相应的标准。如图3所示,开放式ATS体系结构中包含了多种标准的开放式软件接口关系。

IEEE 1226中的测试基础框架(TFF)定义了开发和执行测试程序和测试流程的一系列接口,软件功能模块通过这些接口实现信息交换,这些带有标准接口的功能模块组成了测试基础框架。

但是标准并没有定义这些模块的实现,留给开发者很大的自由度,使之可以用C/C++或ATLAS等语言实现TFF。

在科学技术高度发展的今天,测试工作处于各种现代装备系统设计和制造的首位,是保证现代装备系统实际性能指标的重要手段。

代表着测试技术与仪器行业最高水平的通用ATE(自动测试设备) /ATS(自动测试系统) 技术,以商业成品设备和技术(Commercial Off The Shelf)为依托,采用开放的工业标准、低廉的设备价格、有效的技术支持和最新技术的商业产品和技术,在电子设备的生产与制造行业成为降低生产成本、提高生产效率的重要手段。

IC测试基本原理与ATE测试向量生成

IC测试主要的目的是将合格的芯片与不合格的芯片区分开,保证产品的质量与可靠性。随着集成电路的飞速发展,其规模越来越大,对电路的质量与可靠性要求进一步提高,集成电路的测试方法也变得越来越困难。

因此,研究和发展IC测试,有着重要的意义。而测试向量作为IC测试中的重要部分,研究其生成方法也日渐重要。

IC 测试

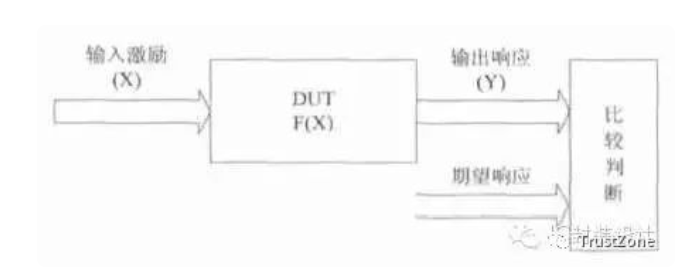

IC测试原理

IC 测试是指依据被测器件(DUT)特点和功能,给DUT提供测试激励(X),通过测量DUT 输出响应(Y)与期望输出做比较,从而判断DUT是否符合格。图1所示为IC测试的基本原理模型。

根据器件类型,IC测试可以分为数字电路测试、模拟电路测试和混合电路测试。

数字电路测试是IC测试的基础,除少数纯模拟IC如运算放大器、电压比较器、模拟开关等之外,现代电子系统中使用的大部分IC都包含有数字信号。

数字IC 测试一般有直流测试、交流测试和功能测试。

功能测试

功能测试用于验证IC是否能完成设计所预期的工作或功能。功能测试是数字电路测试的根本,它模拟IC的实际工作状态,输入一系列有序或随机组合的测试图形,以电路规定的速率作用于被测器件,再在电路输出端检测输出信号是否与预期图形数据相符,以此判别电路功能是否正常。其关注的重点是图形产生的速率、边沿定时控制、输入/输出控制及屏蔽选择等。

功能测试分静态功能测试和动态功能测试。静态功能测试一般是按真值表的方法,发现固定型(Stuckat)故障。动态功能测试则以接近电路 工作频率的速度进行测试,其目的是在接近或高于器件实际工作频率的情况下,验证器件的功能和性能。

功能测试一般在ATE(Automatic Test Equipment)上进行,ATE测试可以根据器件在设计阶段的模拟仿真波形,提供具有复杂时序的测试激励,并对器件的输出进行实时的采样、比较和判断。

交流参数测试

交流(AC)参数测试是以时间为单位验证与时间相关的参数,实际上是对电路工作时的时间关系进行测量,测量诸如工作频率、输入信号输出信号随时间的变化关系等。常见的测量参数有上升和下降时间、传输延迟、建立和保持时间以及存储时间等。交流参数最关注的是最大测试速率和重复性能,然后为准确度。

直流参数测试

直流测试是基于欧姆定律的,用来确定器件参数的稳态测试方法。它是以电压或电流的形式验证电气参数。直流参数测试包括:接触测试、漏电流测试、转换电平测试、输出电平测试、电源消耗测试等。 直流测试常用的测试方法有加压测流(FVMI)和加流测压(FIMV),测试时主要考虑测试准确度和测试效率。通过直流测试可以判明电路的质量。如通过接触测试判别IC引脚的开路/短路情况、通过漏电测试可以从某方面反映电路的工艺质量、通过转换电平测试验证电路的驱动能力和抗噪声能力。 直流测试是IC测试的基础,是检测电路性能和可靠性的基本判别手段。

ATE测试平台

ATE(Automatic Test Equipment)是自动测试设备,它是一个集成电路测试系统,用来进行IC测试。一般包括

- 计算机和软件系统、

- 系统总线控制系统、

- 图形存储器、

- 图形控制器、

- 定时发生器、

- 精密测量单元(PMU)、

- 可编程电源和测试台等。

- 系统控制总线提供测试系统与计算机接口卡的连接。

- 图形控制器用来控制测试图形的顺序流向,是数字测试系统的CPU。它可以提供DUT所需电源、图形、周期和时序、驱动电平等信息。

测试向量及其生成

测试向量(Test Vector)的一个基本定义是:测试向量是每个时钟周期应用于器件管脚的用于测试或者操作的逻辑1和逻辑0数据。

这一定义听起来似乎很简单,但在真实应用中则复杂得多。因为逻辑1和逻辑0是由带定时特性和电平特性的波形代表的,与波形形状、脉冲宽度、脉冲边缘或斜率以及上升沿 和下降沿的位置都有关系。

ATE测试向量

在ATE语言中,其测试向量包含了输入激励和预期存储响应,通过把两者结合形成ATE 的测试图形。

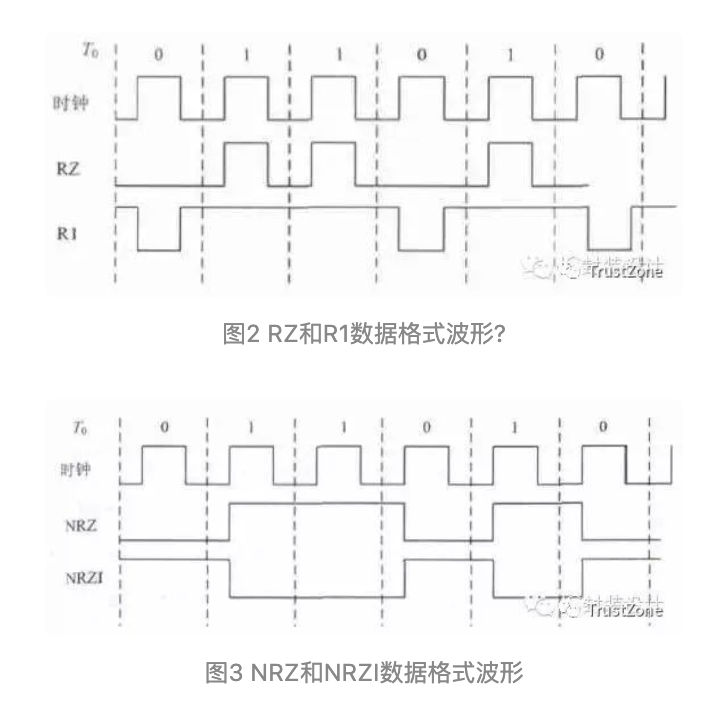

这些图形在ATE中是通过系统时钟上升和下降沿、器件管脚对建立时间和保持时间的要求和一定的格式化方式来表示的。

格式化方式一般有RZ(归零)、RO(归1)、NRZ(非归零)和NRZI(非归零反)等。

图2为RZ和R1格式化波形,图3为NRZ和NRZI格式化波形。

RZ数据格式,在系统时钟的起始时间T0,RZ测试波形保持为“0”,如果在该时钟周期图形存储器输出图形数据为“1”,则在该周期的时钟周期期间,RZ测试波形由“0”变换到“1”,时钟结束时,RZ 测试波形回到“0”。若该时钟周期图形存储器输出图形数据为“0”,则RZ测试波形一直保持为“0”,在时钟信号周期内不再发生变化。归“1”格式(R1)与RZ相反。

非归“0”(NRZ)数据格式,在系统时钟起始时间T0,NRZ测试波形保持T0前的波形,根据本时钟周期图形文件存储的图形数据在时钟的信号沿变化。即若图形文件存储数据为“1”,那么在相应时钟边沿,波形则变化为“1”。NRZI波形是NRZ波形的反相。

在ATE中,通过测试程序对时钟周期、时钟前沿、时钟后沿和采样时间的定义,结合图形文件中存储的数据,形成实际测试时所需的测试向量。

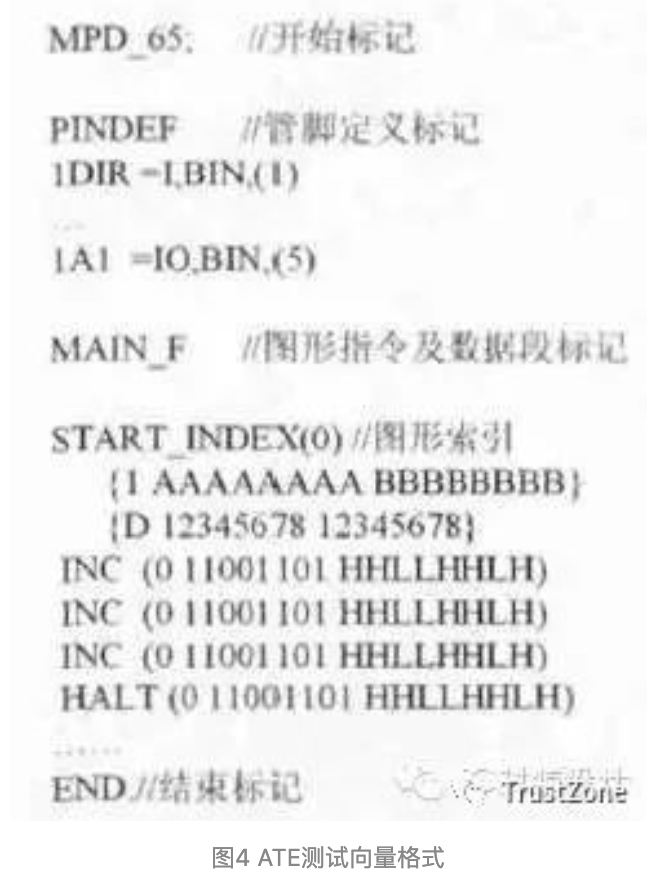

ATE测试向量与EDA设计仿真向量不同,而且不同的ATE,其向量格式也不尽相同。以JC-3165型ATE为例,其向量格式如图4所示。

ATE向量信息以一定格式的文件保存,JC-3165向量文件为

.MDC文件。在ATE测试中,需将

.MDC文件通过图形文件编译器,编译成测试程序可识别的 * .MPD文件。在测试程序中,通过装载图形命令装载到程序中。

ATE测试向量的生成

对简单的集成电路,如门电路,其ATE测试向量一般可以按照ATE向量格式手工完成。而对于一些集成度高,功能复杂的IC,其向量数据庞大,一般不可能依据其逻辑关系直接写出所需测试向量,因此,有必要探寻一种方便可行的方法,完成ATE向量的生成。

在IC设计制造产业中,设计、验证和仿真是不可分离的。其ATE 测试向量生成的一种方法是,从基于EDA工具的仿真向量(包含输入信号和期望的输出),经过优化和转换,形成ATE格式的测试向量。

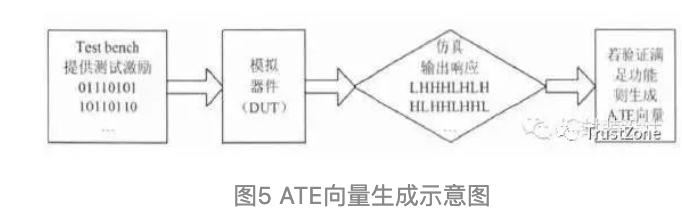

依此,可以建立一种向量生成方法。利用EDA工具建立器件模型,通过建立一个Test bench仿真验证平台,对其提供测试激励,进行仿真,验证仿真结果,将输入激励和输出响应存储,按照ATE向量格式,生成ATE向量文件。其原理如图5所示。

测试平台的建立

(1)DUT模型的建立

- ① 164245模型:在Modelsim工具下用Verilog HDL语言[5],建立164245模型。164245是一个双8位双向电平转换器,有4个输入控制端:1DIR,1OE,2DIR,2OE;4组8位双向端口:1A,1B,2A,2B。端口列表如下:

input DIR_1,DIR_2,OE_1,OE_2;`inout [0:7] a_1,a_2,b_1,b_2;`reg [0:7] bfa1,bfb1,bfa2,bfb2;//缓冲区

- ② 缓冲器模型:建立一个8位缓冲器模型,用来做Test bench 与164245 之间的数据缓冲,通过 在Testbench总调用缓冲器模块,解决Test bench与164245模型之间的数据输入问题。

(2)Test bench的建立

依据器件功能,建立Test bench平台,用来输入仿真向量。 Test bench中变量定义:

reg dir1,dir2,oe1,oe2; //输入控制端`reg[0:7] a1,a2,b1,b2; //数据端reg[0:7] A1_out[0:7]; //存储器,用来存储数据reg[0:7] A2_out[0:7];reg[0:7] B1_out[0:7];reg[0:7] B2_out[0:7];`

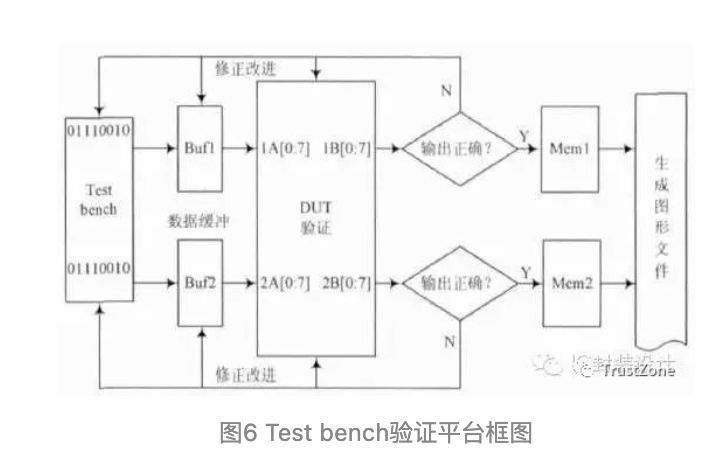

通过Test bench 提供测试激励,经过缓冲区接口送入DUT,观察DUT输出响应,如果满足器件功能要求,则存储数据,经过处理按照ATE 图形文件格式产生 * .MDC 文件;若输出响应有误,则返回Test bench 和DUT模型进行修正。其原理框图可表示如图6所示。

(3)仿真和验证

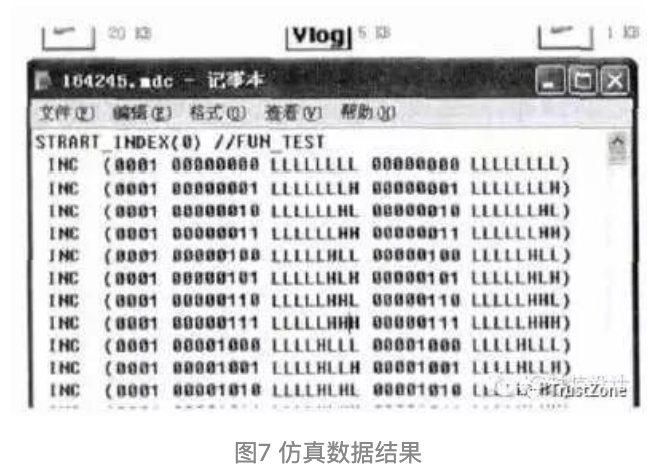

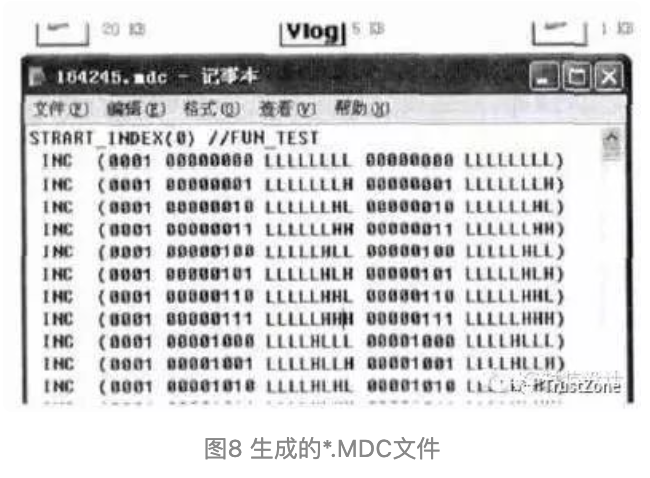

通过Test bench 给予相应的测试激励进行仿真,得到预期的结果,实现了器件功能仿真,并获得了测试图形。图7和图8为部分仿真结果。

在JC-3165的 * .MDC图形文件中,对输入引脚,用“1”和“0”表示高低电平;对输出引脚,用“H”和“L”表示高低电平;“X”则表示不关心状态。

由于在仿真时,输出也是“0”和“1”,因此在验证结果正确后,对输出结果进行了处理,分别将“0”和“1”转换为“L”和“H”,然后放到存储其中,最后生成 * .MDC图形文件。

结论

本文在Modelsim环境下,通过Verilog HDL语言建立一个器件模型,搭建一个验证仿真平台,对164245进行了仿真,验证了164245的功能,同时得到了ATE所需的图形文件,实现了预期所要完成的任务。

随着集成电路的发展,芯片设计水平的不断提高,功能越来越复杂,测试图形文件也将相当复杂且巨大,编写出全面、有效,且基本覆盖芯片大多数功能的测试图形文件逐渐成为一种挑战,在ATE上实现测试图形自动生成已不可能。

因此,有必要寻找一种能在EDA工具和ATE测试平台之间的一种灵活通讯的方法。

目前常用的一种方法是,通过提取EDA工具产生的VCD仿真文件中的信息,转换为ATE测试平台所需的测试图形文件,这需要对VCD文件有一定的了解,也是进一步的工作。

基于ATE的IC测试原理、方法及故障分析

本文以ATE为基础,讨论了 集成电路测试的基本原理和测试方法,并进行了故 障分析.

集成 电 路 测试主要分为三种:

- verificationt est,

- mass production test

- burn-in.

verifa ct iont est,称之为芯片验证,主要用来验证一个新的设计在量产之前功能是否正确,参数特 性等是否符合pec以及电路的稳定性和可靠性.测 试范围包括功能测试和AC/DC测试,测试项目相 对来说比较全面.其主要目的除了调试之外还为量产测试作准备.Verification的周期直接关系到产品的质量和竞争力以及投放市场的时间.

mass production test,称之为量产测试.量产测 试在整个Ic生产体系中位于制程的后段,其主要 功能在于检测Ic在制造过程中所发生的瑕疵和造 成瑕疵的原因.因此,量产测试是确保Ic产品良好 率,提供有效的数据供工程分析使用的重要步骤. mass production test以测试时间计费,同时测试设 备价格的高低也将影响每小时的测试费用,从而直 接影响产品的成本,因此提高测试覆盖率和测试效 率非常重要.

burn- in ,主要用于测试可靠性.采用各种加速 因子来模拟器件长期的失效模型,常用的有加高温, 加高电压等.

集 成 电 路测试的基本原则是通过测试向量对芯片施加激励,测量芯片响应输出(response),与事先 预测的结果比较,若符合,则大体上可以说明芯片是好的。

原文连接:基于ATE的IC测试原理、方法及故障分析.PDF[1]

浅谈基于ATE的IC测试精确度及稳定性问题

随着IC产业的飞速发展,IC的复杂度及其电气参数的性能也日益提高,同时也给IC测试带来了众多难题,其中测试的精确度及稳定性是一直困扰工程师的两大难题,尤其在量产ATE测试时表现更为严重,那么,如何在测试中做到精确、稳定的测试这些IC的各项性能参数,以确保产品质量,并避免由于测试不稳定而导致反复重测而浪费大量测试时间呢?

本文就IC测试的基本参数:电压、电流、时间、THD等的测试进行深入分析,并举以实例来说明如何解决此类问题,以供广大测试工程师参考。

电压测试问题

在IC的测试中,电压的测试是所有测试参数中最为常见的一种参数,尤其是模拟芯片的测试,电压测试更显常见及重要,如:LDO、LED驱动、音频功放、运放、马达驱动等很多类型的模拟芯片都含有电压参数的测试,而且都是其主要性能参数。另外,也有很多其他的参数都是通过电压的测量来间接得到的,如增益(Gain)、电源电压抑制比(PSRR)、共模抑制比(CMRR)等。工程师们在调试中也经常会遇到电压测的不精确或者不稳定的现象,对于测试不精确的问题,目前主要采用correlation的办法,来调整测试的误差,但这种方法对于线性的芯片尚可使用,但对于非线性的芯片却无用武之地。针对测试不稳定的问题,大多采用多次测量取平均值的办法来解决,但这种办法也是治标不治本,同样会给产品的质量带来隐患。那么如何解决电压测试的这些问题呢?以下将具体分析产生这些现象的具体原因,并针对这些原因阐述一些解决办法。

- 1)、芯片工作状态未完全建立或有震荡

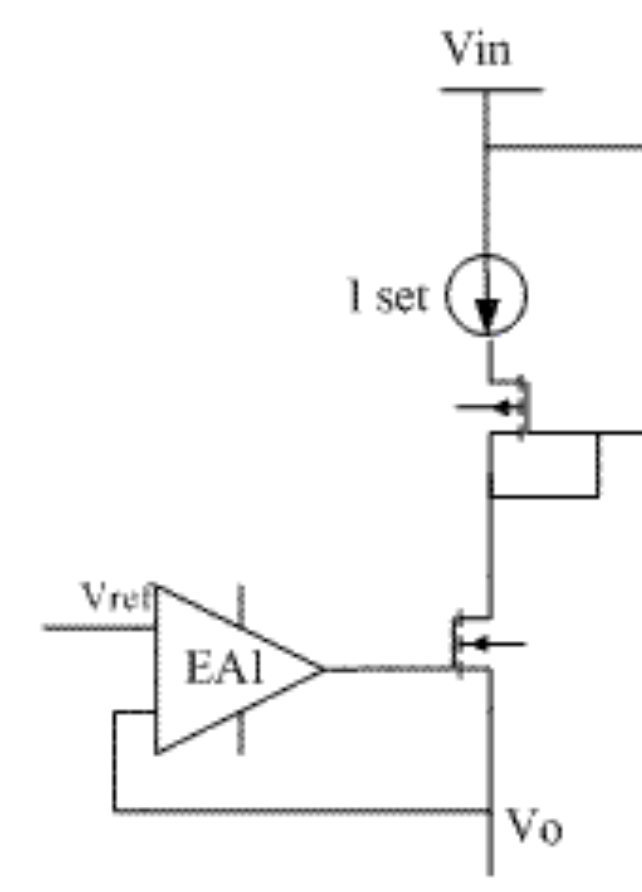

一般在开发测试程序之前必须了解所测试的芯片的功能及性能参数,这样在开发及调试程序时才能心中有数,比如测试LDO的输出电压参数,你必须清楚:在当前的输入及输出滤波电容之下,它的输入电压加上之后,输出电压需要多长时间才能达到稳定,而你在程序中设定的等待时间必须大于这个稳定时间,这样才能做到测试的准确且稳定。当然LDO的输出稳定时间一般都在微秒级(几十到上百微秒),所以调试时不太会遇到此类问题,但有的时候我们需要测试芯片内部的基准电压,但又没有办法直接进行测试,只能通过其他的引脚间接测试,如图1为LED驱动芯片的部分线路图,

图1

我们要测试芯片内部Vref的电压,但又没有直接的引脚出来,所以只能通过测试VO端的电压进行间接测试,但是需要注意的是:如果VO端悬空,没有任何电流流出,那么它上面的MOS管则不能正常导通工作,EA1的反馈回路也不能正常建立,而导致VO端的电压也不确定,此时测试的VO电压将不能代表Vref的电压。所以在测试时,我们必须给VO一定的负载让MOS管及EA1能够正常工作,这样才能正确测试Vref的电压。

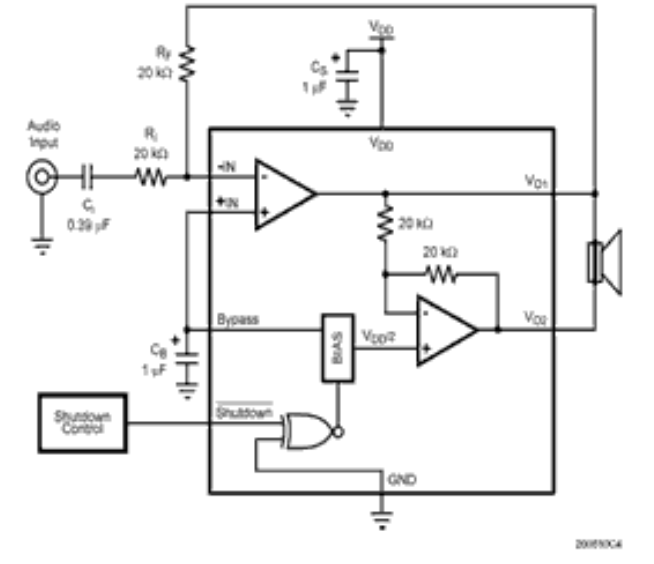

芯片工作状态的建立,有时需要比较长的时间,如图2为一音频功放(LM4990)的功能框图及典型应用线路图,

图2

我们在ATE测试时会测试一些静态直流参数,如bypass、Vo1、Vo2端电压值,当你仔细研读此芯片的手册,你会发现在电源电压为5V、Cbypass为1Uf时(注意不同的电源电压及Cbypass电容,其稳定时间也是不同的),bypass端的电压需要至少100ms才能达到稳定,而Vo1、Vo2端的电压又受bypass端电压的影响,所以要想稳定且准确的测试这些直流参数,必须要在芯片上电之后等待100ms以上再进行测试(必须考虑不同批次芯片间的差异,所以在实际测试中的等待时间可在120ms左右),但对于量产测试,测试时间的长短将直接影响到测试效率及测试费用,我们必须缩短测试时间!那么如何来解决这个问题呢,一般我们可以采用如下两种办法:

- 第一,可以减小Cbypass的电容,这样同样的充电电流及电压,充电时间会随着电容的减小而减少,可以使用0.1uF或者更小的电容来替代,此时有些读者可能会说:这样做肯定会影响到后面的交流参数(如THD)的测试,没错!肯定会有影响!那么又如何来解决呢?其实很简单,也可以有两种解决方案:1、通过测试评估,适当调整在0.1uF时的交流参数的测试规范,当测试要求不高时可采用此方案;2、通过外加继电器来选择测试直流及交流参数时的电容值,但是继电器的连接方式也是很有讲究的,不然也会对交流参数有影响,这在后面的段落中再详细阐述。

- 第二,可以采用预充电的方式对Cbypass进行提前大电流充电,如果bypass端在电源电压为5V时正常情况下是2.5V左右,我们可以预充电到2.3V,这样同样可以节省很多时间,但这种解决办法必须注意一个问题就是:不要在充电的同时给bypass端带来额外的干扰,而导致芯片不能正常工作。

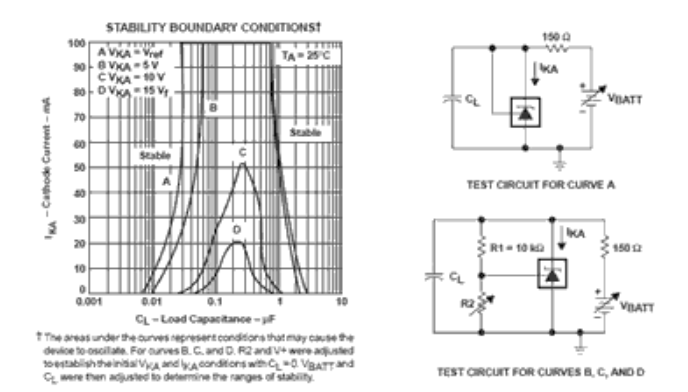

震荡在芯片调试时也是比较常见的现象,由此给芯片测试也带来诸多问题,引起震荡的原因有很多:输出容性负载的大小、阻抗不匹配、不当的反馈回路等,如图3为一款LDO(TL431)芯片手册中的一幅电性能特性曲线及测试图,图中明显规定了输出容性负载CL的大小范围,

但是我们在实际调试中可能没有注意到这一点,如果选用的输出电容不是在芯片稳定所需要的容值范围之内,那么输出就会产生震荡,导致输出测试不准且不稳定。所以在此再次提醒大家:在调试之前务必将芯片性能做到比较详细的了解,以免在后期的调试中浪费大量的时间。

另外震荡不光是在芯片正常工作时发生,在静态时也有可能发生。尤其当你测试放大倍数比较高的运放时,此时的输入引脚要特别注意,必要时要进行隔离,以免引入不必要的噪声而导致输出产生震荡。

DFT PLL向量,ATE怎么用?

自动测试设备 (ATE)对PLL(锁相环)进行测试时,我们首先要明白PLL在系统级芯片(SoC)中的重要性。它是SoC中关键的时钟或信号同步部件,其性能直接影响到芯片逻辑的正确运行。在测试PLL IP时,通常会有多个测试项目,如频率测试、相位噪声、锁定时间、稳定性、误差和漂移等。

但在SoC的ATE测试中,CP阶段通常只进行PLL频率和锁定测试。

那么DFT如何产生PLL 测试pattern,以及ATE如何根据这些pattern进行PLL测试?

DFT(Design For Test)是用于生成测试pattern以检测芯片功能和性能的技术。在生成PLL(Phase-Locked Loop)测试pattern的过程中,DFT通过使用特定的算法和测试向量来生成测试pattern。这些测试pattern旨在模拟PLL在不同条件下的行为,以确保芯片的PLL功能正常。

ATE(Automated Test Equipment)是一种用于自动测试芯片性能和功能的设备。在测试PLL时,ATE会使用由DFT生成的测试pattern来模拟芯片的输入,并监控芯片的输出以检查其功能是否正常。

这里的pattern指的是用于测试PLL的特定数据序列。这些数据序列在测试过程中被发送到芯片的输入管脚,并在芯片的输出管脚比较相应的输出数据序列。通过比较预期输出和模拟输出,ATE可以判断PLL是否正常工作。

总之,DFT通过生成测试pattern来模拟PLL的行为,ATE使用这些测试pattern来测试芯片的功能,并比较预期输出和模拟输出以判断芯片是否正常工作。

PART01 : DFT 产生 PLL 向量

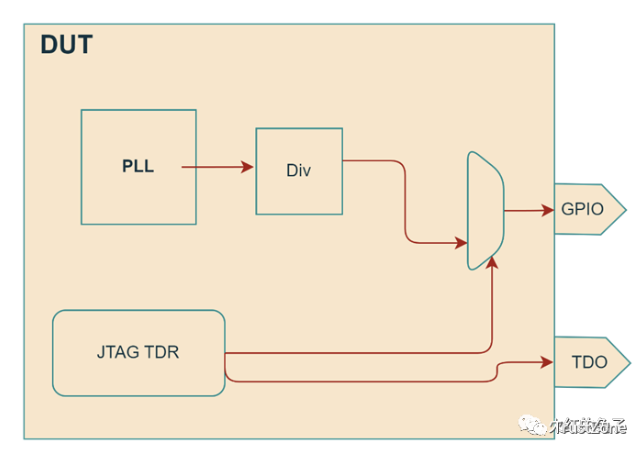

DFTer 每条PLL向量配置要求:(参考下图)

a) JTAG配置多个PLL为对应的待测频点.

b) 配置Div系数为最大,尽可能降低输出时钟的频率。

c) LOCK信号在TDO串行移出观测或者复用到IO上。

d) 切换IO复用后,PLL div 信号将会输出到对应GPIO上。

PLL输出频率的要求:10M~50M之间。 WHY?

1.上限受限于GPIO,在高于50M时,GPIO的输出特性随频率升高而减弱,最好低于50M。(机台PS1600最高1.6G采样频率,不需要考虑奈奎斯特频率的限制。)

2.下限需要考虑到不同测试方法的测试时间的影响,比如给一个32K的钟,机台需要构造更长的采样向量。

PART02 : ATE如何测试PLL

两种方法: 时域和频域测试,如下:

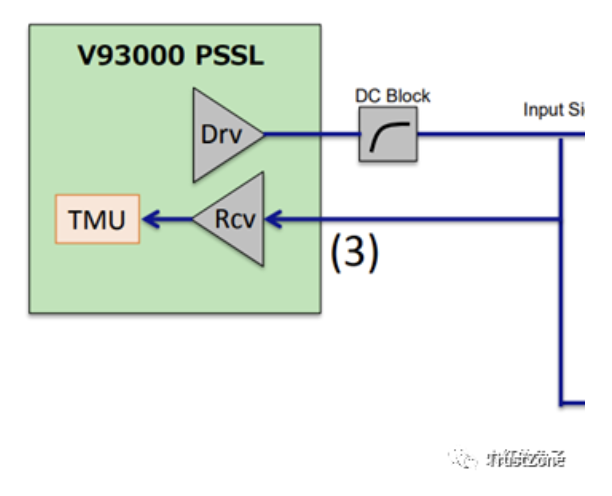

- 方法1. ATE time measurement unit ( TMU)测试。(时域,需要额外的TMU license,因此常不采用。)

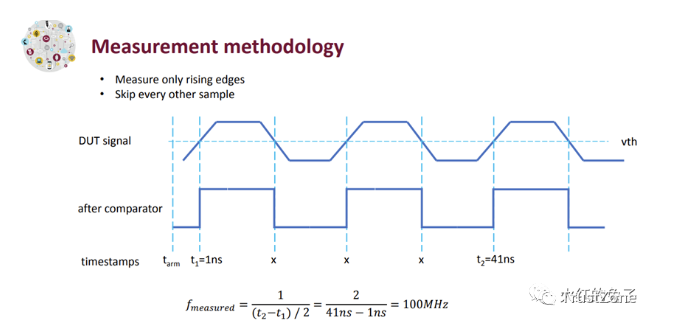

实施步骤:ATE 构造TMU TASK。TMU可以非常高精度地根据task设置trigger到上升沿的时刻,因此可以通过两个上升沿的差值计算出频率,支持多次采样,如下图所示:

- 方法2. 构造采样向量,离散傅里叶公式计算频谱,频谱的最大和第2大频率转换即为待测信号频率。(频域)

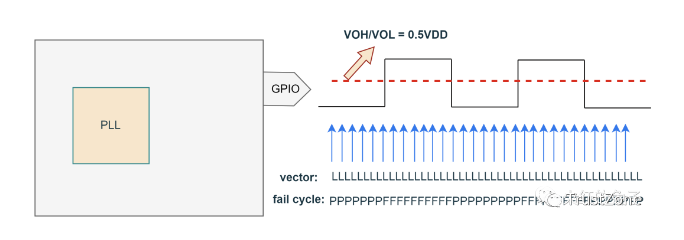

- a). 预先构造一条全L的向量,假设叫做PLL_sample.

- b). 运行DFT PLL向量的测试项.运行后, 不复位的情况下DUT此时稳定输出时钟信号。

- c). 运行预先构造好的向量PLL_sample,收集fail cycle,也就是ATE的error map。获得一串0/1组成的一维序列,如下图(点击可放大):

- d). 对获得一维序列进行汉明窗口卷积后,使用快速离散傅立叶变换获得频谱。通过频谱可以相当高精度的获得输出的频率,通过spec进行分bin。

如果想了解详情,可以参考论文,这里不再赘述:

A Method of High Precision Frequency Detection with FFT, IEIEC Transaction A Vol. J70-A No.5 pp.798-805, May 1987

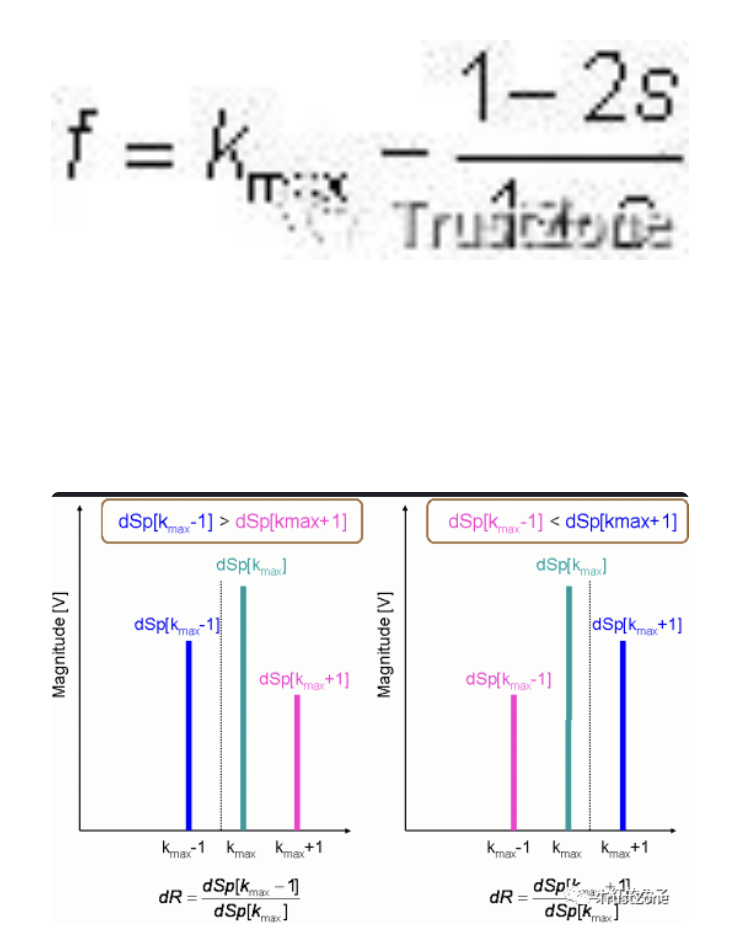

实际步骤:首先应用DSP_FFT与汉明窗口。然后搜索频谱第一大主频kmax 和第二大频,(kmax-1 或者 kmax+1)。如图所示,第1大和第2大频率成为关键参数。

核心为两个公式:

参考资料

感谢来自以下前辈分享组成了本文的学习资料:

- 浅谈基于ATE的IC测试精确度及稳定性问题[2]

- IC测试基本原理与ATE测试向量生成[3]

- IC测试机-ATE/ATS内部结构简介[4]

- 基于ATE的IC测试原理、方法及故障分析[5]

References

[1] 原文连接:基于ATE的IC测试原理、方法及故障分析.PDF [2] 浅谈基于ATE的IC测试精确度及稳定性问题 [3] IC测试基本原理与ATE测试向量生成 [4] IC测试机-ATE/ATS内部结构简介[5] 基于ATE的IC测试原理、方法及故障分析

作者:Hkcoco

文章来源:TrustZone

推荐阅读

更多IC设计干货请关注IC设计专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。