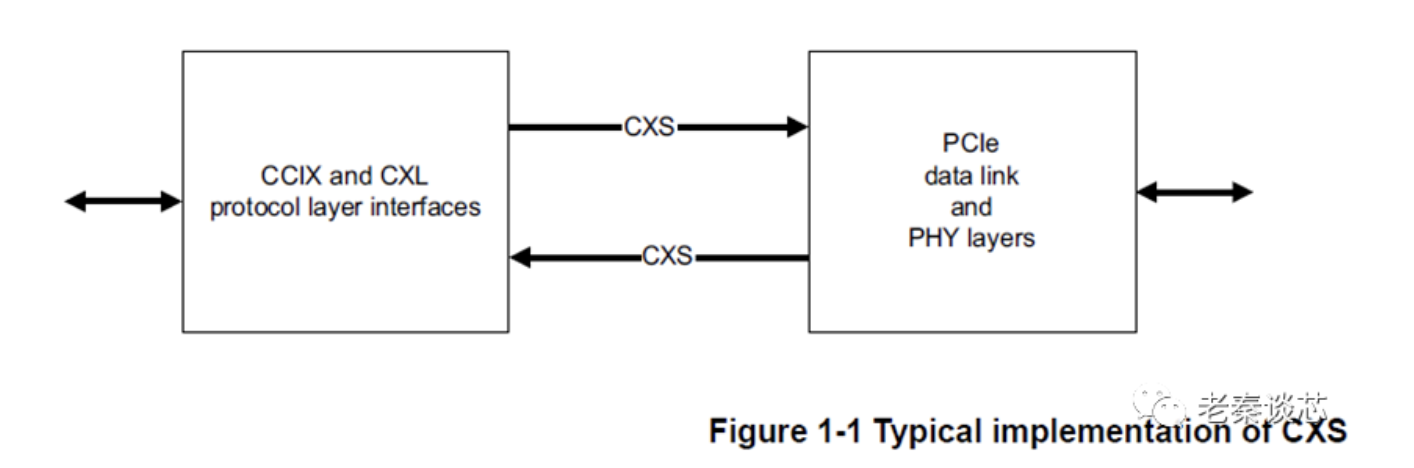

CXS (Credited eXtensible Stream)是一个流接口协议,主要用于点到点(point-to-point)的数据包通信。CXS接口的主要使用情形是在片上互连和PCIe控制器。CXS中的数据传输是单向的,因此一般CXS接口是收/发成对出现的。看到这里,是不是想起了什么?没错,就是AXI-Stream,同样也是点到点的流接口传输,比如中断控制器GIC的组件之间就采用了AXI-Stream。AXI-Stream在 FPGA中应用较多,尤其是多媒体领域。

CXS接口的数据传输是单向的,两端是Transmitter(TX)和Receiver(RX)。一个时钟周期内传输的数据称作flit。一个数据包可以占用一个或多个flit组成。

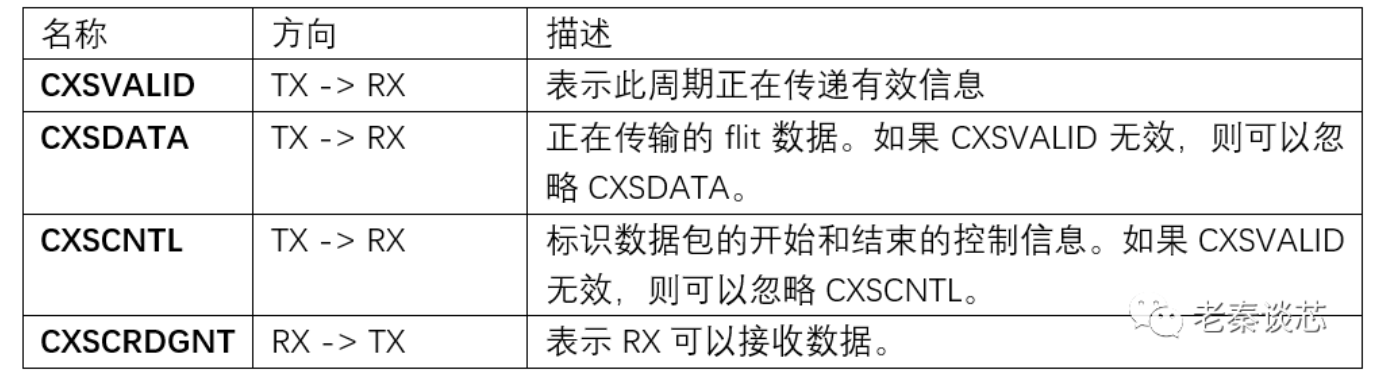

CXS的接口信号分为两部分,一部分是必须包含的,另一部分是可选信号。其中必须实现的信号如下(以下用正粗体表示信号,斜粗体表示属性):

从接口信号上看,并没有READY信号,也就是说CXS不像其它的AMBA总线,比如AXI,是通过“VALID - READY”来控制流量。

正如名字中的含义,CXS接口上的流量控制(flow control)通过信用交换机制实现。其信用机制规则如下:

- 仅当TX有信用值时才能发送数据

- 当接口刚完成复位或者是第一次active,TX没有信用值,不能发送数据

- RX通过CXSCRDGNT信号授予TX信用

- 在CXSCRDGNT被RX置位的每个时钟周期,RX授予一个信用值给TX。每个信用值可用作一次flit传输。

- RX必须保证每释放一个信用值,即可接收一个flit

- TX置位CXSVALID,每个时钟周期发送一个flit,占用一个信用值

- RX可以授予TX的最大信用值数由 CXS MAX CREDIT 属性决定

- TX只有等到CXSCRDGNT被置位之后,得到信用才能发送flit

- 可选,TX可以通过CXSCRDRTN返还信用值给RX,无需发送flit

- RX不能重用已消耗或返回的信用

- 如果TX在发送flit或者返回给RX信用的同时接收到一个信用,则TX端的可用信用数不变

正常情况下,TX发送一个flit给RX,同时消耗一个信用值;RX接收到flit,如果有能力接收更多的flit,则可以授予TX一个信用值;随后,TX得到新的信用值。从TX消耗信用值到得到新的信用值,这段时间称为信用延迟(credit latency)。为保证TX能够源源不断的发送数据,则需要设计好最大可用的信用数量,以保证不会由于信用延迟造成的断流。

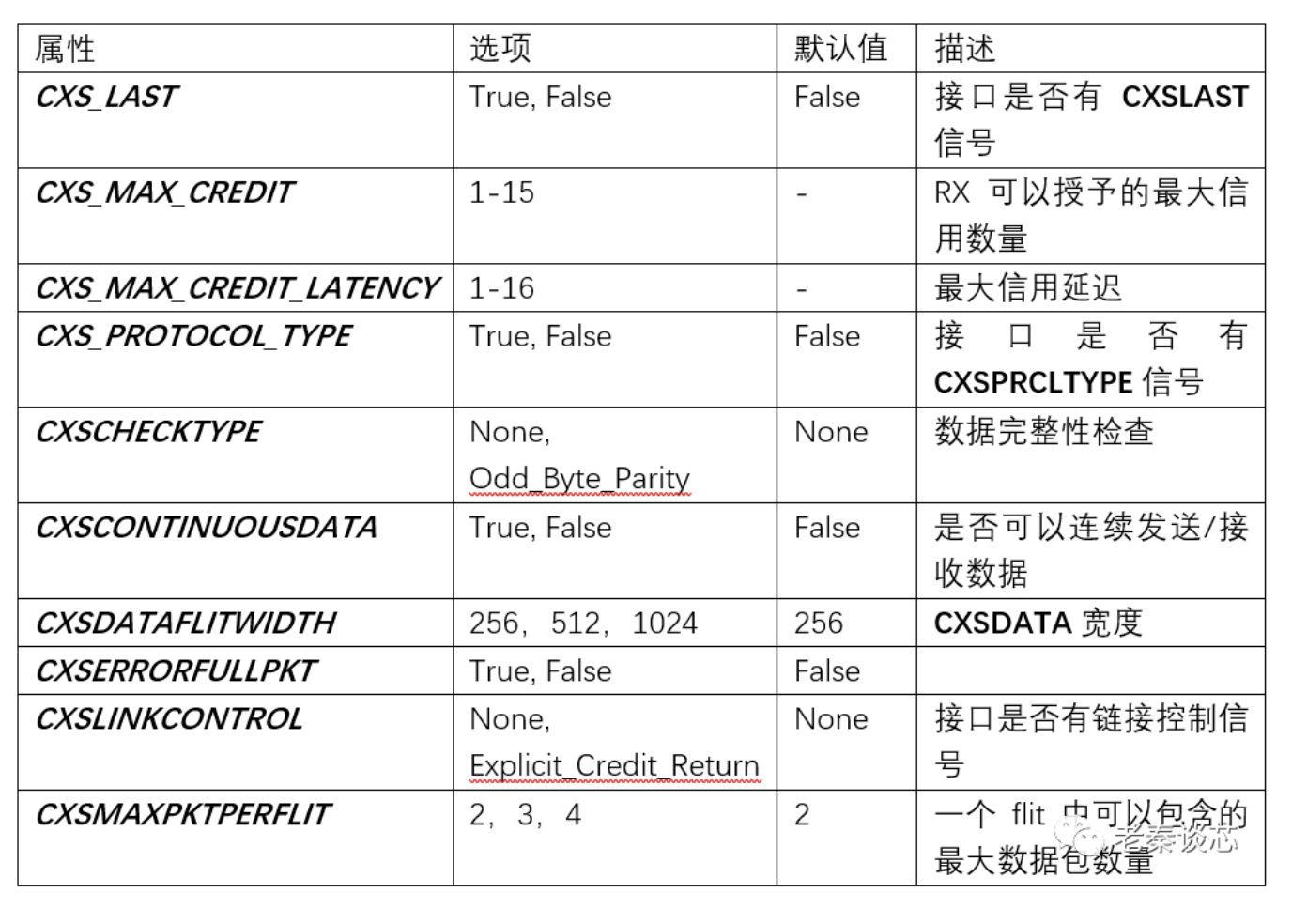

CXS接口的属性包括以下:

其中,TX和RX的属性可以单独设置。

CXS的完整接口信号列表如下:

其中,CXSLAST用于连续传输;CXSPRCLTYPE用于支持多种协议类型。

当CXSCHECKTYPE 属性被设置成Odd_Byte_Parity,CXS接口上会增加额外的信号线,用于增强接口信号的完整性。对于单bit信号线,增加一个bit,比如CXSVALID,增加一个信号CXSVALIDCHK;对于多bit信号,每8bit增加一个信号,比如256-bit的CXSDATA,增加一个32-bit信号CXSDATACHK。增加的信号与原信号相加为奇数。

CXS对每个flit中的数据包放置进行了限制,以简化数据路径实现:

- 数据包的第一个byte必须是16-byte对齐的边界

- 数据包的后续字节占用flit的后续字节

- 数据包可以在任何4-byte对齐的边界上结束。

- 从字节位置开始的数据包将占用该flit中的每个后续字节,直到数据包结束或flit结束。

- 如果flit结束时数据包中还有剩余字节,则该数据包将从下一个flit的字节[0]开始,并占据随后的每个字节位置,直到数据包结束或flit结束。

- 当数据包在flit中结束时,flit中的剩余字节可以不使用。

- flit中的任何数据包必须从相对于flit开始或前一数据包结束的第一个可用16-byte边界开始。

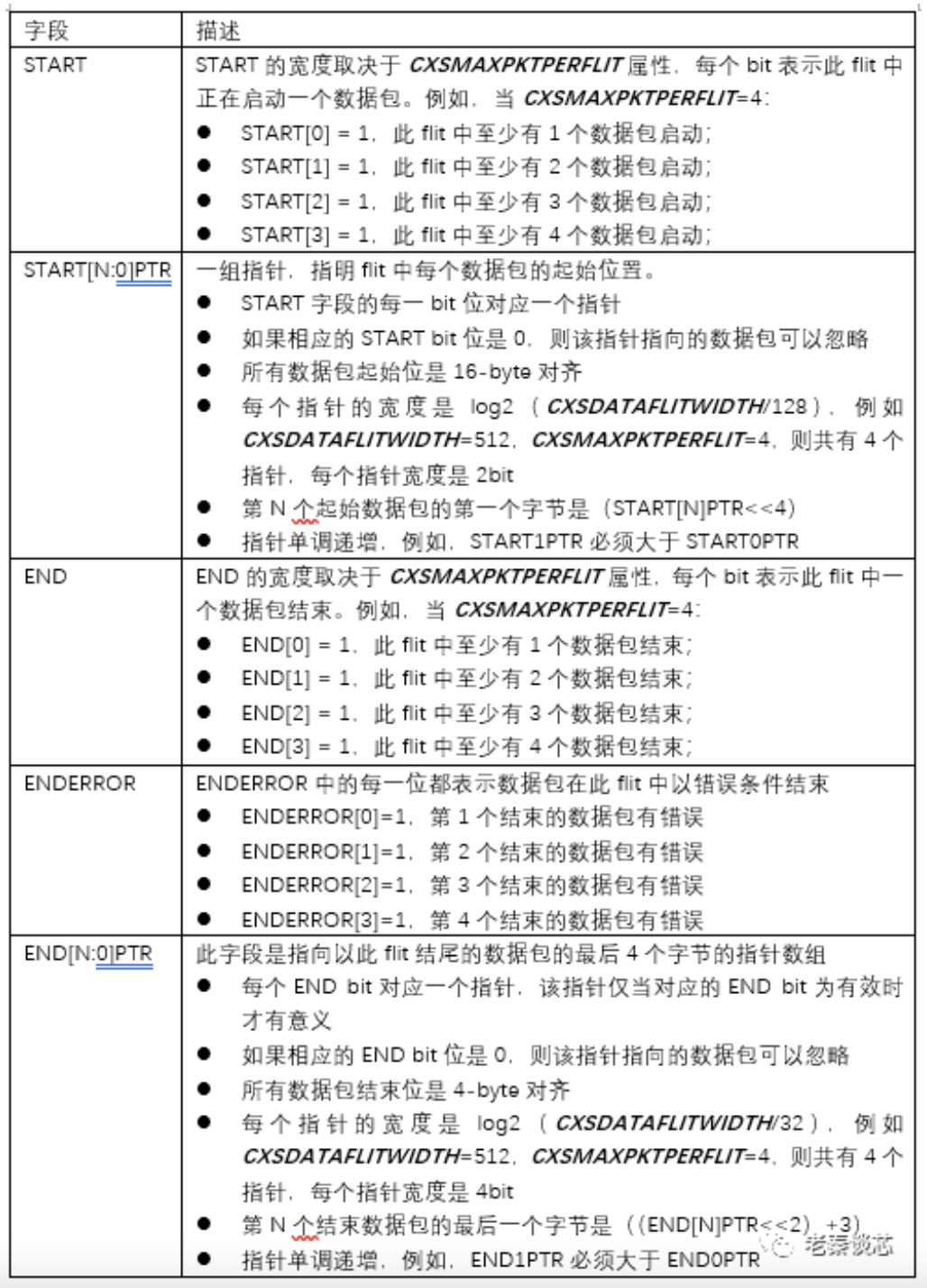

CXSCNTL信号总线可以分为五个字段,分别为:START,START[N:0]PTR,END,ENDERROR和END[N:0]PTR。下面分别解释。

下图给出CXSCNTL信号的组成示例。当属性CXSMAXPKTPERFLIT = 4,属性CXSDATAFLITWIDTH = 512时,CXSCNTL信号共有36-bit。

CXS接口传输满足以下要求的数据包大小需满足:

- 至少为4字节

- 为4字节的倍数

- 数据大小没有上限

如果CXS用于CCIX数据包传输,需要遵守CCIX的约定。

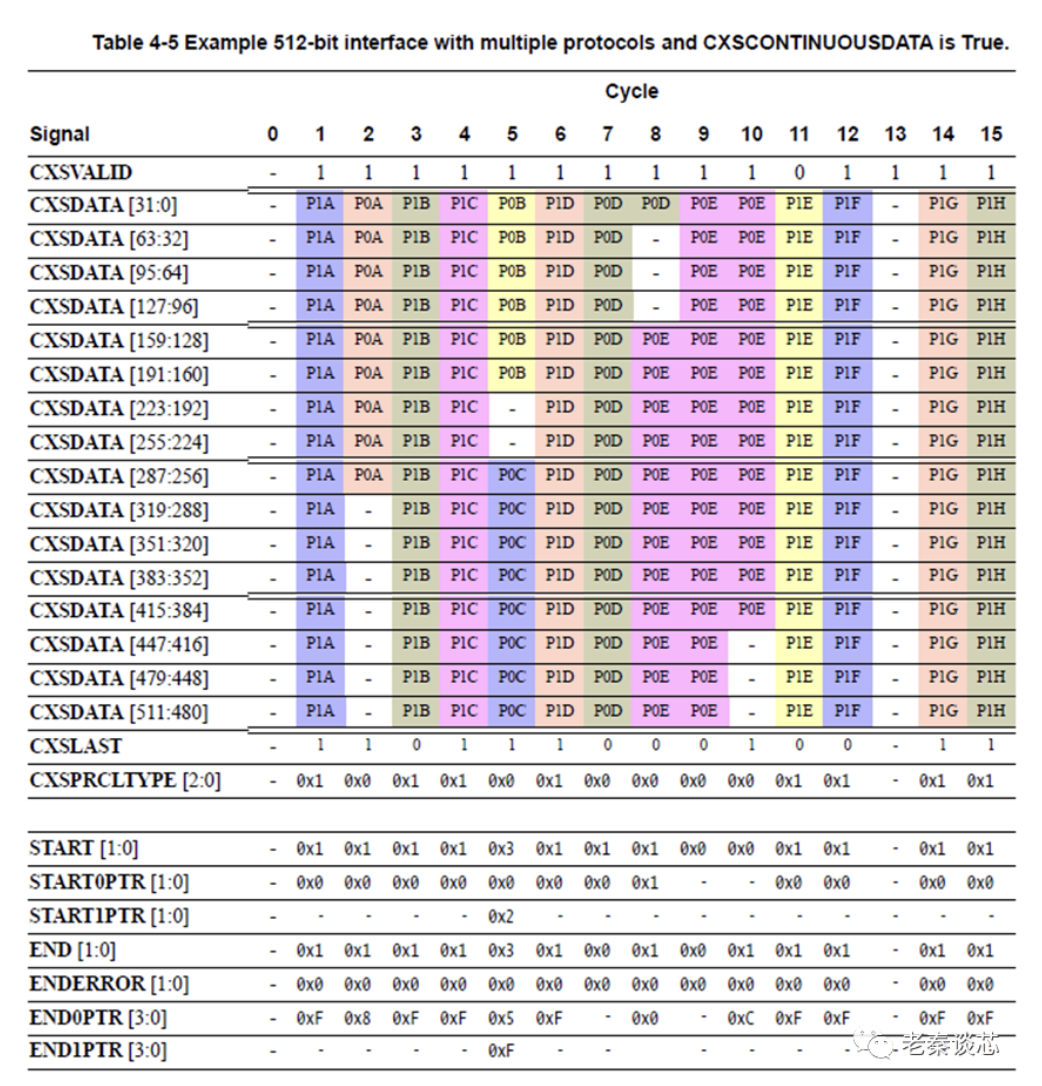

协议中给出了数据包传输的例子,看一个比较复杂的示例。属性 CXSMAXPKTPERFLIT = 4, CXSDATAFLITWIDTH = 512, CXSCONTINUOUSDATA = true,Protocol 0用于可变长数据包,Protocol 1用于固定长64-byte数据包。在Protocol 0中,P0D和P0E分组必须保持在一起;在Protocol 1中,P1B和P1C分组必须保持在一起,P1E,P1F和P1分组必须保持在一起。

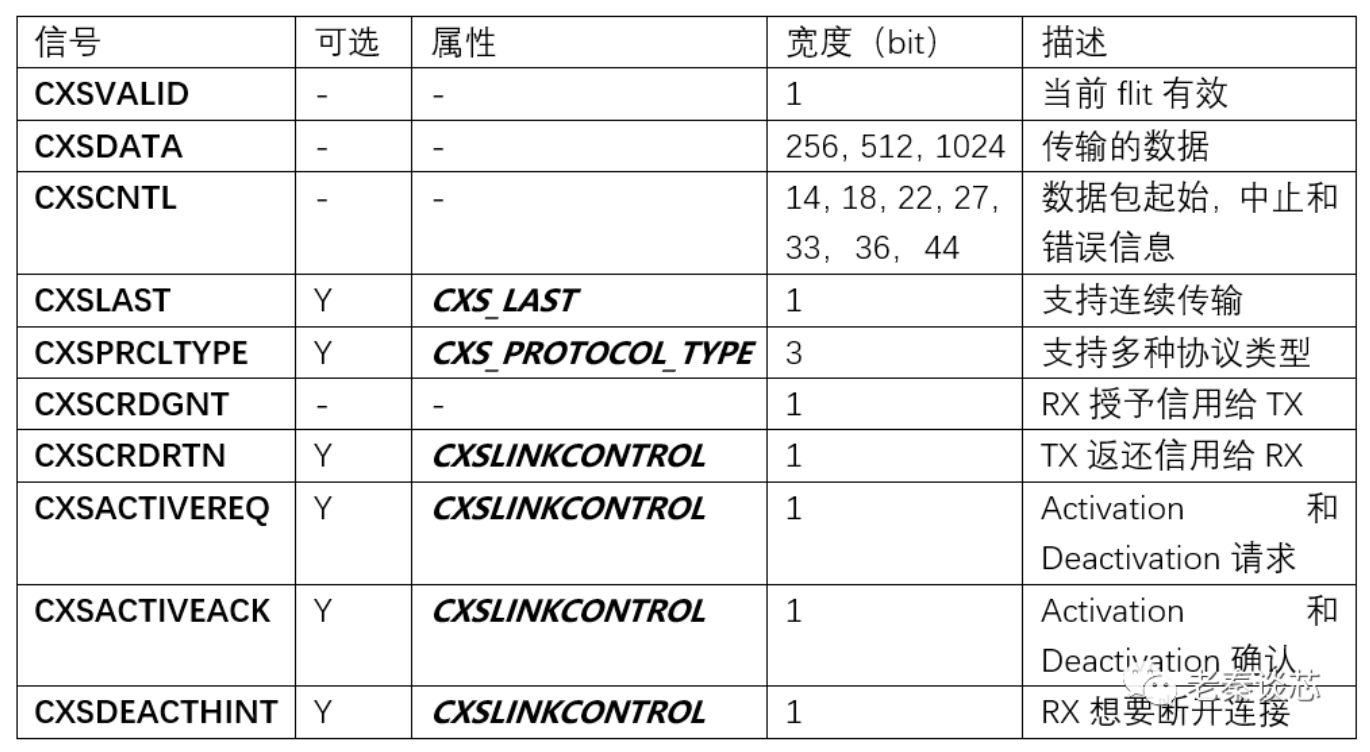

当属性CXSLINKCONTROL _ = Explicit Credit Return,CXS接口上会多出一组信号,CXSCRDRTN,CXSACTIVEREQ,CXSACTIVEACK和CXSDEACTHINT。

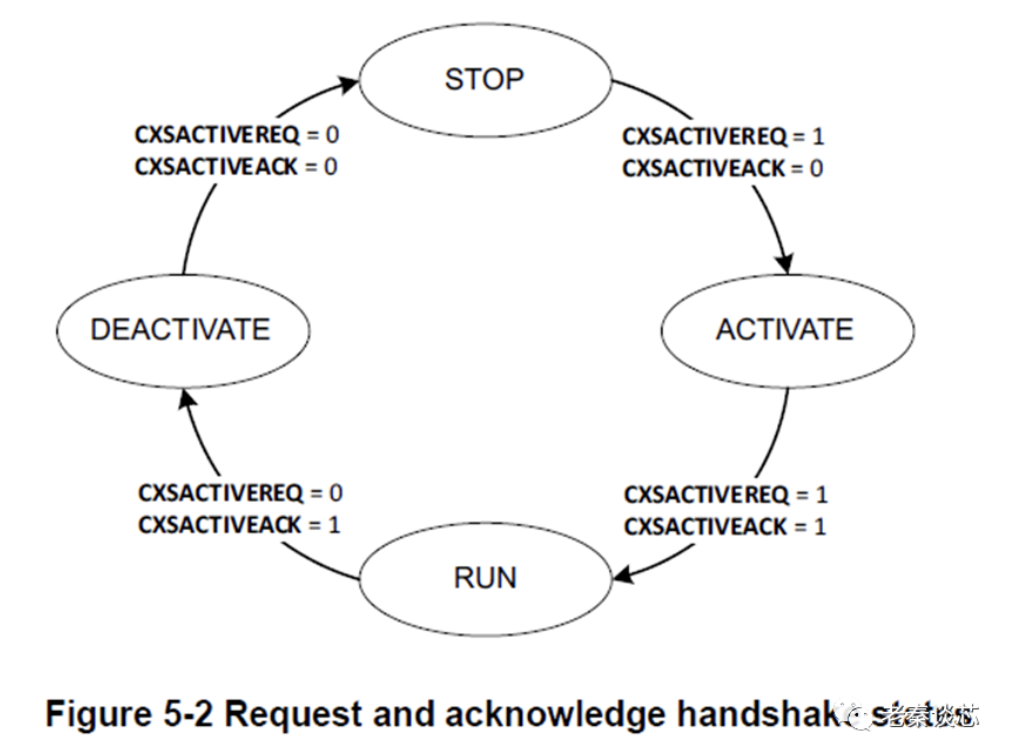

其中CXSACTIVEREQ,CXSACTIVEACK实现四相位的握手机制。握手机制共分为四种状态:

- STOP

- CXS接口在STOP状态时没有任何操作,所有的信用被RX收回

- STOP是一个稳定状态,CXS接口可以无限期保持在STOP

- RX此时不可以接收flit,也不可以授予信用

- TX此时不可以发送flit,也不可以返还信用

- 如果TX有flit等待发送,需要从STOP状态转移到ACTIVATE状态

- ACTIVATE

- 此状态为STOP到RUN的过渡

- 期望进入此状态后,期待CXS通路很快进入RUN状态

- 此状态下,TX必须接收信用,但还不可以发送flit

- RX此时不可以接收flit,也不可以授予信用

- RX不可以在状态ACTIVATE下发送信用。但是允许RX在进入RUN状态的同一周期内发送信用。由于存在潜在的竞争条件,因此TX在ACTIVATE状态下可能会收到信用

- 当RX准备好接收flit时,它可以从ACTIVATE状态转移到RUN状态

- RUN

- TX和RX在此状态下传输flit

- RUN状态是稳定状态,CXS通道可以一直保持在RUN状态

- RX可以接收flit,授予信用,接收返还的信用

- TX可以发送flit,,接收信用

- TX允许返还信用给RX

- TX可以在某些情况下从RUN状态切换到DEACTIVATE状态,比如TX没有flit可以发送了

- DEACTIVATE

- 此状态用于从RUN到STOP的过渡

- DEACTIVATE是一个中间状态

- 在进入此状态前,TX必须停止发送flit,由于潜在的竞争条件,RX有可能在此状态下接收flit

- RX可以发送信用,当RX发现TX返还信用时必须停止继续发送信用

- RX可以接收TX返还的信用

- TX必须发送信用返回,以便将所有信用返回给RX。

- 只有当所有信用都已返回时,RX才能退出该状态并移至STOP状态。

四种状态转换的关系如下图:

TX始终负责启动从RUN到STOP,或从STOP到RUN的状态更改,例如:

- TX端有flit等待发送,所以需要从STOP转移到RUN

- TX端没有flit可以发送,可以从RUN切换到STOP

- TX可以观测一个独立的边带信号,判断是否需要从RUN移动到STOP,或从STOP移动到RUN

- TX可以观测RX发出的CXSDEACTHINT来判断是否需要从RUN转移到STOP

当接口的一方同时执行两个操作时,即存在竞争条件。CXS规范允许数据流和链路控制信号组之间存在不同的延迟。因此,到达时的操作顺序可能与发出的顺序不同。竞争条件之所以会存在,是因为不要求CXSACTIVEREQ和CXSACTIVEACK信号不需要在TX和RX之间的其它信号具有相同的延迟。

CXS接口信号间的时序关系如下。

- CXSVALID,CXSDATA,CXSCNTL和CXSCRDRTN必须是同步关系,且具有相同的延时

- CXSCRDGNT,CXSACTIVEACK,CXSDEACTHINT必须是同步,但是可以有任意延时

- CXSACTIVEREQ必须是同步驱动,但是接收端可以异步接收,且可以任意延时

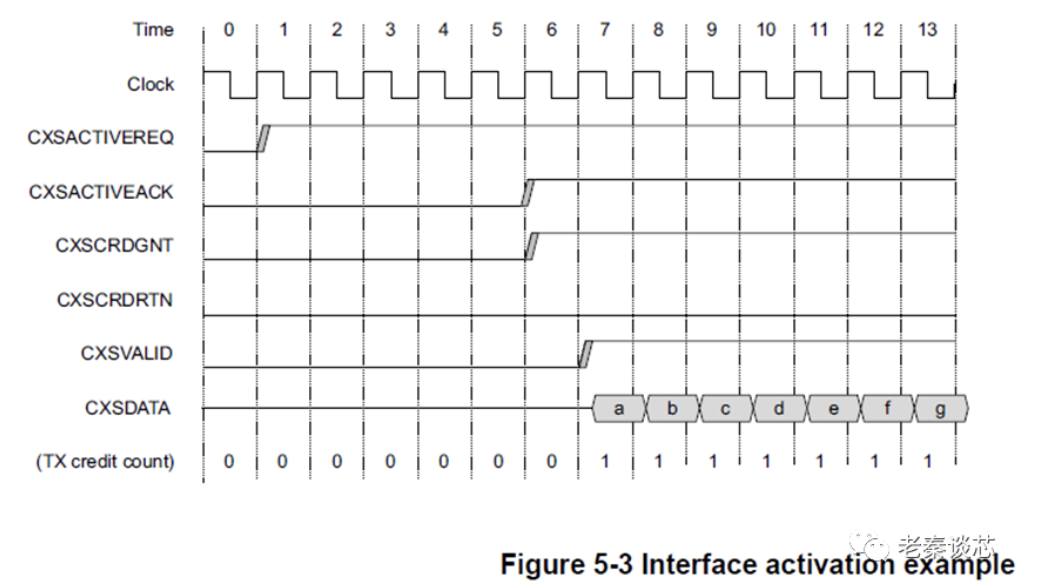

来看一个例子。

- 1.T0时刻,TX和RX都处于STOP状态,两边都可以关断时钟,甚至电源;

- T1时刻,TX置位CXSACTIVEREQ,从STOP转移到ACTIVATE;TX等待RX启动;

- 3.T6时刻,RX完成启动,置位CXSACTIVEACK;

- 4.CXSCRDGNT与CXSACTIVEACK**在同一时刻被置位;

- 5.T7时刻,TX接收到一个信用,发送一个flit;

- 6.TX在接收到更多信用后,连续发送flit。

某些情况下,CXS通道不能中断数据流,例如PCIe。这时,需要TX和RX实现一个存储转发(store-and-forward)buffer。

如果RX内置了这个buffer,数据包可以被下游完整接收。RX必须有足够的空间来存储TX所能发送的最大数据包。这种情况下,TX和RX可以设置属性 CXSCONTINUOUSDATA = False。TX无需缓存数据包。

如果RX没有缓冲区并且需要连续数据,则它会将 CXSCONTINUOUSDATA 属性设置为True,并且TX也必须将 CXSCONTINUOUSDATA 设置为True。然后,TX必须能够在不依赖其它接口的情况下发出数据包内的所有flit。

如果需要连续流量,必须确保RX有足够的信用来覆盖最坏情况下的往返信用延迟:

- RX和TX之间的CXSCRDGNT延迟

- TX端的CXSTXCRDGNT和CXSTXVALID之间的最大内部延迟,由TX的CXS_MAX_CREDIT_LATENCY属性描述

- RX和TX之间的CXSVALID延迟

- RX端的CXSTXVALID和CXSTXCRDGNT之间的最大内部延迟,由RX的CXS_MAX_CREDIT_LATENCY属性描述

RX可以发出的最大信用数取决于其缓冲区的大小,可以通过其 CXS MAX CREDIT 属性来描述。

如果下游接口的时钟比CXS链路慢,则可能不需要每个周期发送一个flit。在这种情况下,RX保持恒定流量所需的信用数可能小于往返延迟。

作者:老秦谈芯

文章来源:老秦谈芯

推荐阅读

更多IC设计干货请关注IC设计专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。