本期我们学习美光的一篇文章,关于如何估算 DDR 功耗,本文是对这篇文章粗略翻译和一点儿个人见解。原文链接:Calculating Memory Power for DDR4 SDRAM

原文是美光 DDR4 Technology Note (TN) 系列文章中的一篇,写的比较详尽又比较好懂,大家可以看下这系列的文章。 美光 DDR4 TN

本文是文章的第二部分,第一部分参见

LogicJitterGibbs:DDR 学习时间 (Part A - 2):学习 Micron DDR4 TN-40-07: DDR4 功耗估算 (1)

8 I/O Termination 功耗

前文基于 SPEC 计算的 Psch(RD) 和 Psch(WR) 只是 DRAM 读写功耗的一部分。SPEC 没有包括 output driver 功耗以及 ODT 功耗。这两者取决于系统的实现 ,每个系统的功耗数值和计算都不同。

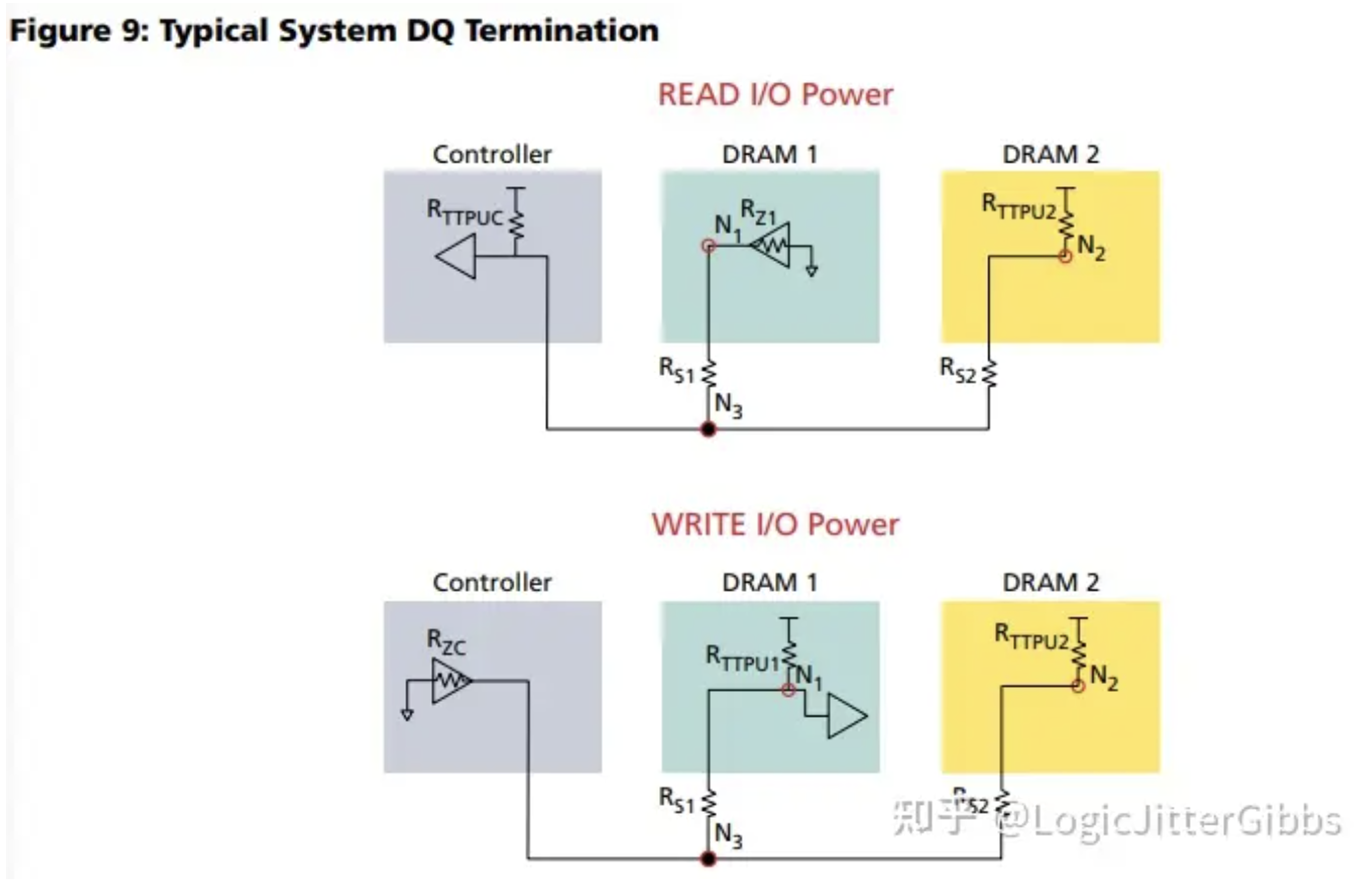

DDR4 IO 功耗与系统 DRAM 的总容量以及 DRAM 颗粒之间的连接结构有关,下图举了一个结构简单的小容量系统的例子,控制器连接有两个 DRAM 颗粒。此外,因为控制器和 DRAM 颗粒在数据线上都使用了 ODT,所以这个系统不需要额外的被动器件。

图 9- 典型的系统 DQ termination 结构

系统中的驱动的阻抗记为 R_ON,用于上拉到 V_DDQ 表示数值 1,或者下拉到 V_SSQ 表示数值 0。颗粒 Die 上的 termination 在功能上相当于一个上拉电阻。

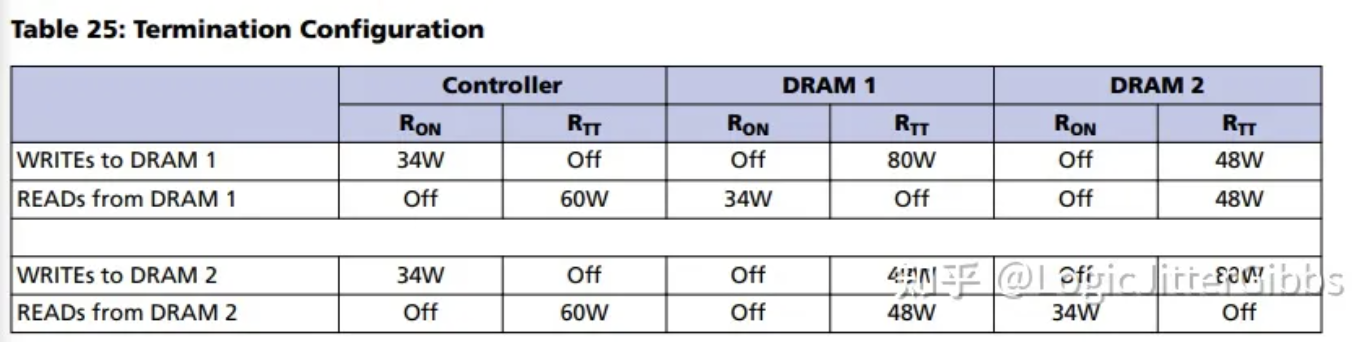

下表是这个系统一个简单的 termination 方案。

有两种计算系统中输出驱动和 ODT 功耗的办法,一种是基于 SPICE 模型的系统数据总线仿真,运行一个足够长的伪随机数据序列,然后计算得到平均功耗。另一种更简单的方式是通过输出驱动在阻抗上的 DC 功耗来估算,这种方法测得的数据一般不是系统最坏的情况,但是提供了一个 first-order (一阶)估算值。

以下是需要计算的 IO 功耗的组成:

- PdqRD: The output driver power when driving the bus

- PdqWR: The termination power when terminating a WRITE to the DRAM

- PdqRDoth: The termination power when terminating a READ from another DRAM

- PdqWRoth: The termination power when terminating write data to another DRAM

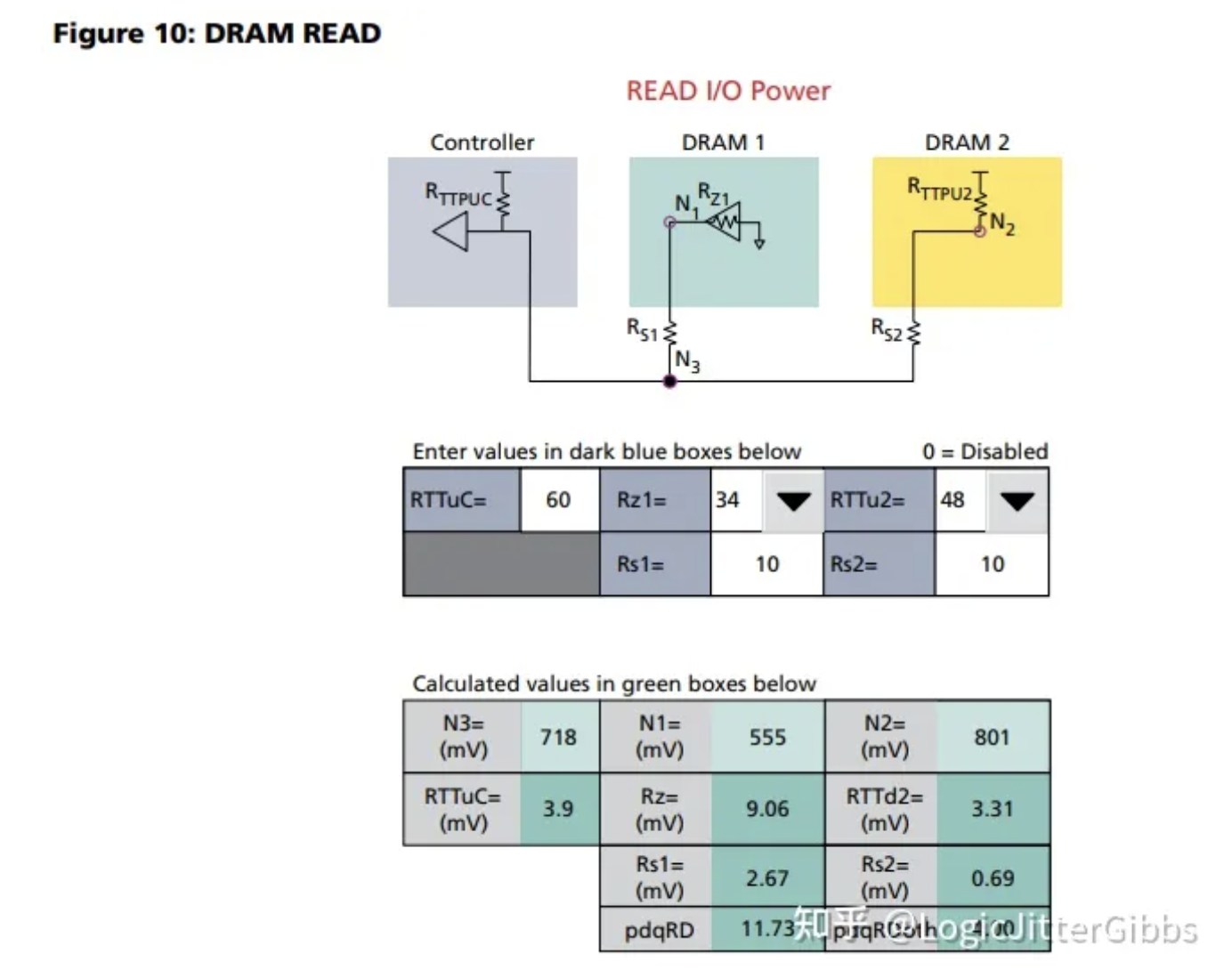

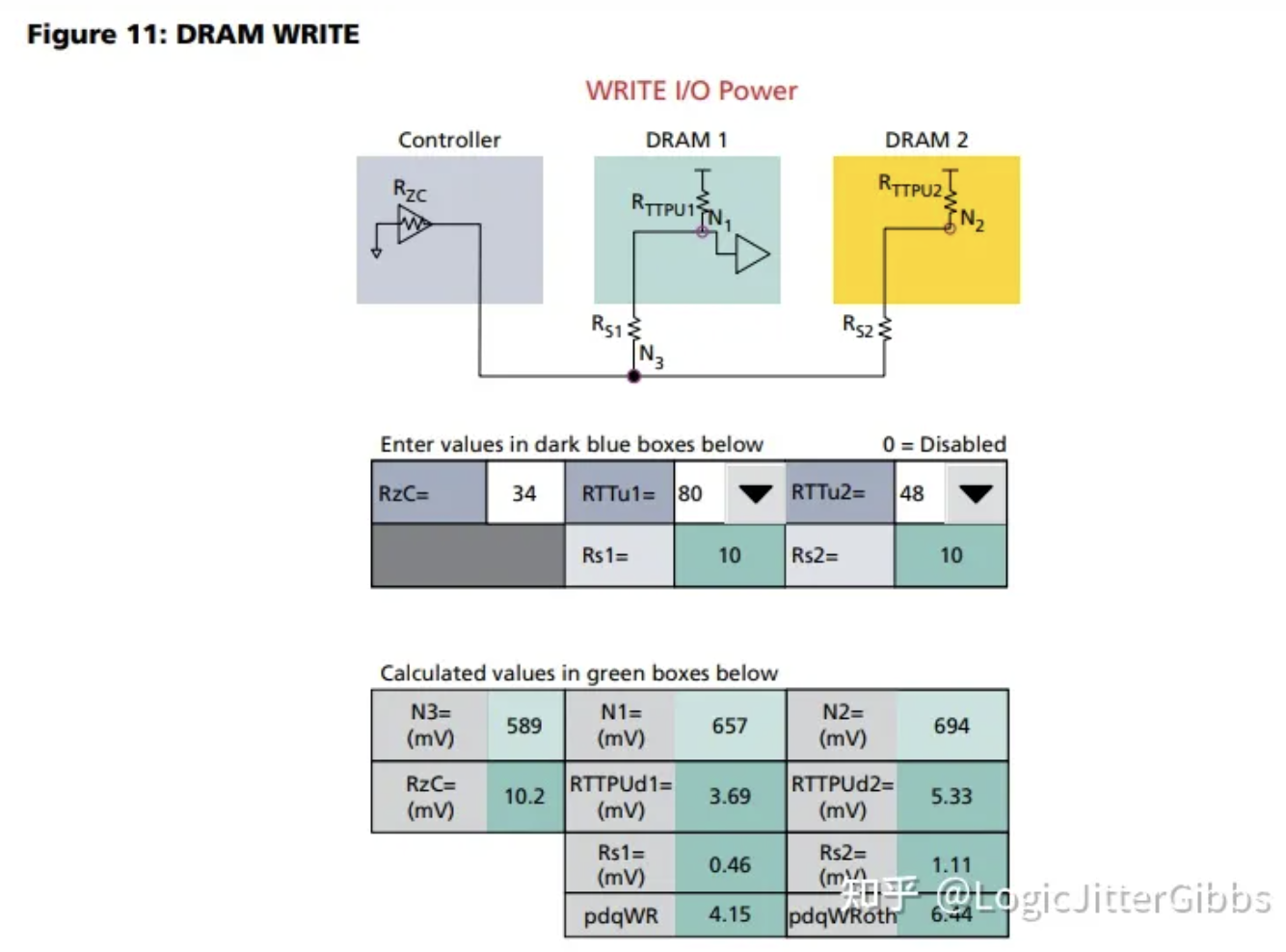

可以通过戴维宁等效电路计算 DRAM IO termination DC 功耗,如下面图 10 和图 11 所示。图片中的表格列出了 DRAM 每个 IO 的等效 DC 功耗。表格中的控制器功耗和线路串行功耗被没有被算到 DRAM IO 功耗中。

图 10- DRAM 读操作时的 IO 功耗计算

图 11- DRAM 写操作时的 IO 功耗计算

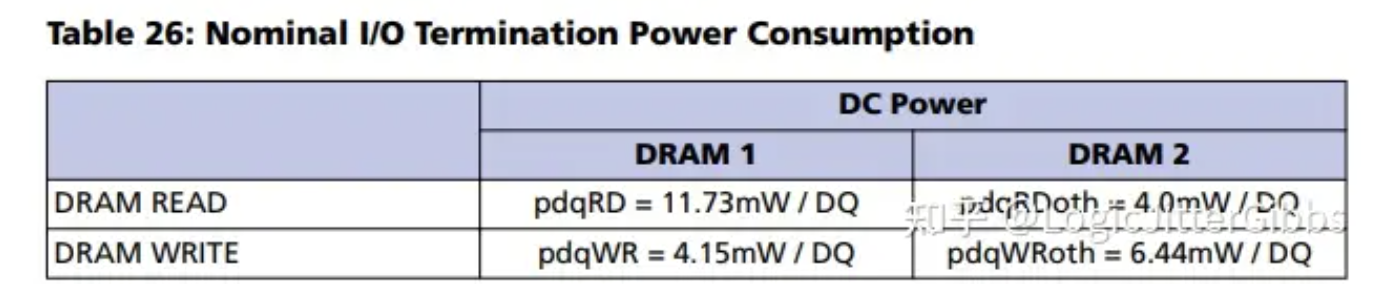

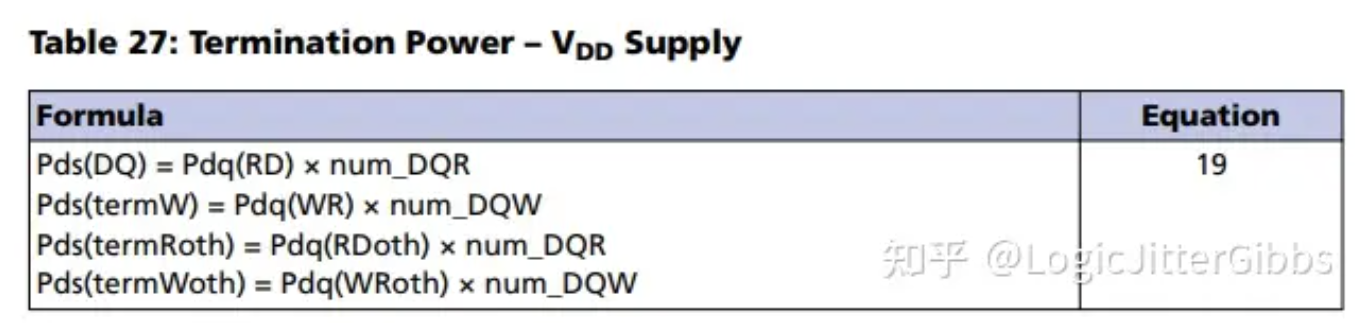

表 26 中的结果是单个 DQ IO 的功耗,DRAM IO 总功耗是通过把每个 DQ IO 上的功耗乘以 DQ 以及 DQS IO 数量的总和得到。在写操作时,还要算上 DQM IO 的数量。表 27 中的公式 19 计算 DRAM 4 种不同模式的功耗。

- Pds(DQ): DRAM output driver power when driving the bus

- Pds(termW): DRAM termination power when terminating a WRITE to the DRAM

- Pds(termRoth): DRAM termination power when terminating a READ from another DRAM

- PPds(termWoth): DRAM termination power when terminating write data to another DRAM

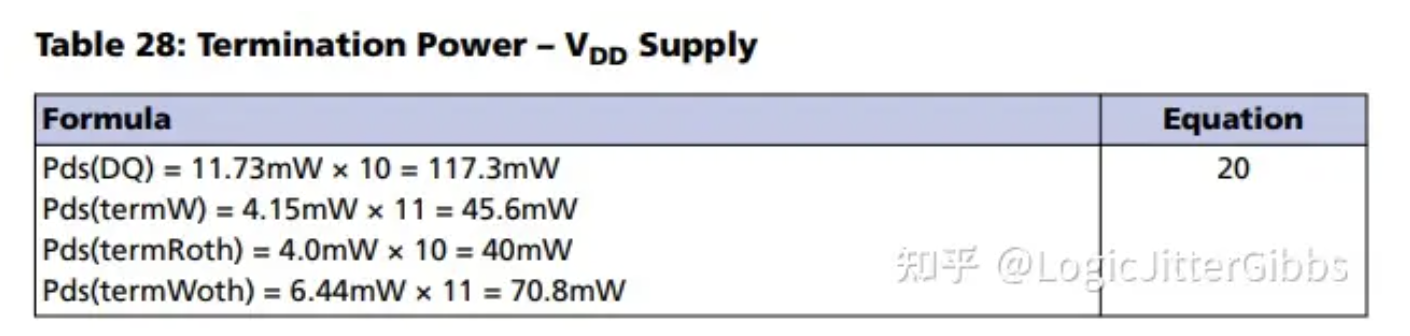

具体地,我们举一个 x8 颗粒 IO 功耗计算的例子来说明。这个 x8 颗粒具有 8 个 DQ IO 以及 2 个 DQS IO,所以 num_DQR = 10。算上一个额外的 DQM IO,写操作时的 num_DQW = 11,因此带入表 27 的公式得到表 28 中的结果。

此时,我们得到的 IO 功耗是四种情况不停在数据总线上发生时得到的 100% 功耗。需要根据四种情况在总线上出现的概率计算得到实际的 IO 功耗。这些情况出现概率和数据调度情况相关,因此需要具体情况具体计算。在后文 13 章的示例中,我们将做一个具体的计算。

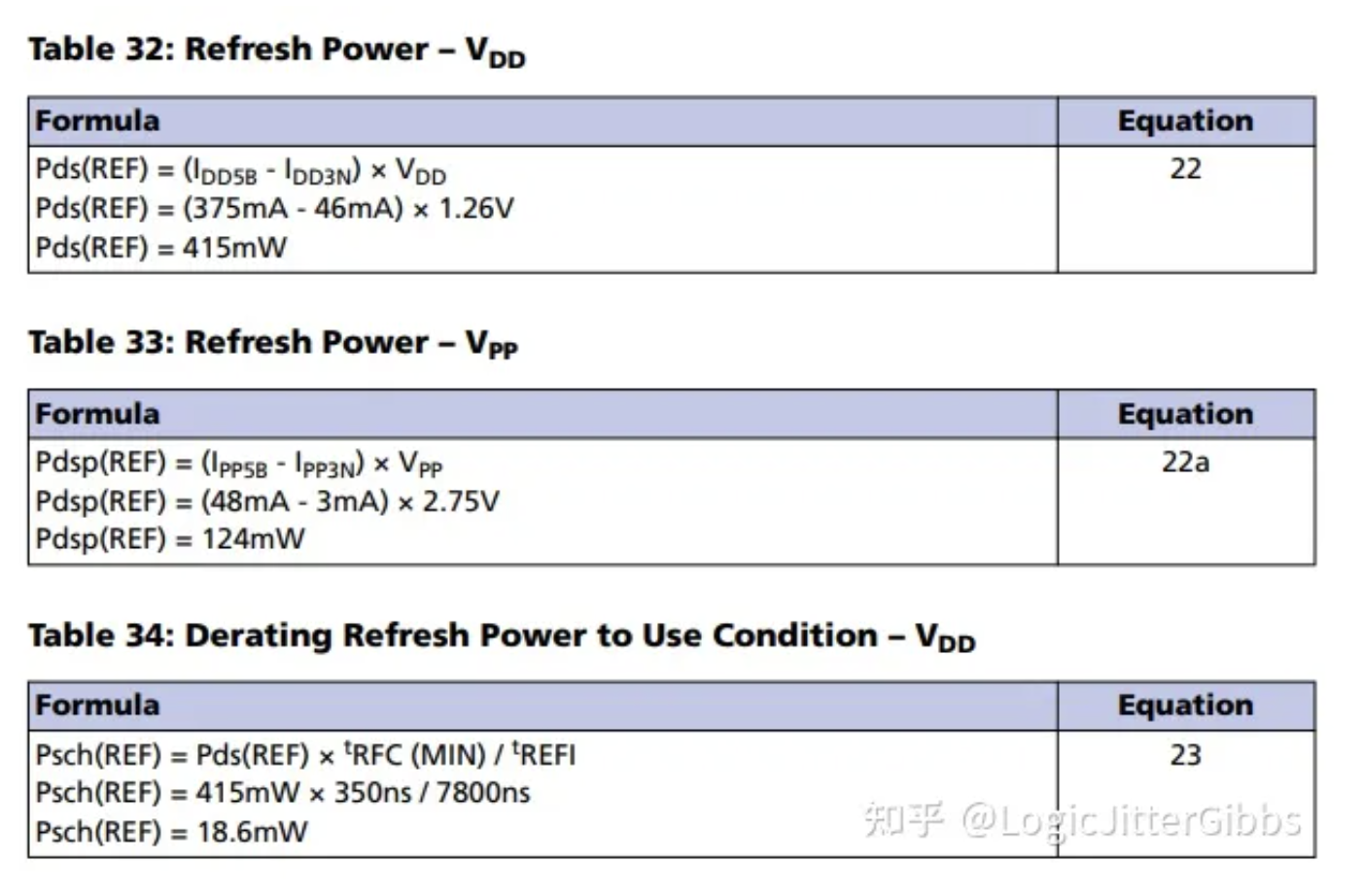

9 Refresh 功耗

DDR4 存储单元把信息存储在一个个非常小的电容中,这些电容会慢慢流失电荷,为了保持住电容中的数据,必须定时给这些电容充电,充电的过程被称为刷新 Refresh。保持数据的 Refresh 功耗是 DRAM 功耗的最后一个组成部分。

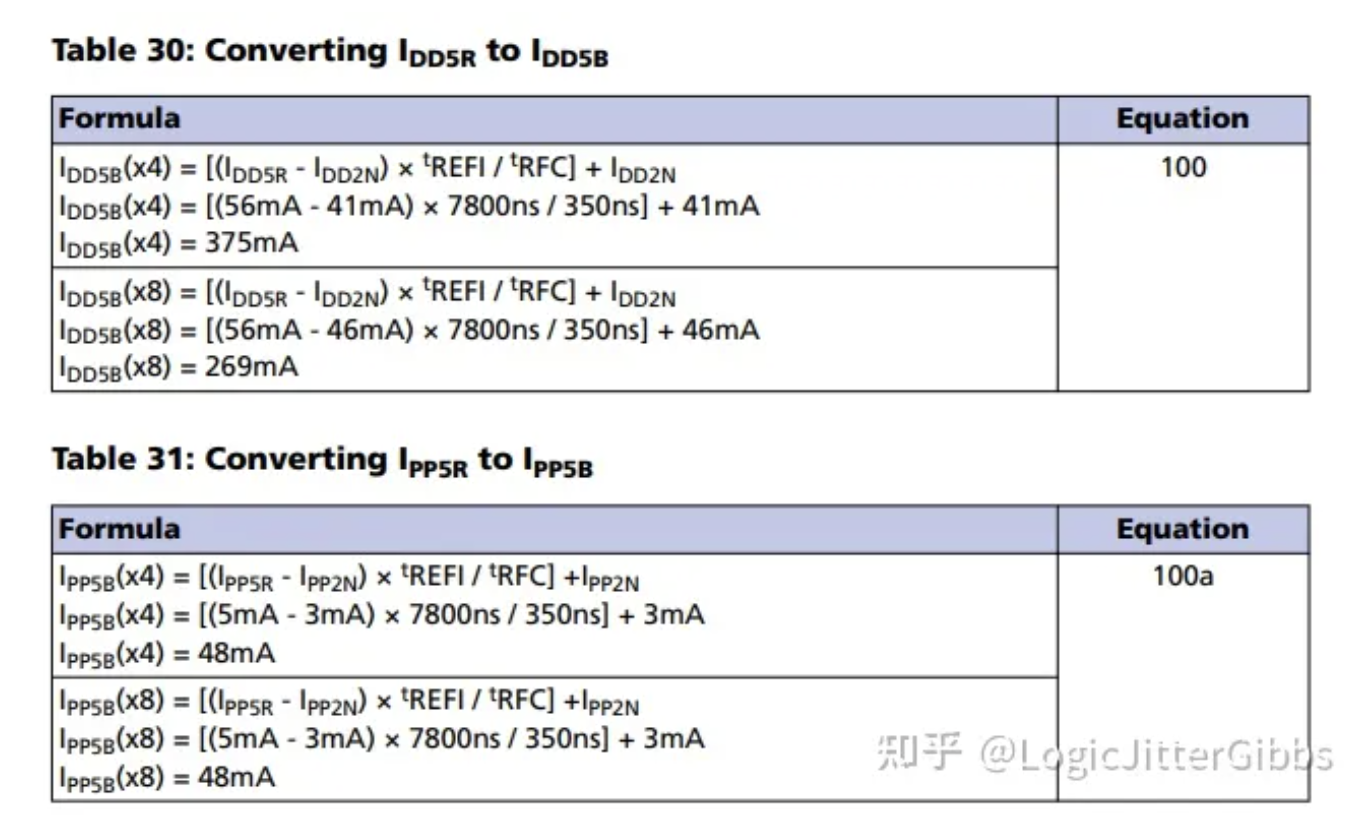

DDR4 SPEC 中与 refresh 相关的电流是 I_DD5B,I_DD5B 是 DRAM 在最小刷新命令间隔(Refresh-Refresh)下连续工作产生的 refresh 电流,刷新持续时间为 t_RFC(MIN)。在有些数据手册中用 I_DD5R 代替 I_DD5B,表 30 中的公式 100 是两者之间的转换关系。如果一个颗粒同时支持 x4 和 x8 模式,那么计算两者的数值,取其中较大的那个。

上述结果中还包括静态电流 I_DD3N,单独计算 refresh 功耗时要再减去 I_DD3N。

10 功耗计算调整

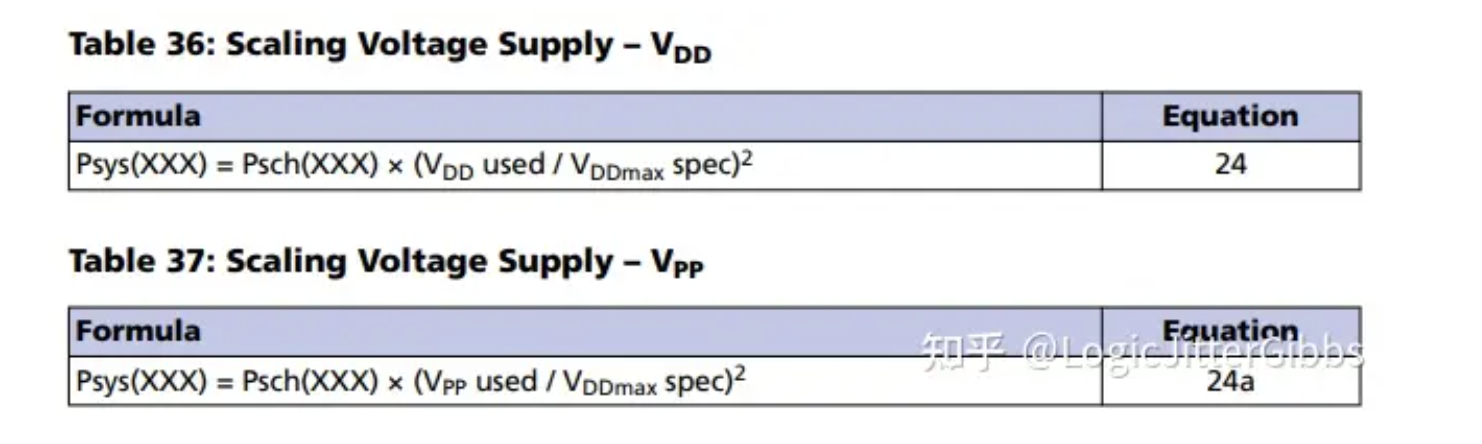

目前我们计算的系统功耗基于最恶劣的 VDD 电压,并且假设 DRAM 工作频率与数据手册中规定的完全一致,此时计算得到的功耗记为 P_sch。但实际系统有自己的电压和频率,需要调整计算 P_sys。

实际系统的 VDD 电压应该和标准 VDD 电压接近,需要把按 VDD_MAX 计算得到的 P_sch 按比例换算,IO 功耗因为计算的时候用的就是标准 VDD 电压,因此可以免除换算。

DRAM 功耗和电压是平方关系,这是因为大部分的功耗消耗在电容上:

P = CV^2f, 其中 C 代表内部电容大小,V 是供电电压,f 代表频率。

接下来是基于系统频率的功耗换算,在所有功耗中,Psch(PRE_PDN), Psch(ACT_PDN), Psch(ACT_STBY), Psch(PRE_STBY), Psch(WR) 以及 Psch(RD) 和频率相关,需要根据实际频率调整。而 Psch(REF) 与频率无关, Psch(ACT) 与实际的 ACT 命令之间的间隔有关,与时钟频率之间不是直接的关系。

频率调整时,直接把 Psch 乘以实际频率与 SPEC 频率之间的系数就可以得到 Psys。

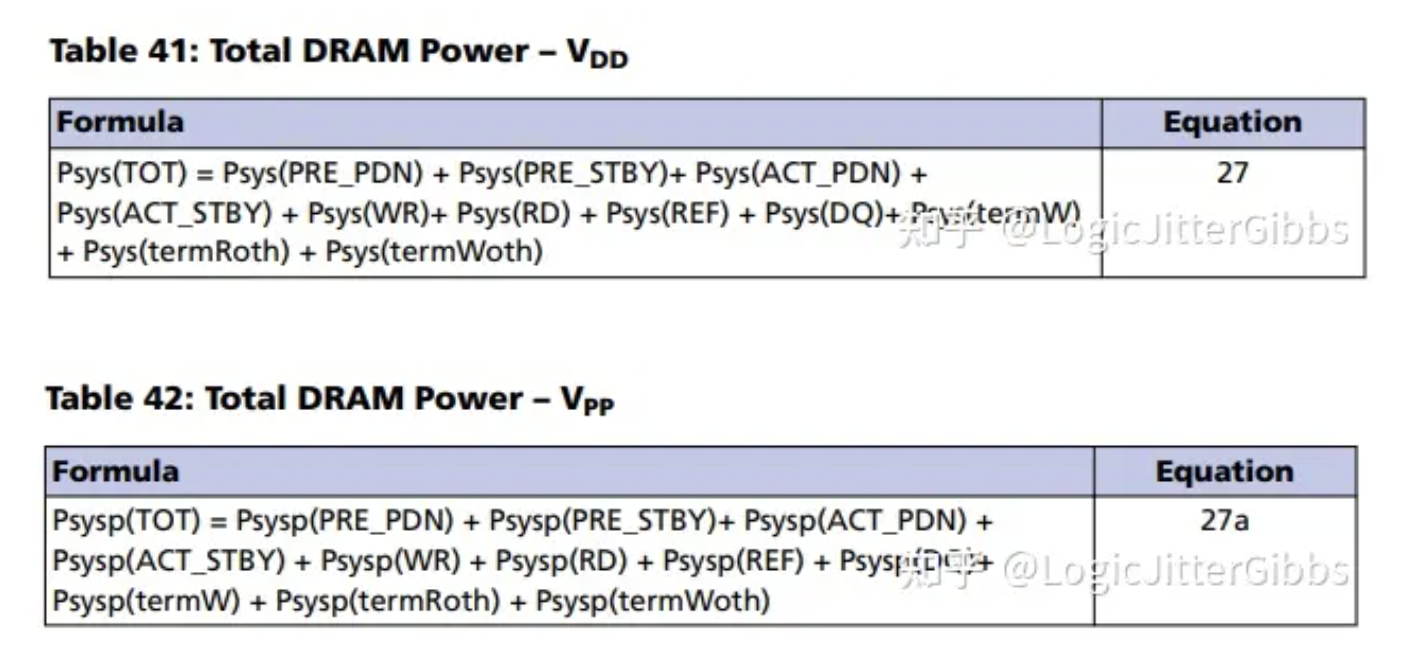

11 DRAM 整体功耗

我们已经准备好了 DRAM 各个部分的功耗数据,最后要做的就是把他们加到一起。

12 DDR4 功耗计算工具

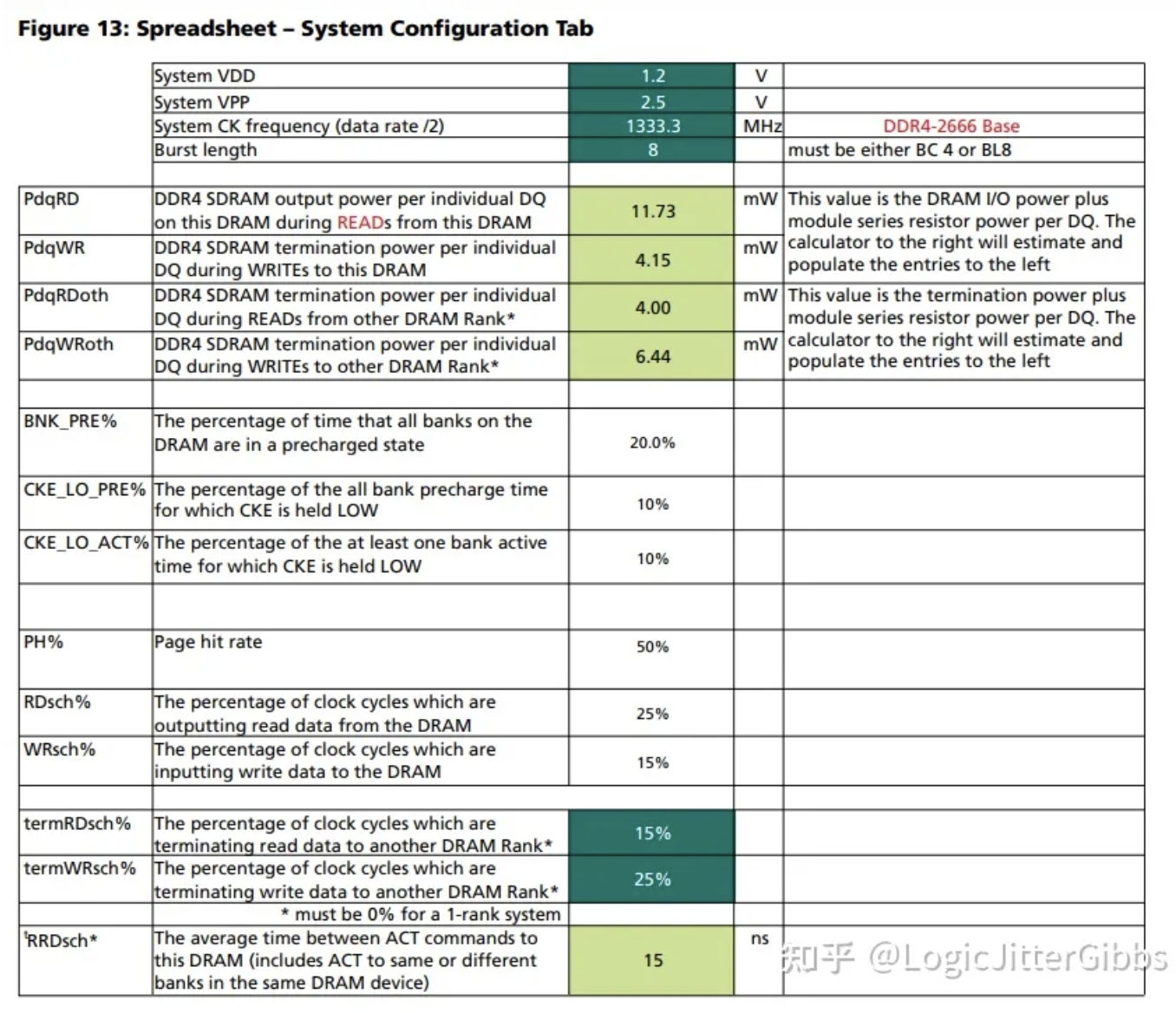

手算上述过程很费力的,因此 Micron 提供了一个在线辅助计算的工具 http://micron.com/systemcalc。本节是计算工具的一个简单教程。

首先选择 DRAM 型号,系统会自动罗列出该型号 DRAM 的参数。然后是输入系统的组成方式,包括 DRAM 容量,位宽,速度等级以及是否使能 DBI 等。接下来是输入系统的工作条件,包括实际的 VDD 电压和时钟频率,总线的各种利用率情况等,如图 13 所示。

最后,就可以在 Summary 页面显示计算的功耗了。

图 13- 系统配置输入表格

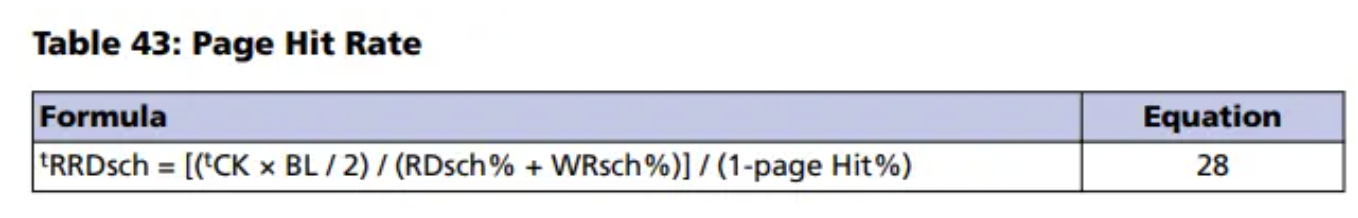

值得一提的是上图中的 Page hit rate 参数,用于计算 t_RRDsch。Page hit rate 表示访问打开状态行的读写命令占总读写命令的比例。表 43 是用 Page hit rate 计算 t_RRDsch 的公式,column-column 命令之间的间距 CtC 为 (tCK × burstlength / 2) / (RD%+WR%)。t_RRDsch 即 ACT-ACT 命令之间的间距为 CtC / (100% - PH%)。

13 数据手册中的标准电流

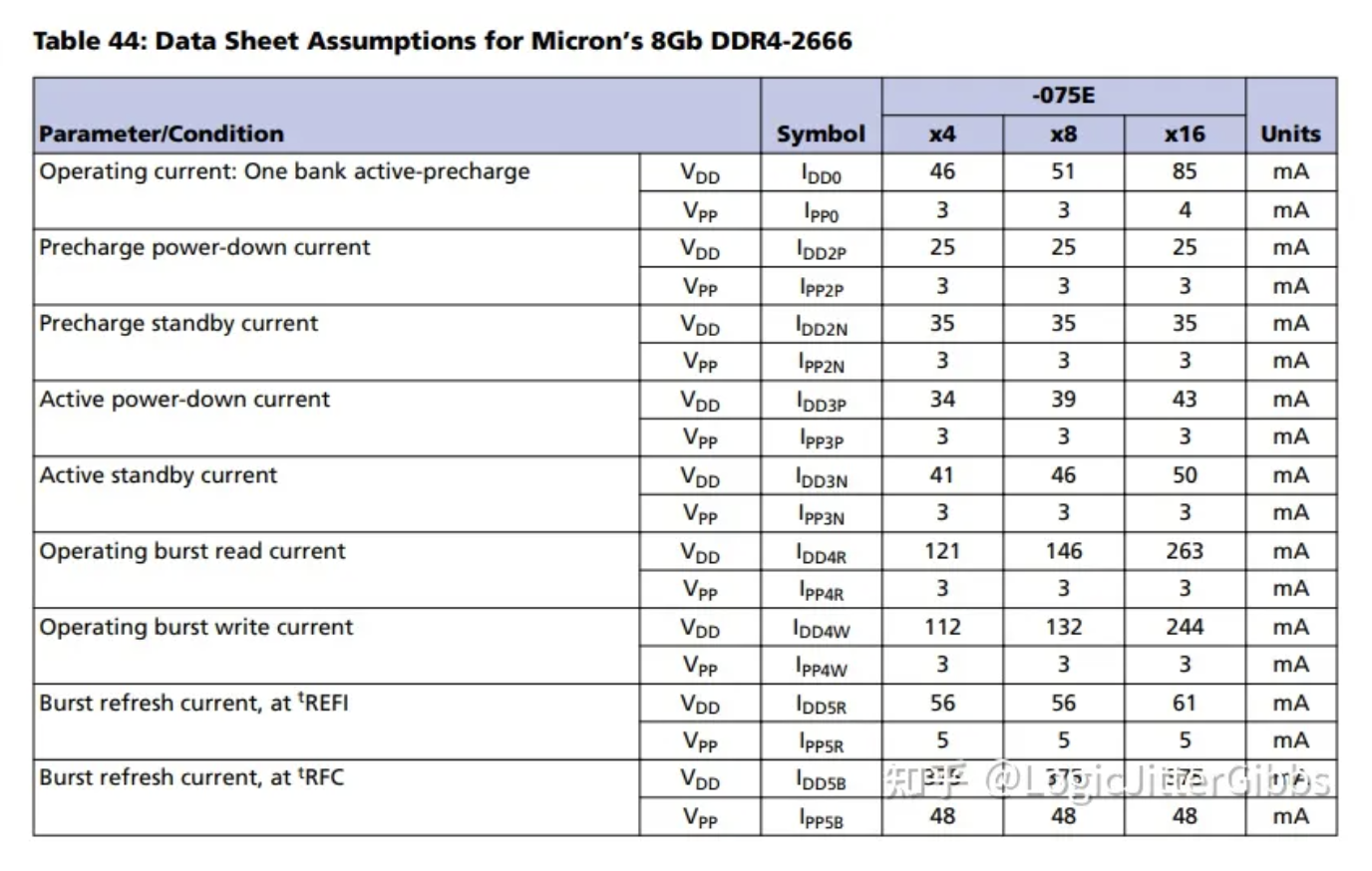

以 DD4-2666 为例,下图是数据手册中用于计算 DDR4 功耗的电流数值。

14 示例:使用 Power Spreadsheet 计算 DDR4 功耗的示例

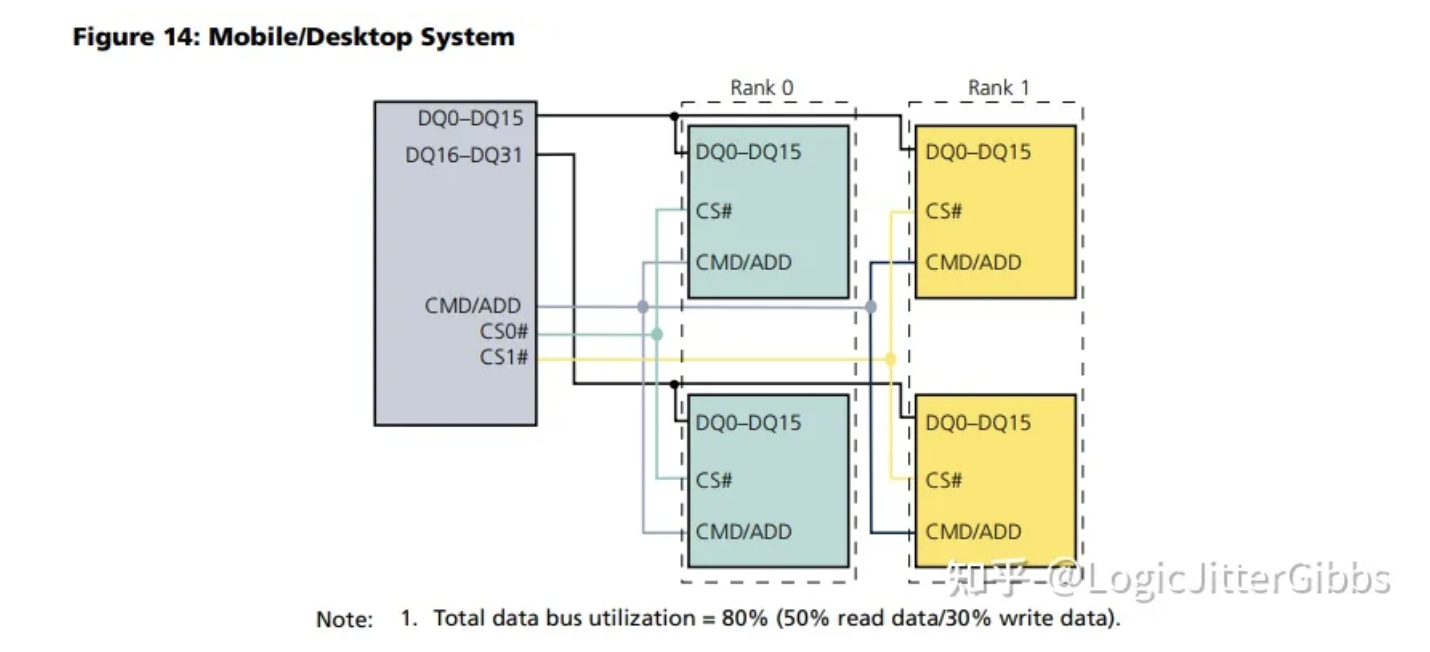

本节是一个计算系统中 DDR4 功耗的例子。系统结构如图 14 所示,是一个 2 rank,32bit 数据位宽的系统,连接有四片共 8Gb DDR4-2666 DRAM。图 14 中蓝色部分的控制器,驱动所有四个 DRAM 的控制/地址总线。两个 Rank 中分别连接到控制器两个独立的 CS 信号上,每个 Rank 有两个 x16 DRAM 颗粒,提供 32 比特数据位宽。

图 14- 一个 Mobile/Desktop 系统示例

示例中假设这个系统的总线利用率是 80%,其中 50% 的带宽是读数据,30% 的带宽是写数据,假设两个 Rank 被均匀访问,系统中所有的传输的 Burst length 都是 8,page hit 率是 50%。考虑到系统的带宽利用率比较高,假设没有 CKE 置低的时间,以及所有 Bank 20% 的时间处于 precharge 状态。

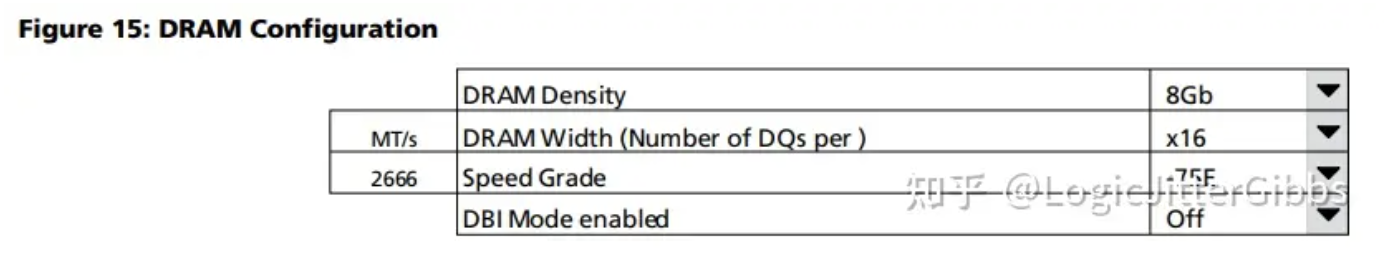

图 15- DRAM 配置信息填写

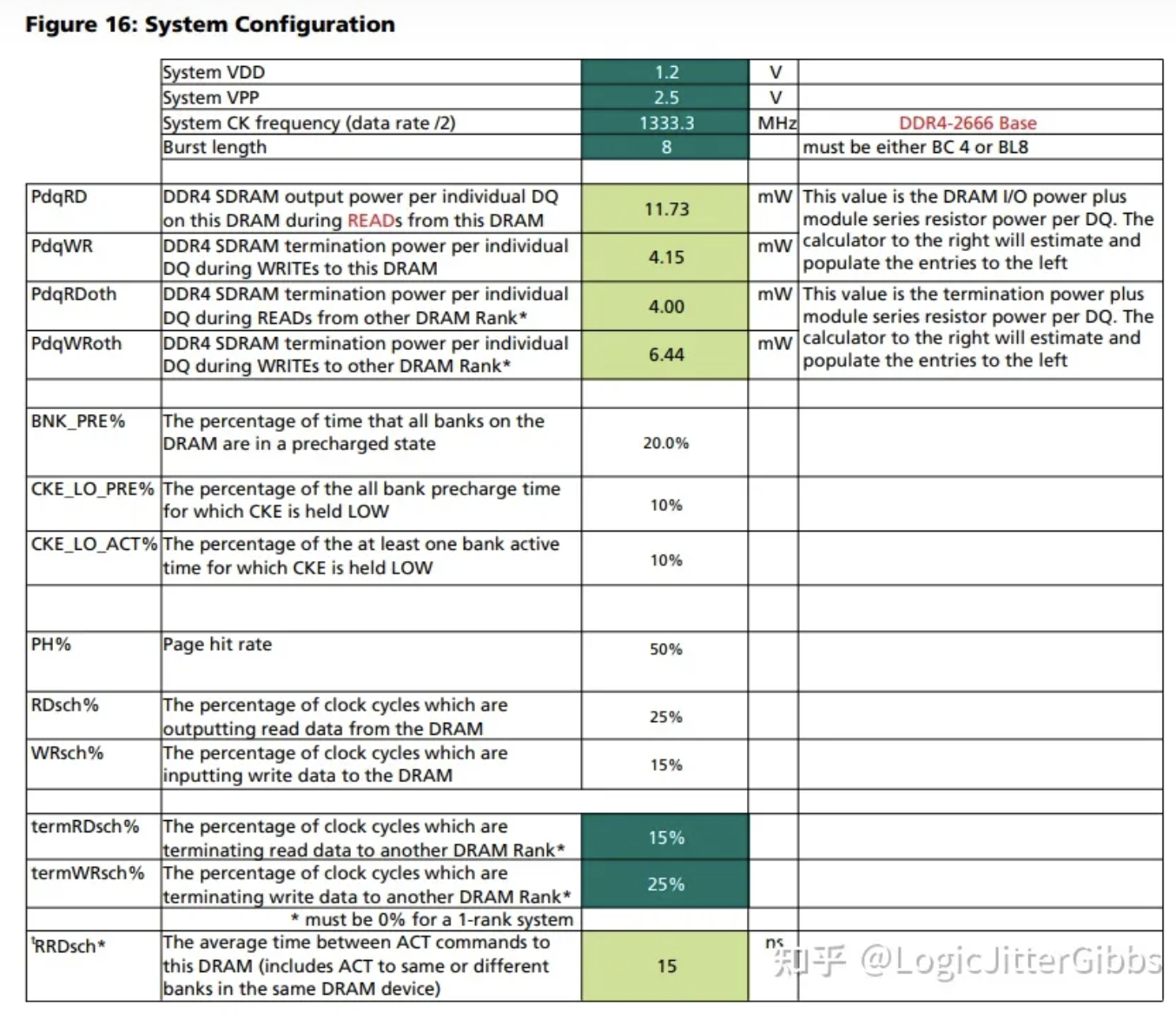

如图 15 填写系统配置信息之后,根据系统的情况填写图 16 中的系统配置信息。

由于这是一个双 Rank 系统,在两个 Rank 之间均分了流量,因此设定每个 DRAM 的读利用率为 25%,写利用率为 15%。基于设定的 PageHit 率,工具计算出 t_RRDsch = 15ns。

图 16- 系统配置信息

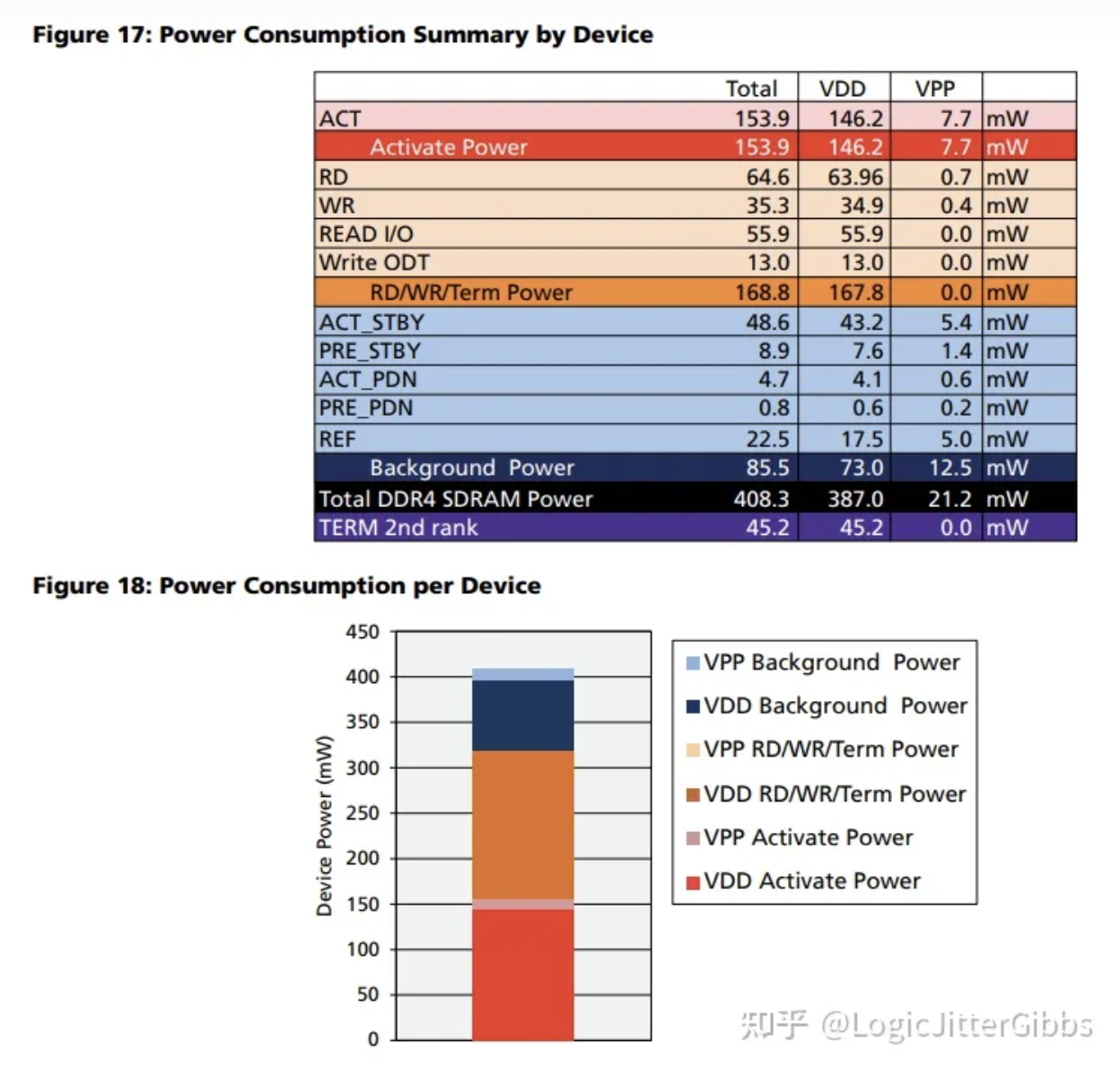

在输入所有系统配置之后,工具计算出各个子模块的功耗,如图 17 所示,每个 DRAM 颗粒消耗

- 85.5mW 背景功耗

- 153.9mW Row Activate 功耗

- 168.8mW 读写数据功耗

因此,每个 DRAM 颗粒总计消耗 408.3mW,整个系统四个 DRAM 颗粒共计消耗 1.63W。

图 17、18、19 DRAM 功耗计算结果

从上面三张图中可以发现,功耗中主要的组成部分是 ACT 功耗,占到总功耗大约三分之一,其次是读操作时的核心和 IO 功耗。因此,通过提高 page hit 率,减少 Row 的关闭和打开操作,能够最显著地降低 DRAM 功耗。

15 结论

数据手册很难告诉你一个 DRAM 具体消耗了多少功耗,但是,通过对 DRAM 器件功耗原理和数据手册的理解,我们可以基于实际的使用情况建立一个功耗模型。这个功耗模型可以帮助系统设计者实验多种访问压力下 DRAM 的功耗情况,可以通过更多或者更少地置低 CKE 或者调整数据序列等手段来调整系统的功耗。

总的来说,系统设计者通过这个功耗模型可以估计实际的 DRAM 功耗需求,调整系统设计和热设计预算,从而优化整个系统的性能。

原文:知乎

作者:LogicJitterGibbs

相关文章推荐

- DDR 学习时间 (Part C - 1):DFI 协议简介、演进和协议下载

- DDR 学习时间:学习 Micron DDR4 TN-40-07: DDR4 功耗估算 (1)

- 一些PCIE知识整理——PCIe体系的拓扑结构

- 一些PCIE知识整理——带宽计算

- 译文:DDR4 - Initialization, Training and Calibration

更多FPGA干货请关注FPGA的逻辑技术专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。