相关概念

传输速率为每秒传输量GT/s,而不是每秒位数Gbps,因为传输量包括不提供额外吞吐量的开销位; 比如 PCIe 1.x和PCIe 2.x使用8b / 10b编码方案,导致占用了20% (= 2/10)的原始信道带宽。

GT/s —— Giga transition per second (千兆传输/秒),即每一秒内传输的次数。重点在于描述物理层通信协议的速率属性,可以不和链路宽度等关联。

Gbps —— Giga Bits Per Second (千兆位/秒)。GT/s 与Gbps 之间不存在成比例的换算关系。

PCIE带宽计算

PCIe 吞吐量(可用带宽)计算方法:

吞吐量 = 传输速率 * 编码方案

PCIe2.0协议支持5.0GT/s,每一条Lane上支持每秒钟传输5G个bit;但是不代表每条Lane支持5Gbps的速率。

由于PCIe2.0的物理层协议采取的是8b/10b的编码方案。每传输8个bit需要发送10个bit。这多出的2个Bit并不是对上层有意义的信息。

那么, PCIe 2.0协议的每一条Lane支持 5 * 8 / 10 = 4 Gbps = 500 MB/s 的速率。

以一个PCIe 2.0 x8的通道为例,x8的可用带宽为 4 * 8 = 32 Gbps = 4 GB/s。

同理,PCI-e3.0 协议支持 8.0 GT/s, 即每一条Lane 上支持每秒钟内传输 8G个Bit。

而PCIe 3.0 的物理层协议中使用的是 128b/130b 的编码方案。 即每传输128个Bit,需要发送130个Bit。

那么, PCIe 3.0协议的每一条Lane支持 8 * 128 / 130 = 7.877 Gbps = 984.6 MB/s 的速率。

一个PCIe 3.0 x16的通道,x16 的可用带宽为 7.877 * 16 = 126.031 Gbps = 15.754 GB/s。

为应对各领域日益增长的超高速带宽需求,英特尔推出了全新的互联协议Compute EXpress Link(CXL),面向超极数据中心,高性能计算和AI等领域,可有效解决未来所遇到的负载瓶颈。

SSD的协议标准除了SATA,还有一个更先进的协议标准,就是PCIe。PCIe总线使用了高速差分总线,并采用了端到端的连接方式。

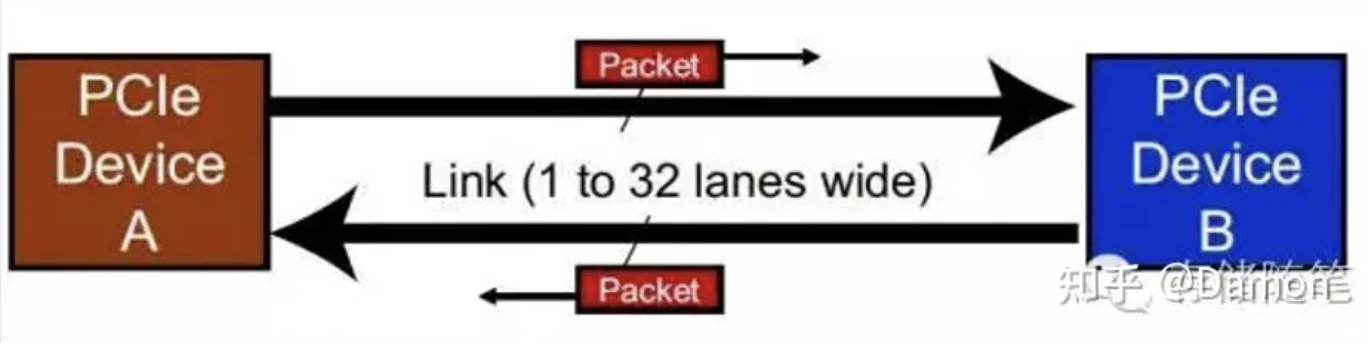

两个设备之间的的传输通道,称为Link,由1,2, 4, 8, 16, 32个Lane组成。Lane的数目代表Link的传输宽度(x1, x2, x4, x8, x16, x32)。

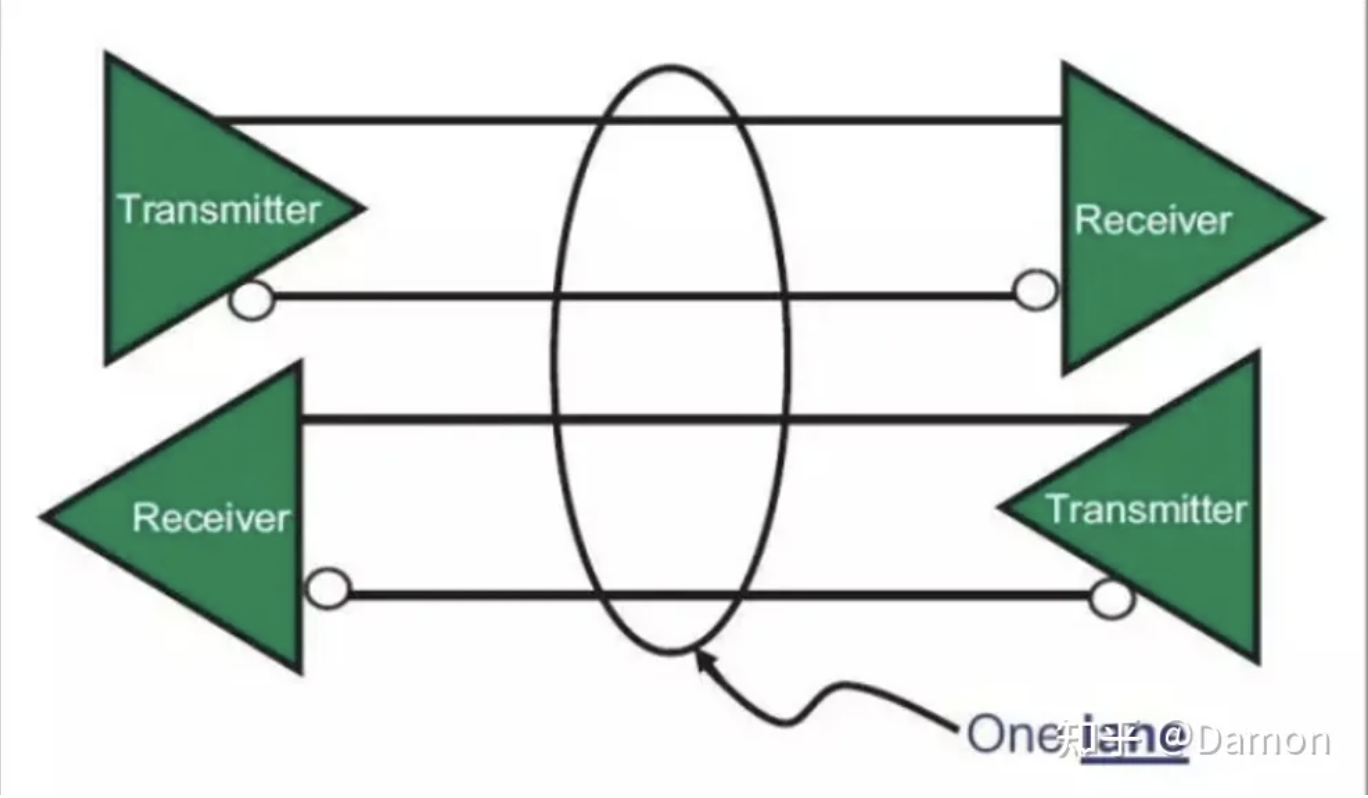

Lane是发送端与接收端之间的一个传输回路。由两组差分信号组成。如下图,

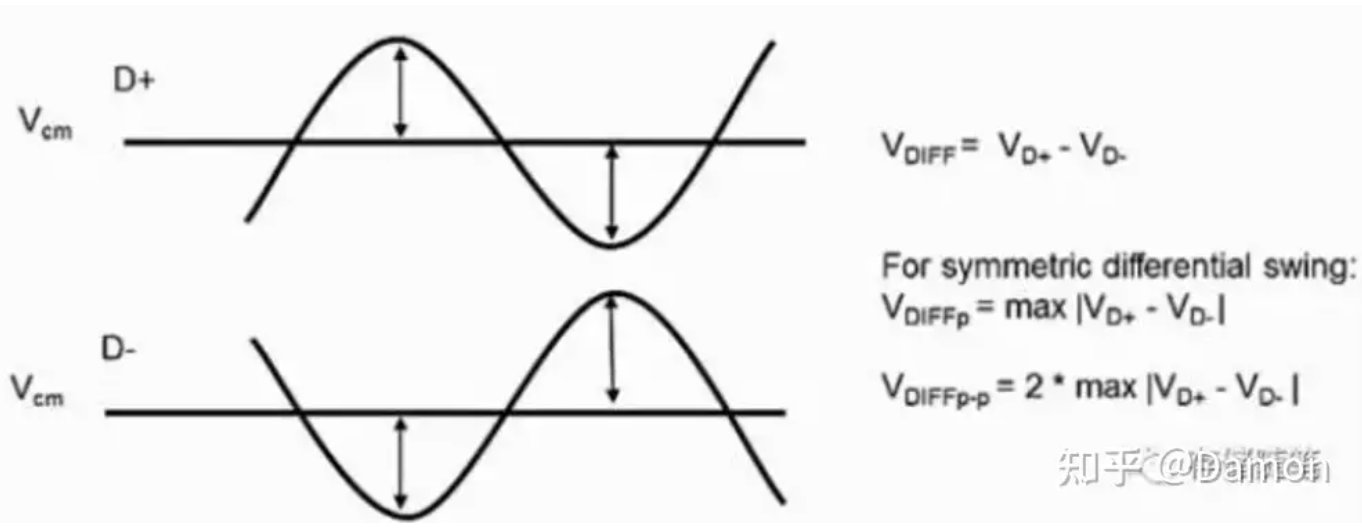

扩展:PCIe链路使用差分信号进行数据传送,一个差分信号由D+和D-两根信号组成,信号接收端通过比较这两个信号的差值,判断发送端发送的是逻辑“1”还是逻辑“0”。

与单端信号相比,差分信号抗干扰的能力更强,能有效抑制电磁干扰EMI(Electro Magnetic Interference)。

PCIe传输速率对比

Gen1/Gen2采用是8b/10b的编码,而Gen3之后则采用的是128b/130b的编码。

PCIe 的速度倍增减惯例与 PCIe 5.0 的发布保持一致。PCIe 5.0 使用自 PCIe 3.0 版以来的标准 128b/130b 编码方法,将在每个方向上提供 64 GB/秒的吞吐量。由于 PCIe 技术允许数据全双工双向流动,因此两个方向的总吞吐量加起来达到 128 GB/秒。

PCIe 3.0 之前的编码标准是 8b/10b,这意味着 8 位数据被编码并作为 10 位数字传输。这进而产生了 20% 的性能开销因子,将 2.5 GT/秒的原始比特传输速率降低到仅为 2.0 Gbit/秒的净带宽。这个更有效的 1.5% 开销因子在 PCIe 5.0 编码惯例中仍然有效。

PCIe总线物理链路间的数据传送使用基于时钟的同步传送机制,但是在物理链路上并没有时钟线,PCIe总线的接收端含通过PLL锁相环从接收报文中提取接收时钟,从而进行同步数据传递。

PCIe是一种封装分层协议,主要包括事务层(Transaction layer), 数据链路层(Data link layer)和物理层(Physical layer)。

在PCIe体系结构中,数据报文首先在设备的核心层(Device Core)中产生,然后再经过该设备的事务层(Transaction Layer)、数据链路层(Data Link Layer)和物理层(Physical Layer),最终发送出去。而接收端的数据也需要通过物理层、数据链路和事务层,并最终到达Device Core。

在一条PCIe链路中,这两个端口是完全对等的,分别连接发送与接收设备,而且一个PCIe链路的一端只能连接一个发送设备或者接收设备。因此PCIe链路必须使用Switch扩展PCIe链路后,才能连接多个设备。

原文:知乎

作者:Damon

相关文章推荐

- 译文:DDR4 - Initialization, Training and Calibration

- 快来看看用FPGA做的开源示波器(二)

- 【译文】 在综合中约束逻辑无关时钟

- 【译文】如何定义综合时序约束·目录

- [译文】DRAM Circuit Design: A Tutorial 前言与目录

更多FPGA干货请关注FPGA的逻辑技术专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。