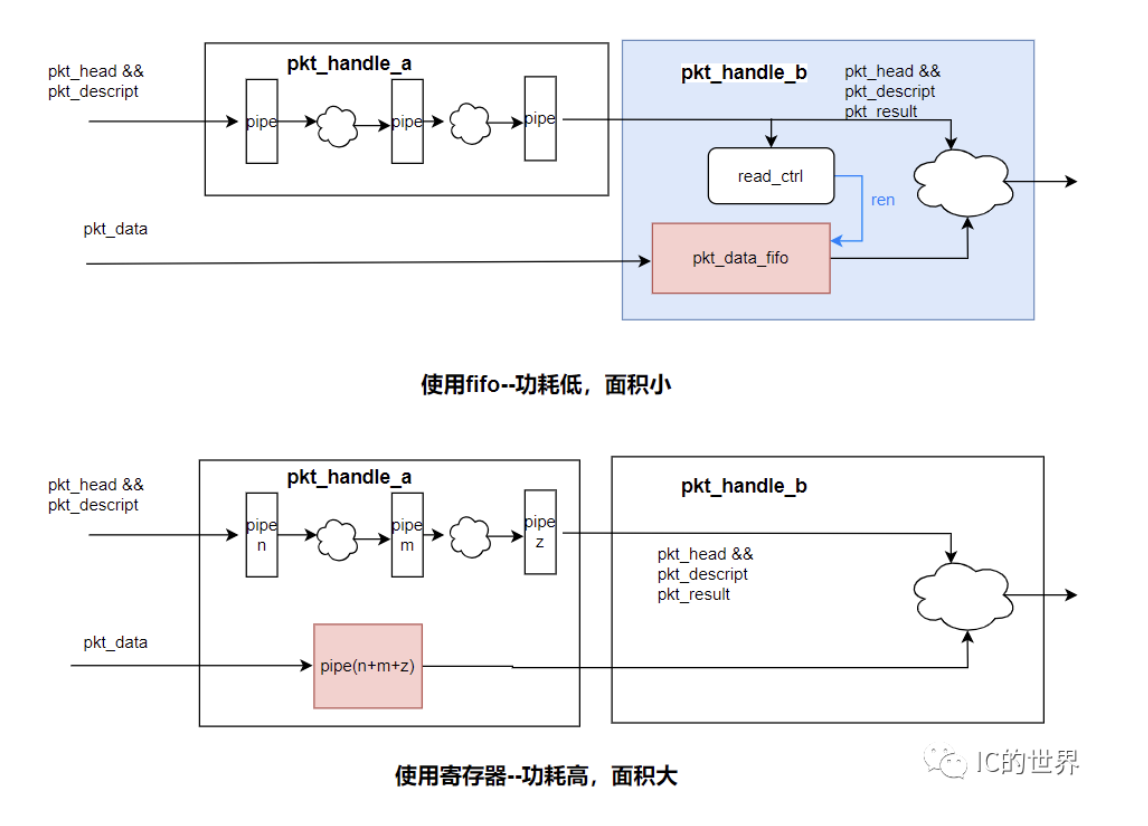

本案例中,我们讲解一种使用fifo节约资源,降低功耗的设计。如图所示,pkt_handle_a模块是对数据包进行处理的模块,但是不需要包数据(pkt_data),而仅仅需要根据包头(pkt_header)和包描述符(pkt_descript)。这时候该怎么设计呢?可以采用如下方式:在pkt_handle_b模块使用一个fifo用于存储包数据(pkt_data),pkt_handle_a模块的输入仅仅只有包头和包描述符,pkt_handle_a模块完成包处理后新增处包处理结果(pkt_result),送到pkt_handle_b模块,pkt_handle_b模块在需要读出包数据(pkt_data)的时候才将fifo内的数据读出。

在包数据位宽较大,pkt_handle_a流水拍数较大时,相对于使用寄存器对包数据(pkt_data)进行打拍,使用fifo存储包数据(pkt_data)的实现方式更有优势,功耗低,面积小。虽然从存储bit位角度计算两种设计需要的bit位几乎相同,但是相对于寄存器,底层用ram实现的fifo面积更小,功耗更低。

pkt_handle_a和pkt_handle_b之间可能存在更多的模块,数据流水可能长达几十到上百个周期,因此流水拍数越大,节约面积,降低功耗的效果越明显。

作者:IC小鸽

文章来源:IC的世界

推荐阅读

更多IC设计干货请关注IC设计专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。