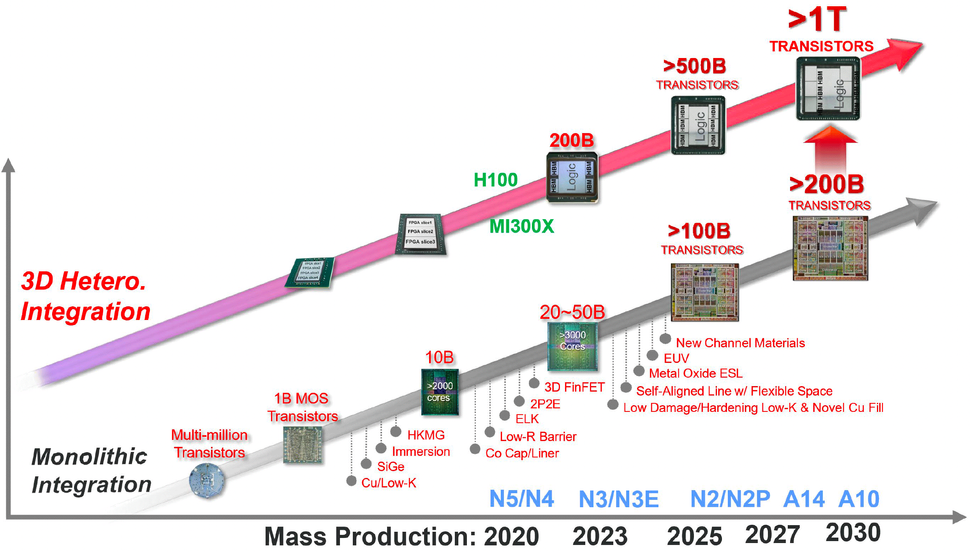

集微网消息,在IEEE国际电子元件会议(IEDM)上,台积电制定了提供包含1万亿个晶体管的多芯片封装路线,就像英特尔去年透露的那样。这些庞然大物将来自于单个芯片封装上的3D封装Chiplet(小芯片)集合,但台积电也在致力于开发在单片硅上包含2000亿个晶体管的芯片。为了实现这一目标,该公司重申正在致力于2nm级N2和N2P生产节点以及1.4nm级A14和1nm级A10制造工艺,预计将于2030年完成。

此外,台积电预计封装技术(CoWoS、InFO、SoIC等)将取得进步,使其能够在2030年左右构建封装超过1万亿个晶体管的大规模多芯片解决方案。

IEDM会议上的台积电幻灯片预见封装技术的进步

近年来,由于芯片制造商面临技术和财务挑战,前沿工艺技术的发展有所放缓。台积电与其他公司面临着同样的挑战,但台积电表示有信心,将能够在未来五到六年内在性能、功耗和晶体管密度方面提升其生产节点,会陆续推出2nm、1.4nm和1nm节点。

英伟达的含有800亿个晶体管的GH100是市场上最复杂的单片处理器之一,根据台积电的说法,很快就会有更复杂的单片芯片,拥有超过1000亿个晶体管。但构建如此大型的处理器变得越来越复杂和昂贵,因此许多公司选择多芯片设计。例如,AMD的Instinct MI300X和英特尔的Ponte Vecchio由数十个小芯片组成。

据台积电称,这种趋势将持续下去,几年后,我们将看到由超过1万亿个晶体管组成的多芯片解决方案。但与此同时,单片芯片将继续变得复杂,根据台积电在IEDM上的演讲,我们将看到拥有多达2000亿个晶体管的单片处理器。

台积电及其客户必须同步开发逻辑技术和封装技术,前者为后者提供密度改进,这就是台积电将生产节点的演变和封装技术都包含在同一张幻灯片上的原因。