Chisel (Constructing Hardware in a Scala Embedded Language) 是一种用于硬件设计的高级语言,相比于传统的硬件描述语言如Verilog和VHDL,Chisel 有多个显著的优势,主要体现在设计的抽象级别、重用性、测试能力和开发效率上。下面我们通过具体案例来说明这些优势。

1. 高级抽象和函数式编程

优势:Chisel允许使用高级抽象和函数式编程范式来设计硬件,这使得代码更加简洁、易于理解和维护。设计者可以定义高层次的生成器和组件,通过参数化生成不同配置的硬件模块。

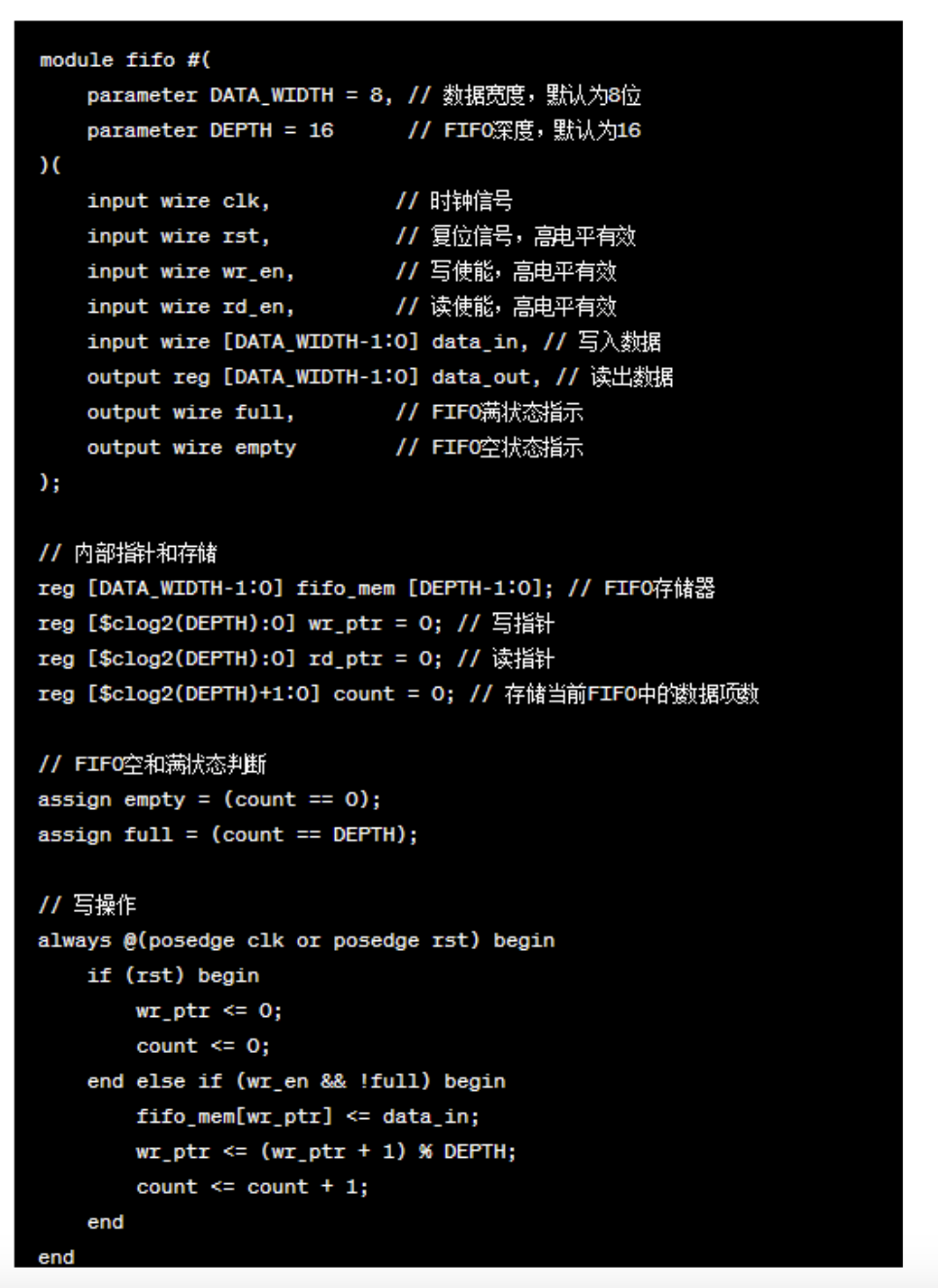

案例:设计一个参数化的FIFO队列,根据不同的需求调整其深度和宽度。

- Verilog:在Verilog中实现这样的参数化设计需要使用generate语句和参数传递,代码可能较为冗长并且难以理解。

- Chisel:在Chisel中,可以直接利用Scala的函数和类来实现这种参数化,代码更加直观和灵活。

2. 设计重用

优势:Chisel的对象导向特性使得代码重用更加方便。设计者可以创建可复用的模块和库,提高开发效率。

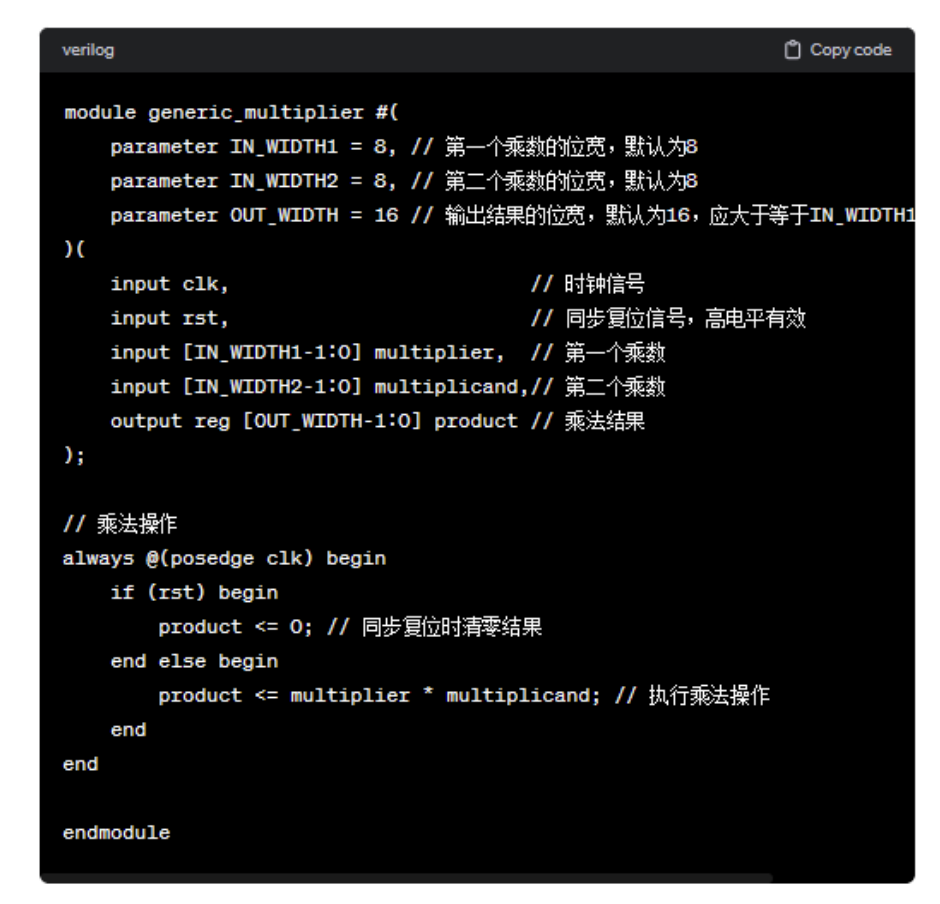

案例:创建一个通用的乘法器模块,可以被不同的DSP(数字信号处理)组件复用。

- Verilog:在Verilog中,代码重用通常依赖于复制粘贴,这可能导致代码冗余和维护困难。

- Chisel:在Chisel中,可以定义一个乘法器类,然后在不同的DSP组件中实例化该类。

3. 测试和验证

优势:Chisel提供了强大的测试框架,使得硬件的测试和验证更加灵活和自动化。

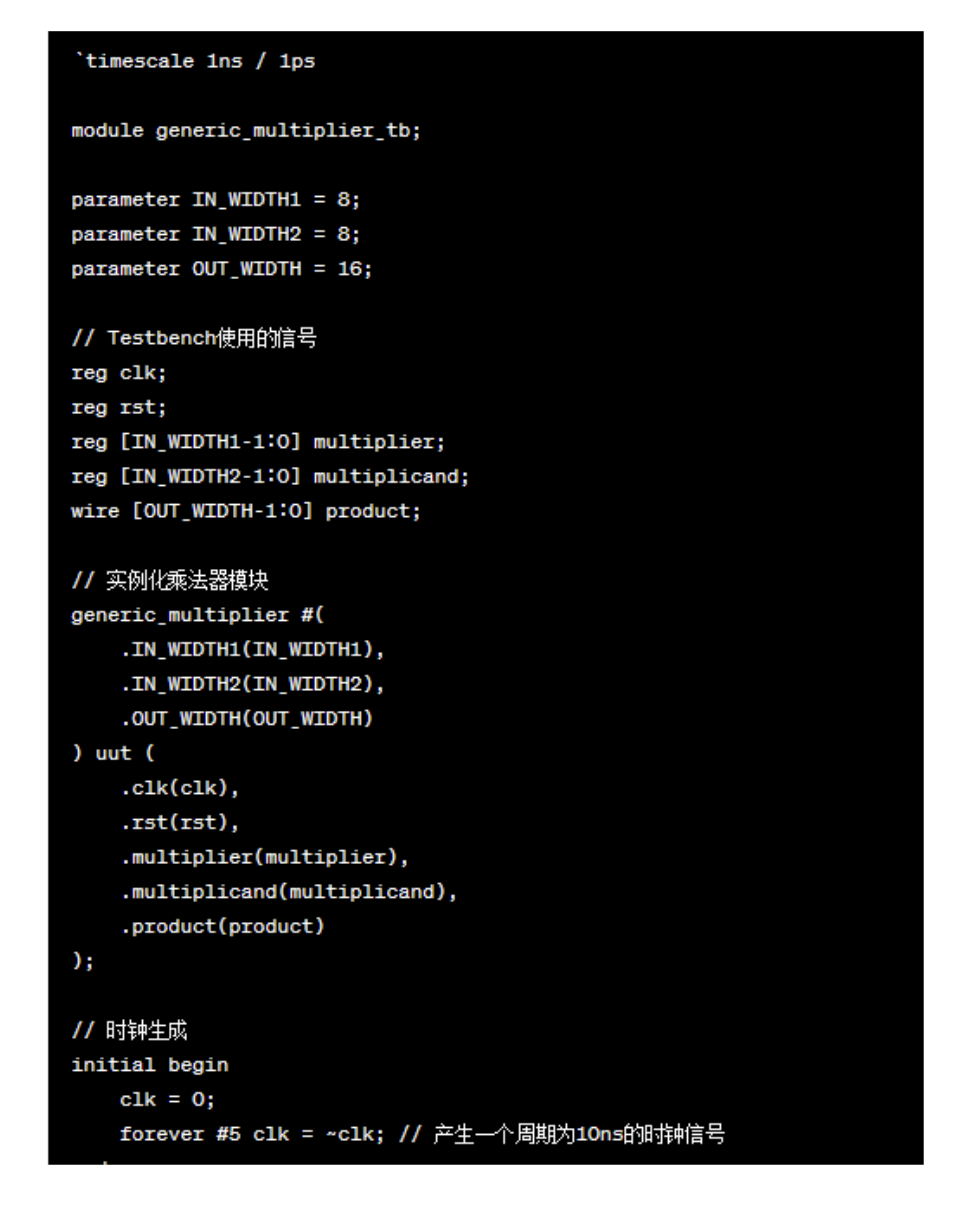

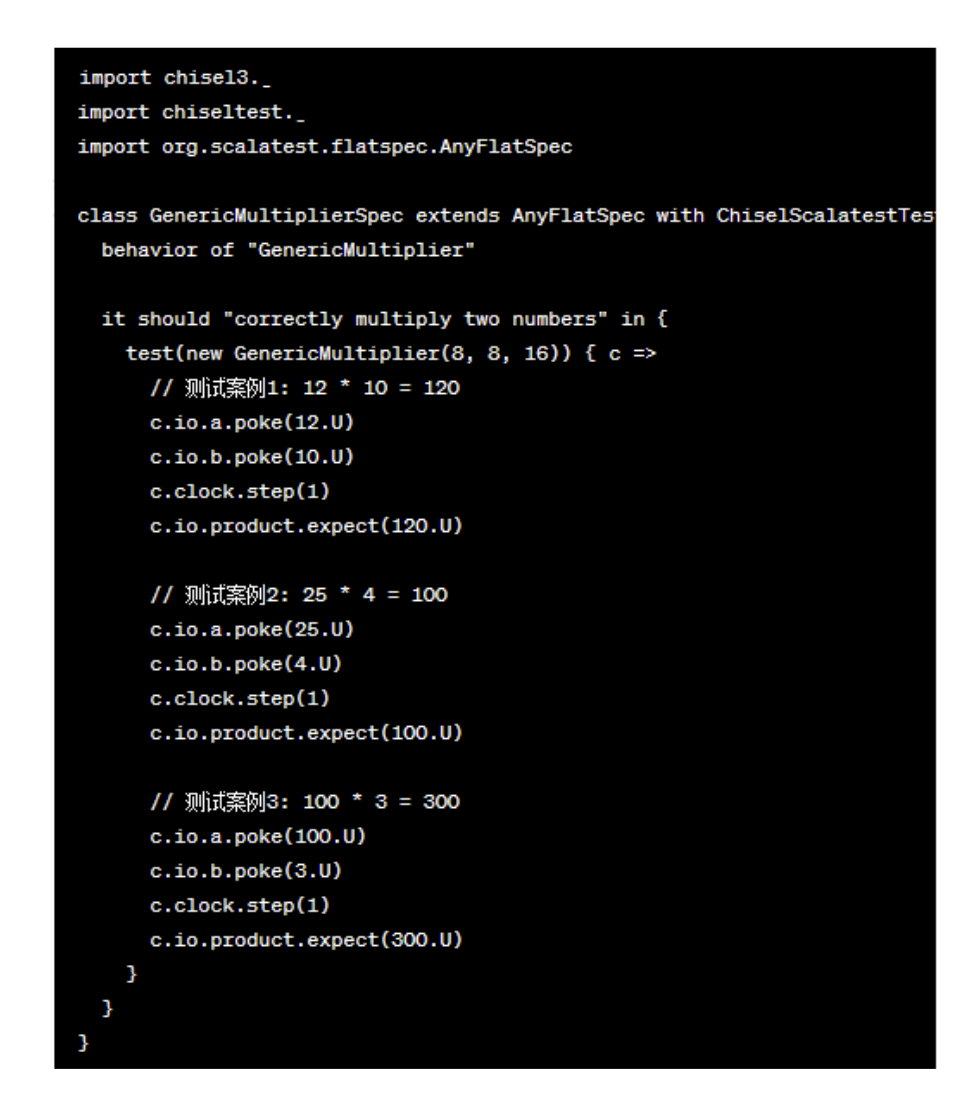

案例:对上述乘法器模块进行单元测试。

- Verilog:测试通常需要编写测试平台(testbench),使用特定的测试语言(如SystemVerilog)。

- Chisel:可以直接使用Scala编写测试代码,利用ChiselTest框架进行单元测试。

4. 开发效率和迭代速度

优势:Chisel的高级特性和Scala语言的强大功能,加上强类型系统,可以提高硬件设计的开发效率和迭代速度。

案例:快速原型开发和迭代一个复杂的数字系统,如CPU设计。

- Verilog:在Verilog中,修改和迭代设计可能较为缓慢,因为语言的低级特性限制了快速原型的能力。

- Chisel:可以利用Chisel的高级抽象和参数化设计快速迭代原型,同时保证设计的正确性。

综上,Chisel提供了比Verilog更高级的设计抽象、更好的代码重用性、更强大的测试能力和更高的开发效率。这些优势使得Chisel在某些场景下成为更优的硬件描述语言选择。

有哪些开源的chisel 项目呢?

1. Rocket Chip Generator

- 描述:一个高度参数化的SoC生成器,包括RISC-V处理器核心、缓存、内存控制器等。

- GitHub:https://github.com/chipsalliance/rocket-chip

2. Chisel3

- 描述:Chisel3本身就是一个开源项目,提供硬件设计的语言和编译框架。

- GitHub:https://github.com/chipsalliance/chisel3

3. FIRRTL

- 描述:灵活的中间表示用于RTL。FIRRTL代表“Flexible Intermediate Representation for RTL”,是Chisel生成的中间表示,用于进一步的转换和优化。

- GitHub:https://github.com/chipsalliance/firrtl

4. BOOM (Berkeley Out-of-Order Machine)

- 描述:一个高性能、可扩展、开源的RISC-V处理器,支持乱序执行。

- GitHub:https://github.com/riscv-boom/riscv-boom

5. Sodor

- 描述:一组教学用的RISC-V核心,包括从简单的单周期核心到更复杂的流水线设计。

- GitHub:https://github.com/librecores/riscv-sodor

6. Treadle

- 描述:Chisel的FIRRTL执行引擎,一个FIRRTL模拟器。

- GitHub:https://github.com/chipsalliance/treadle

7. Chisel DSP

- 描述:数字信号处理(DSP)库,专为使用Chisel进行硬件设计的DSP应用开发。

- GitHub:https://github.com/ucb-bar/dsptools

8. SpinalHDL

- 备注:虽然不是用Chisel写的,但SpinalHDL是一个类似于Chisel的硬件描述语言,也是基于Scala,提供了类似的高级抽象和功能。值得一提作为Chisel社区的相关项目。

- GitHub:https://github.com/SpinalHDL/SpinalHDL

作者:处芯积律

文章来源:处芯积虑

推荐阅读

- 标准延迟文件和时序报告中的delay value的一致性研究

- 老李带你看菜谱— stx_cookbook 之 加法器 (二)

- 老李带你看菜谱— stx_cookbook 之 加法器 (一)

- 数字IC设计中的update io clock latency

- 你还不会gvim正则表达式???来,一文搞懂!

更多IC设计干货请关注IC设计专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。