往期错误案例

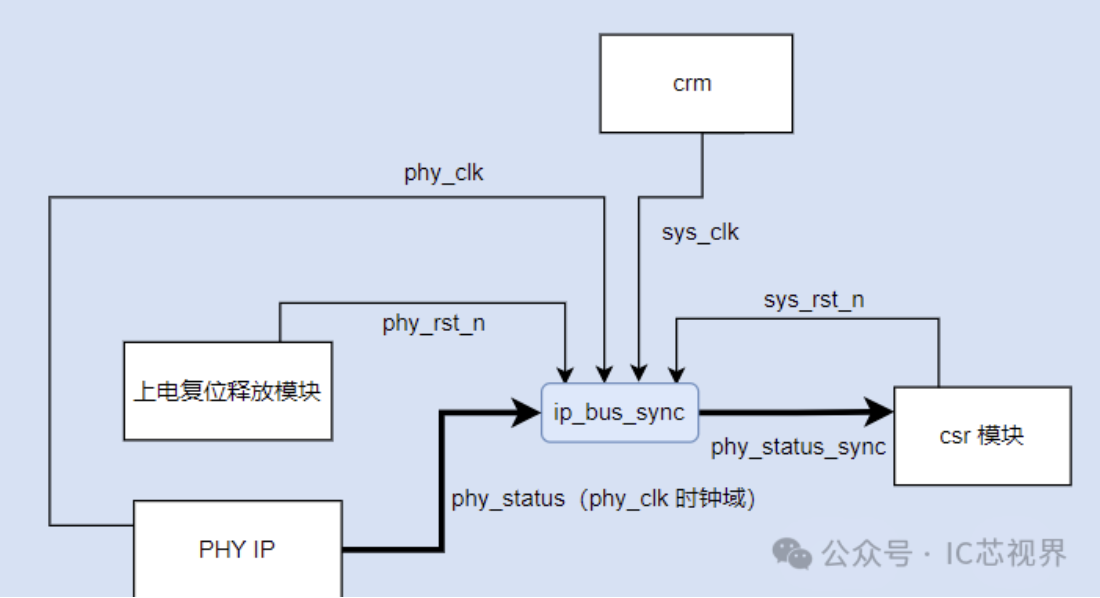

本文将介绍一个跨时钟错误的案例如图所示,phy_status作为一个多bit的phy_clk时钟域的信号,需要输入csr模块作为一个可读状态寄存器,目的是方便debug,而csr模块是sys_clk时钟域,此时phy_status需要进行跨时钟,得到sys_clk时钟域的phy_status_sync送到csr模块。

phy_rst_n是由上电复位释放模块产生的phy_clk时钟域的复位信号,在上电处理流程的初期phy_rst_n一直是0,处于复位状态,上电解复位流程进行到一定阶段后才会将phy_rst_n置为1。

ip_bus_sync跨时钟模块接口信号如下:

本模块的特点就是只有输入数据,没有vld信号。

phy_clk作为源时钟(i_src_clk),而phy_rst_n作为源时钟域复位信号(i_src_rst_n)。

sys_clk作为目的时钟(i_dst_clk),而sys_rst_n作为源时钟域复位信号(i_dst_rst_n)。

NOTE: 需要注意的是在在源时钟复位phy_rst_n为0时,输出的o_dst_dout(phy_status_sync)是跨时钟模块Ip_bus_sync的复位值(每bit都是0)

错误设计:设计中将phy_status作为一个可读状态寄存器,本意是想在上电解复位流程出现异常的时候,能够读出phy_status的数值,从而进行分析上电流程异常的原因。而在部分场景中,一旦phy_rst_n没有从0跳变成1时,此时phy_status_sync为0,无法获取phy_status的真实数值 。

正确设计:本文场景中应该采用无复位的跨时钟模块进行实现,如果存在可用的无复位多bit跨时钟模块,可以直接采用,否则可以考虑采用多个无复位的bit跨时钟模块实现。虽然采用多个无复位的bit跨时钟模块实现多bit跨时钟可能存在重汇聚问题,但是此场景中,一旦出现上电解复位异常,phy_status信号通常是处于稳定状态,多bit跨时钟重汇聚问题将不会存在。

作者:IC小鸽

文章来源:IC芯视界

推荐阅读

- ISSCC 2024: 三星利用对称马赛克架构将 DDR5 容量翻倍

- IC最新最全EDA虚拟机分享(RedHat7.9)

- IC设计:ram的折叠设计

- PCIE定位:PCIe需要的debug设计

- 工作6年半,模拟IC心得感悟(网友分享)

更多IC设计干货请关注IC设计专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。