当PCIe出现链路不稳定时,如何进行进行问题定位。本文描述的场景:EP PCIe 最高速率为gen4模式,ltssm状态机无法持续稳定在L0状态。

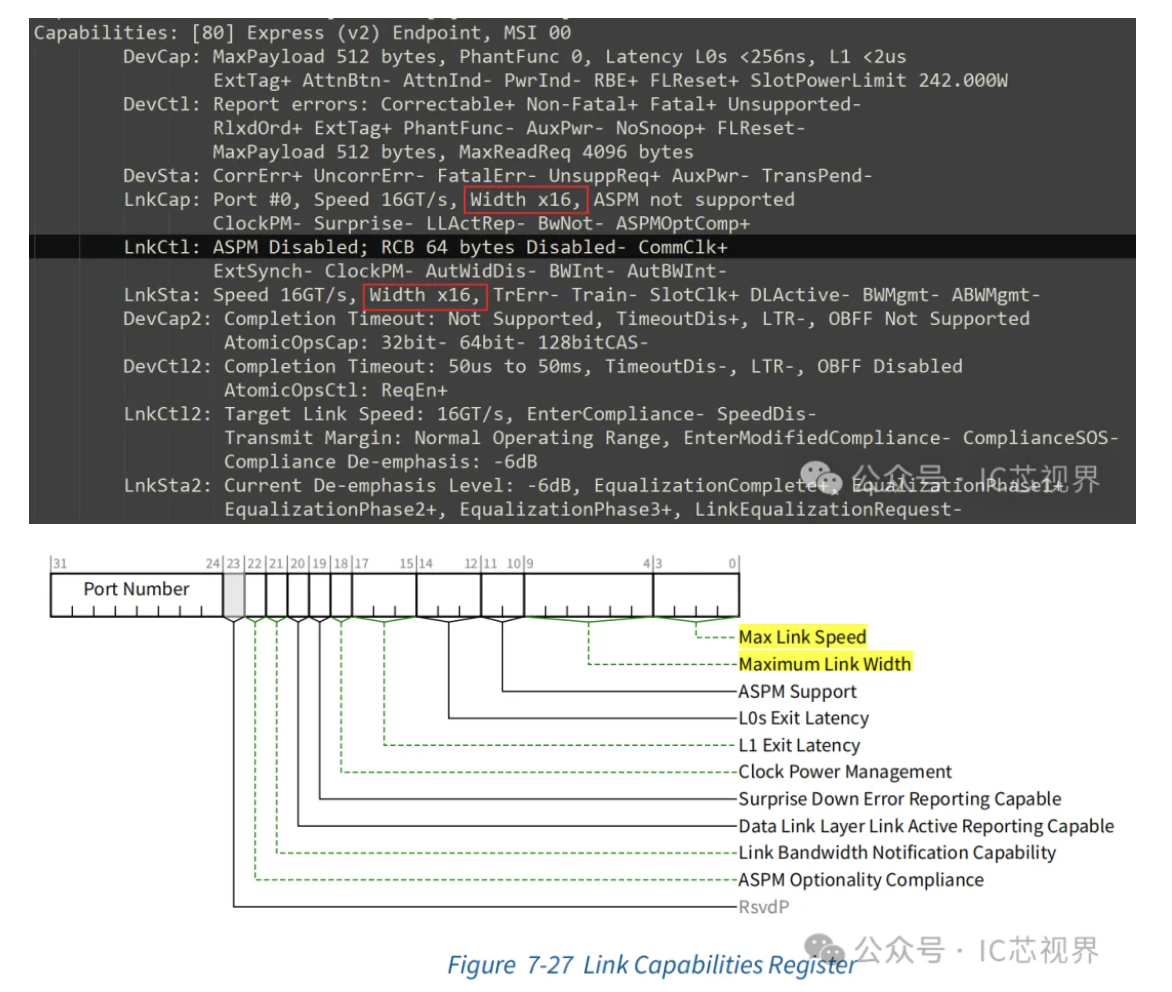

1.使用lspci观察配置空间的状态寄存器

使用lspci查看Endpoint(EP)和downstream port(DSP)的配置空间,两者都要看,方便定位问题出现在Endpoint的TX侧链路还是RX侧链路。重点看配置空间的状态寄存器,状态寄存器记录了曾经发生的错误状态。

NOTE: 如下案例中的状态位支持写1清零,可以通过setpci 命令将状态位清零,观察错误状态是否再次置1。

setpci -s 1a:00.0 110.L=FFFFFFFF //将bdf为1a:00.0的0x110地址的寄存器写全1清零,对应图1-2中的CESta状态寄存器。

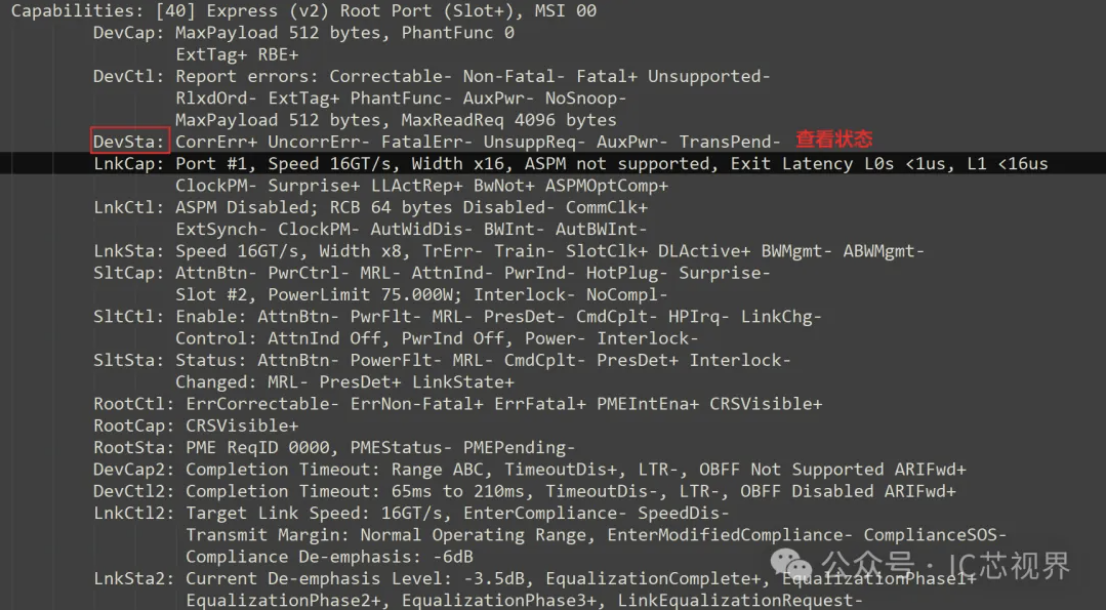

1.1.看device status寄存器

下图是DSP的device status寄存器,可以发现存在可纠正错误(CorrErr+)。

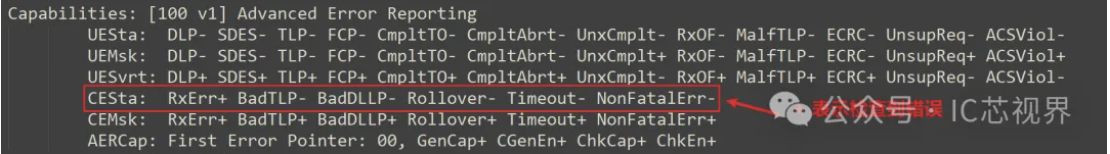

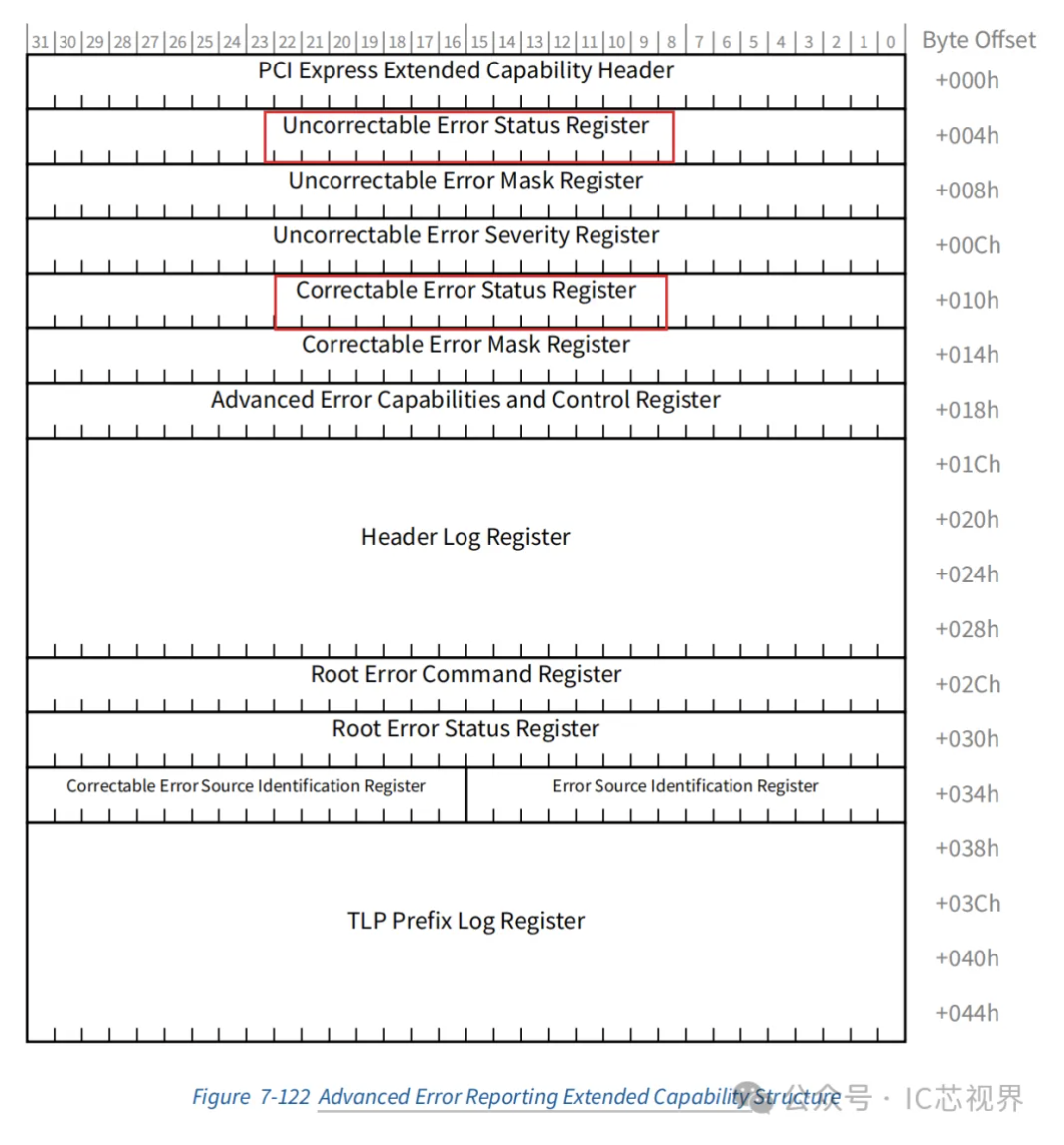

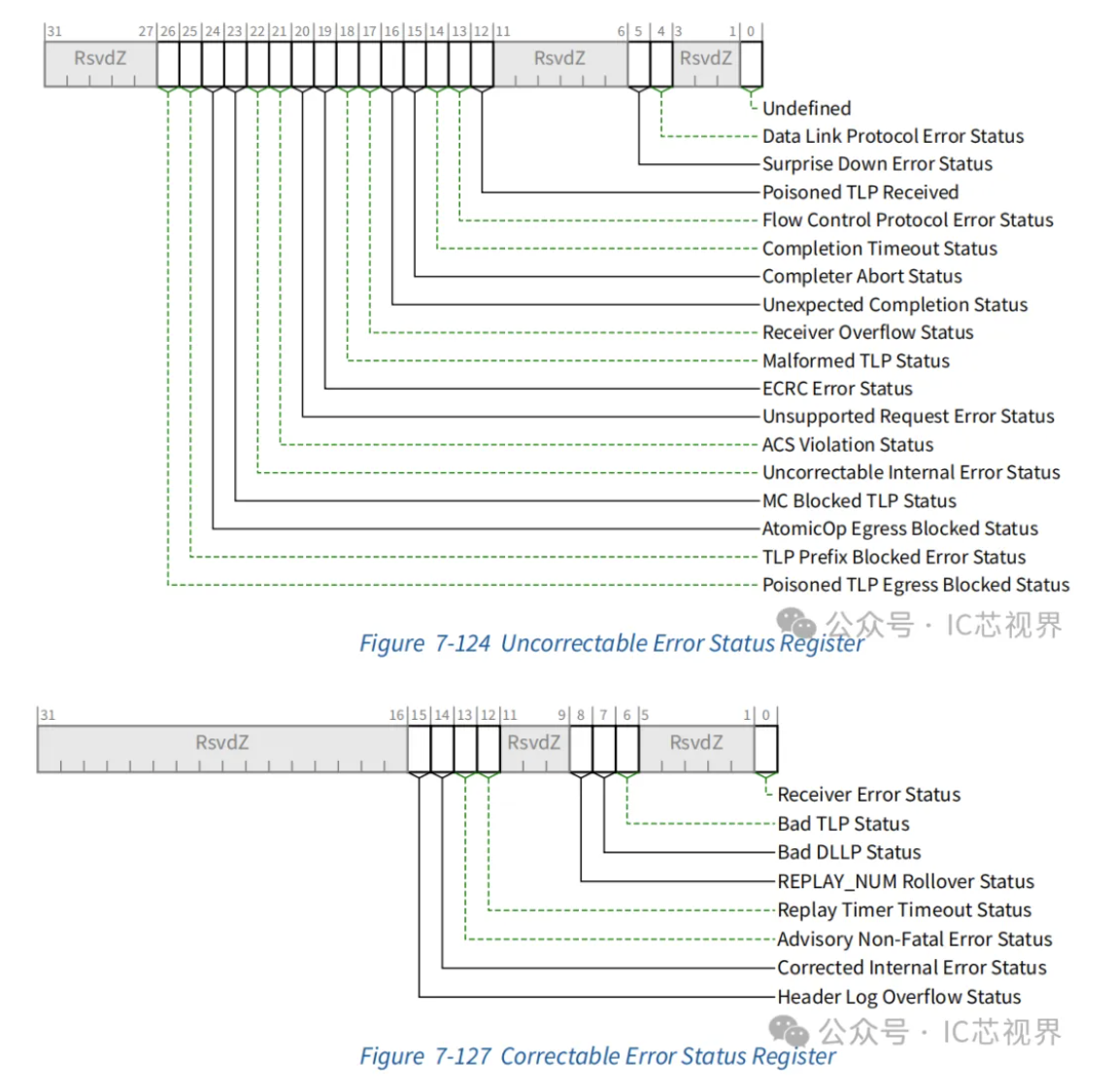

1.2.看AER的状态寄存器

Advanced Error Reporting能够提供更详细的异常状态记录,可以重点看Uncorrectable Error Status Register(UESta) 和Correctable Error Status Register(CESta),UESta和CESta都提供了详细的错误分类,例如CESta就支持如下错误记录:Receiver Error Status、Bad TLP Status、Bad DLLP Status、REPLAY_NUM Rollover Status、Replay Timer Timeout Status、Advisory Non-Fatal Error Status、Corrected Internal Error Status。

图1-2:AER能力结构状态

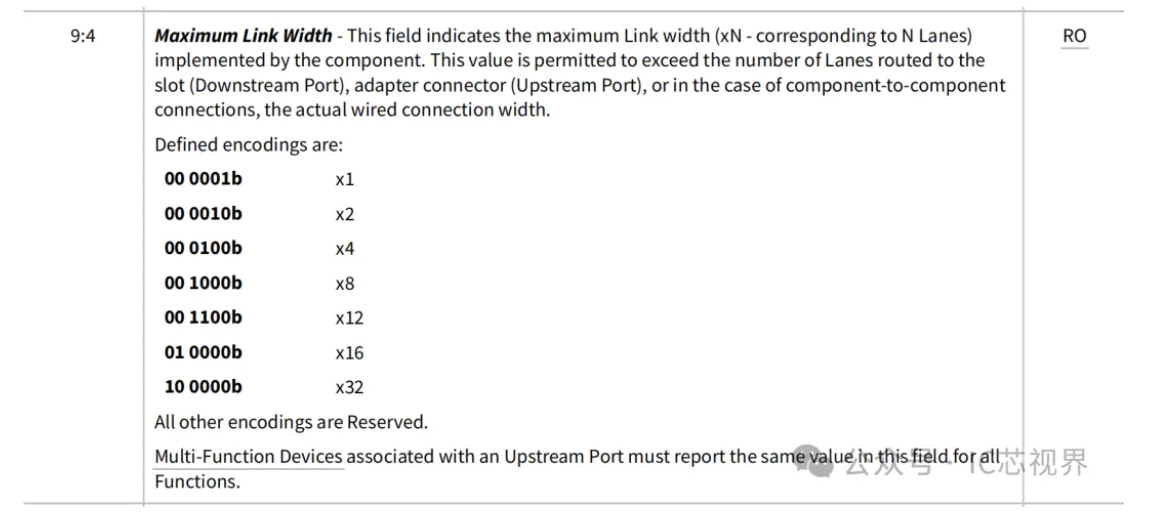

2.尝试调整lane数量,观察链路状态

通过修改EP的配置调整LnkCap(Link Capabilities Register)的Maximum Link Width数值(主流的PCIe IP均支持此功能),观察在不同lane数量的情况下,链路是否稳定,例如x16、x8、x4、x2和x1。

NOTE: 可以重点观察x16 --> x8 -->x16 两次跳变场景下的链路情况。

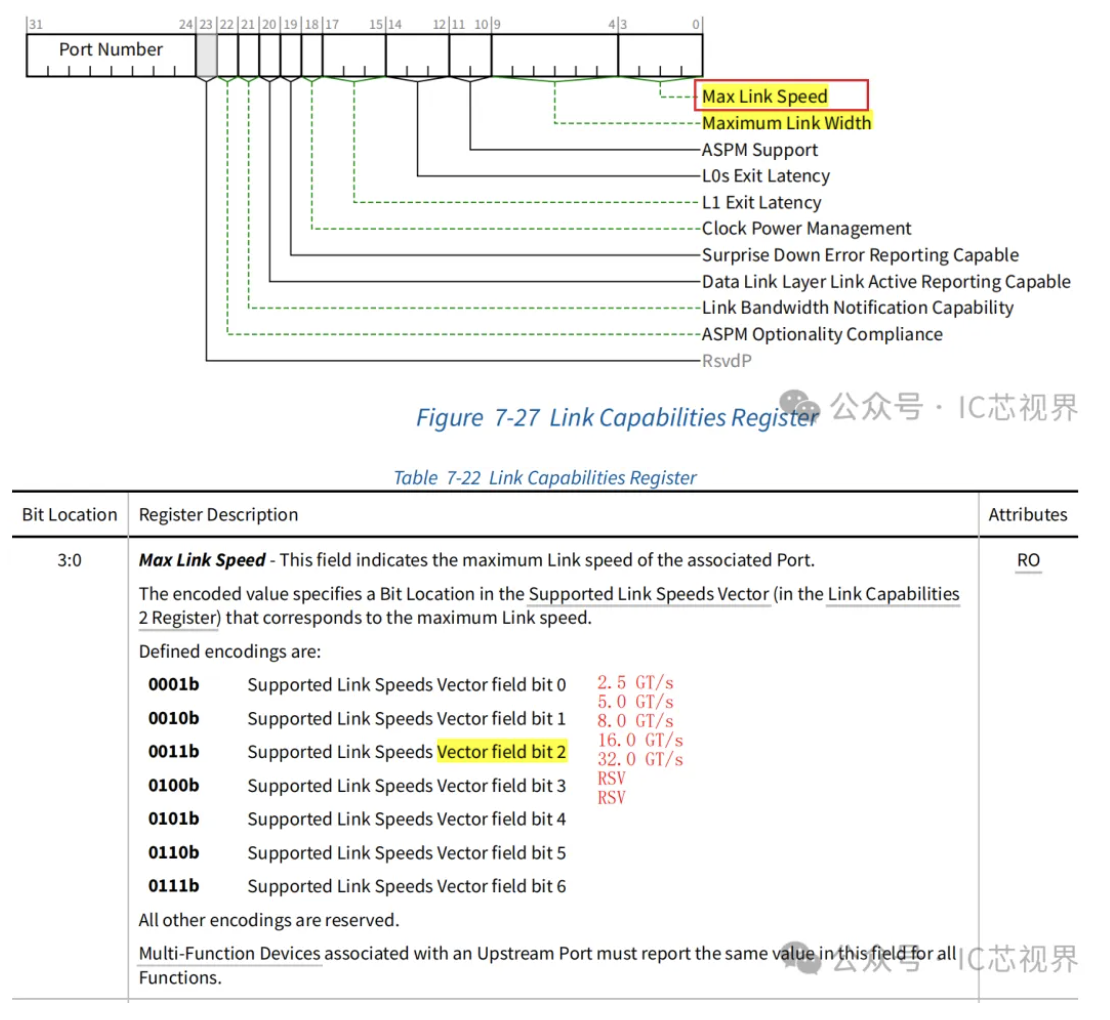

3.尝试调整PCIe速率,观察链路质量

通过修改EP的配置调整LnkCap(Link Capabilities Register)的Max Link Speed

数值(主流的PCIe IP均支持此功能),观察在不同速率的情况下,链路是否稳定,例如gen4、gen3、gen2、gen1。

NOTE: 可以重点观察gen4--> gen3-->gen4两次跳变场景下的链路情况。

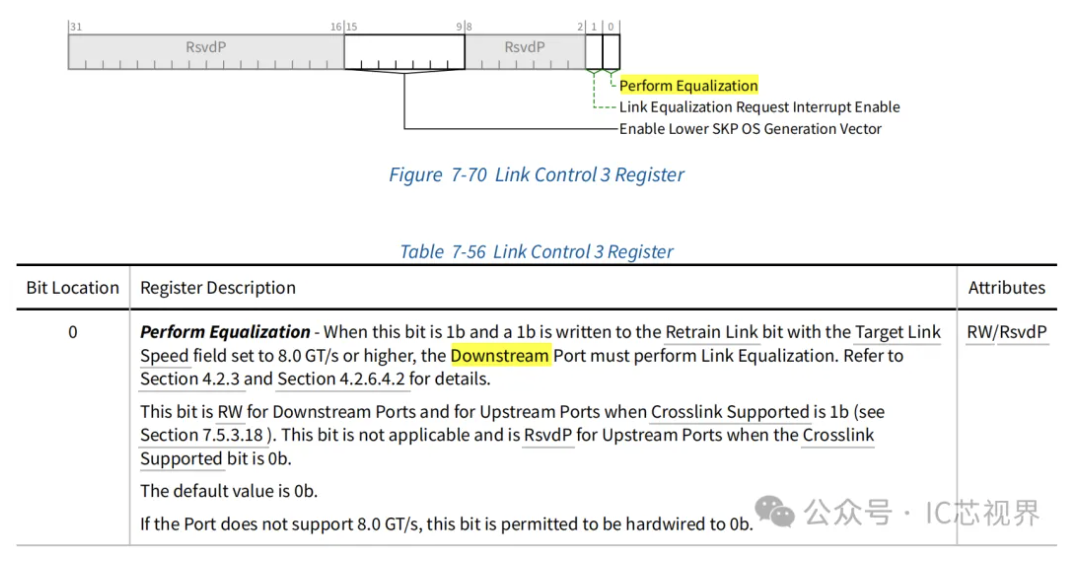

4.尝试Perform Equalization,观察链路状态

通过对DSP的Secondary PCI Express Extended Capability中Link Control 3 Register的Perform Equalization字段写1,使得DSP再次执行Equalization,等待LTSSM进入L0后,观察链路质量。本操作调整的是DSP和EP发送侧的均衡参数。

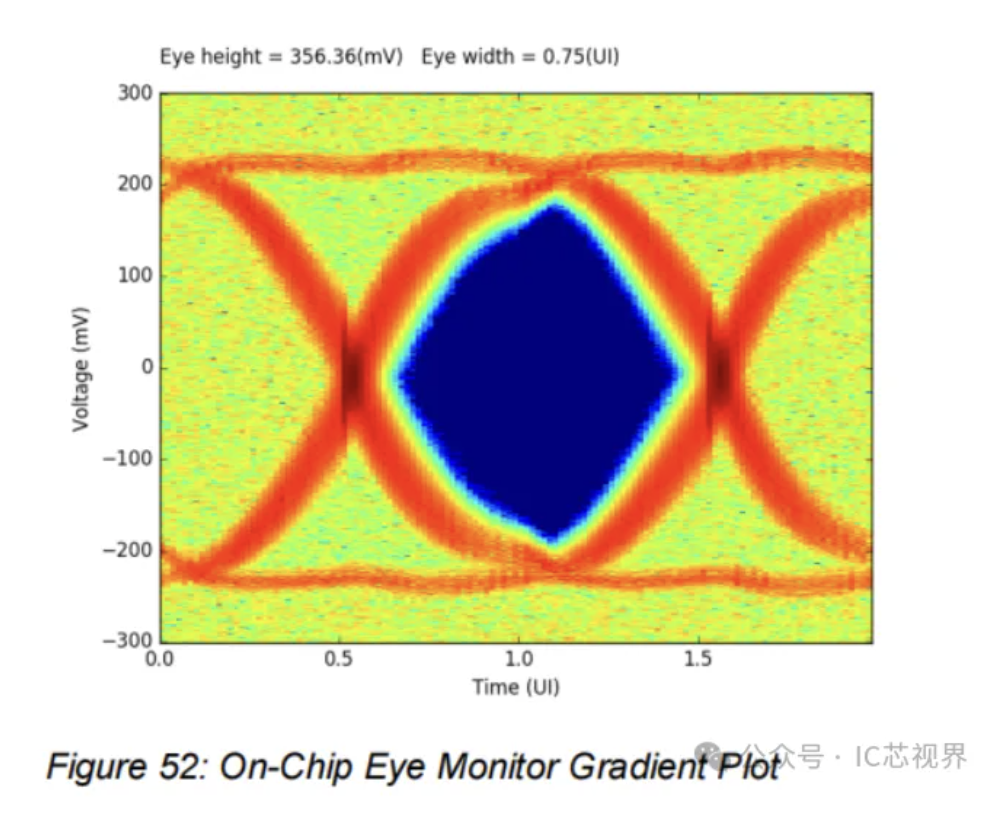

5.进行lane眼图测试,观察眼图质量

在出现链路问题的时候,对所有的lane进行眼图测试,观察不同lane的眼图质量。重点关注:是否存在部分lane的眼图在特定场景下(高速率)质量很差。

6.尝试进行PHY RX adapter,观察链路状态

对PHY的RX进行配置,使其再次进行adapter,PHY会根据链路状态进行自适应参数调整以满足链路质量的要求,不同的PHY vendor拥有不同的配置方法和限制条件,需要根据IP SPEC进行配置。此类配置是逐lane配置的,重点关注方法5中发现的有问题的lane。

7.尝试调整TX Equalization preset,观察链路状态

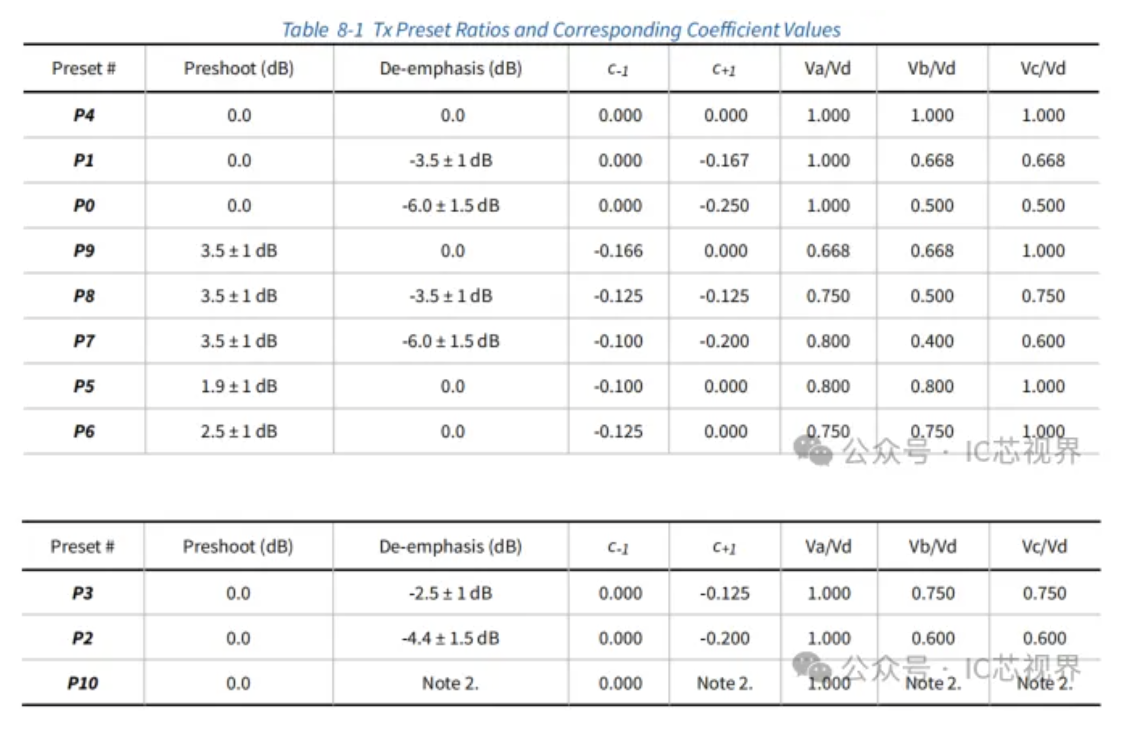

TX Equalization是PCIe中一项很重要的技术,用于提高信号传输质量。PCIe通过评估不同的Preset和Tx coefficients,最终选择最优的配置。

在ASIC芯片中,部分vendor的PCIe IP支持用户选择不同的preset,可以对PCIe 进行配置,在特定的preset中进行扫描。以Endpoint为例,通过不同的配置,在recovery.Equalization的phase2阶段,EP可以选择在Preset P0、P1、P2、P3、P4、P5、P6、P7、P8、P9、P10 中选择任意个preset进行链路质量评估扫描,最终选择链路质量最优的一个Preset。部分PCIe IP还可以配置Tx coefficients调整的次数,可以通过适量增加Tx coefficients调整次数以获取更好的链路质量。

8.通过PCIe 内部监控手段判断问题

PCIe 中的物理层、链路层和事务层通常都会存在中断、统计等常见的定位手段,包括但不限于:

链路层和事务层:

Receiver encoding error

Received bad TLP

Rx buffer overflow

Received bad DLLP

Parity error detected

Received TLP with LCRC error

物理层

128b/130b framing error detected

Elastic Buffer overflow

Elastic Buffer underflow

Phystatus[LNAE_NUM-1:0]

作者:IC小鸽

文章来源:IC芯视界

推荐阅读

更多IC设计干货请关注IC设计专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。