在当今这个数据驱动的时代,内存子系统的性能对各种计算系统的表现起着至关重要的作用。DDR(Double Data Rate)内存技术自 2000 年推出以来,经历了多次迭代和优化,已成为高性能计算、数据中心、消费电子和嵌入式系统中不可或缺的一部分。

在这篇文章中,我来探讨 DDR 的基本时序参数,从而深入理解这一复杂而重要的技术。

一、DDR 的基本时序参数

- tCL (CAS Latency)

CAS Latency (CL) 是 DDR 内存中一个非常重要的时序参数,它直接影响内存的性能和延迟。

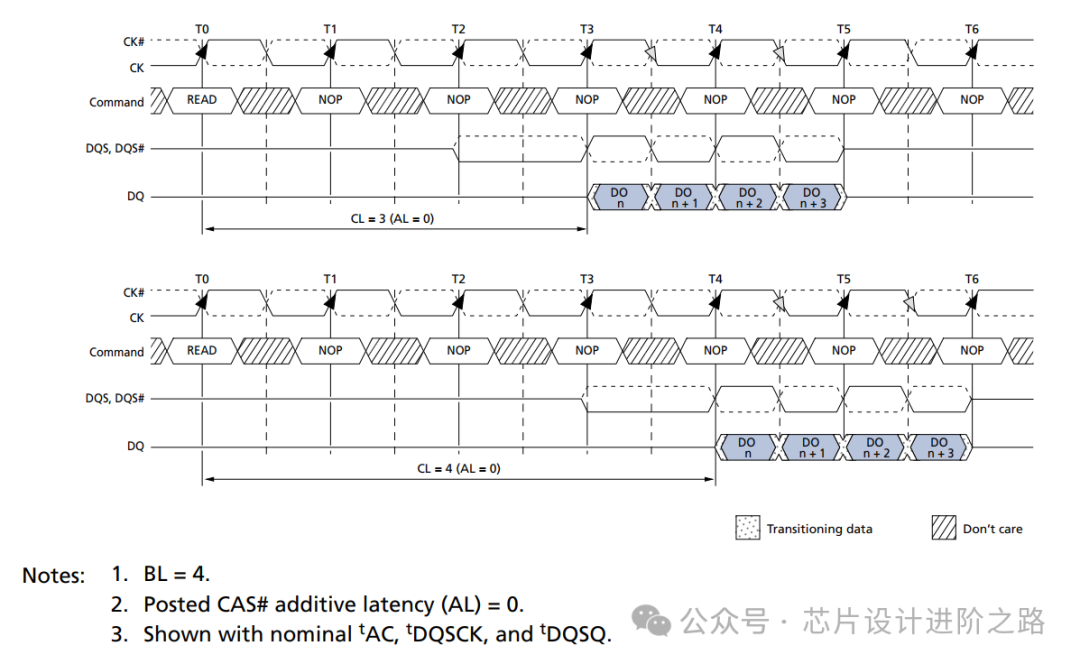

CAS Latency (CL),全称为 Column Address Strobe Latency,指的是从内存控制器发出读取命令到第一个数据可用的时间间隔。这个时间间隔以时钟周期为单位进行测量。CL 值越小,内存的响应速度越快,但通常 CL 值越小的内存价格更高,且对系统的稳定性要求也更高。

CAS Latency 的值可以是 1.5、2、2.5 或 3 等,具体取决于内存模块的规格。为了优化系统性能,建议在确保操作系统能够稳定运行的前提下,尽可能降低 CAS Latency 参数。这样可以有效减少内存的潜伏周期,提高数据访问速度。相反,如果内存在低 CAS Latency 设置下运行不稳定,可以通过增加 CAS Latency 值来增强系统的稳定性。这种调整有助于确保内存模块在各种工作负载下都能可靠地执行,同时平衡性能与可靠性。

tCL 对内存读写性能影响最大。

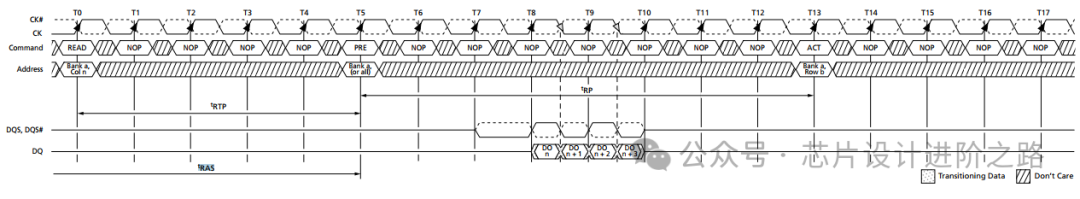

比如下图中,CL 分别等于 3 和 4.

注意,这里是时钟是 DDR 的工作时钟,也就是 IO 传输时钟,而不是 Memory array 的核心频率。

CAS Latency 的值通常以时钟周期为单位,表示为一个整数或半整数(如 1.5、2、2.5、3 等)。例如,如果 DDR4 内存的 CL 值为 16,时钟频率为 2400 MHz,那么第一个数据可用的时间为:

CL 值对带宽的影响相对较小,主要影响的是延迟。然而,较低的 CL 值可以提高内存的吞吐量,特别是在连续数据访问的情况下。

假设你有一条 DDR4-2400 内存,其时序参数为 16-18-18-38,其中第一个 16 就是 CL 值。这意味着从内存控制器发出读取命令到第一个数据可用的时间为 16 个时钟周期。

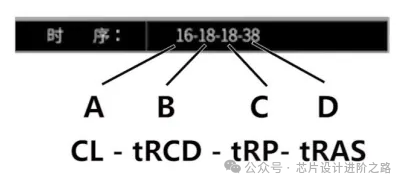

CAS 延迟(tCL)是最广为人知的内存时序。这个值通常是性能的代名词,但有时可能会误导。大多数人都认为 CAS 延迟越低越好,因为这个值代表着内存快速响应新信息的能力。这并不完全正确,因为新型内存的 CAS 延迟通常大大高于旧式内存。为什么新型内存的延迟时间更短?除了不同的时序,还必须乘以“时钟周期”。这个衡量标准反映内存可以多快准备好来处理新的命令集。DDR4 等新型内存的时钟周期时间比旧式内存快很多,这就意味着真实延迟(实际速度)快很多,如下图所示。

在内存技术的历史中,随着速度的提高(这意味着时钟周期时间减少),CAS 延迟值也增加,但是由于时钟周期加快,以纳秒计的真正延迟基本保持不变甚至减少。

- tRCD (RAS to CAS Delay)

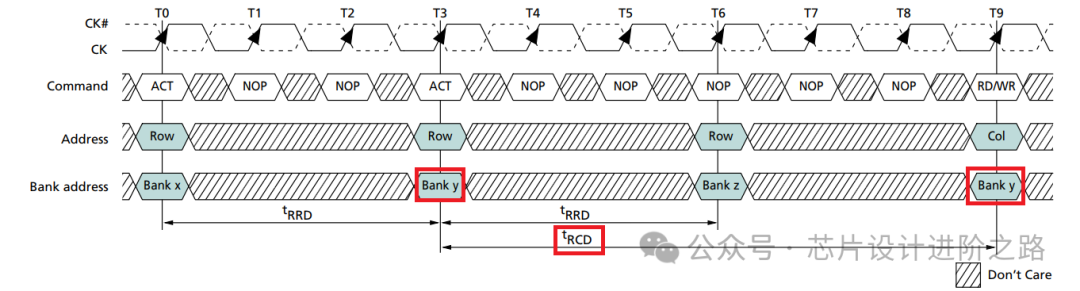

tRCD(RAS to CAS Delay)是指从行激活命令(Activate Command)发出到列地址选通命令(Read/Write Command)可以发出的最小时间间隔。这个时间间隔以时钟周期为单位进行测量。

在 DDR 内存的寻址过程中,首先需要指定 Bank 地址,随后是行地址,最终确定列地址以定位具体的存储单元。在实际操作中,Bank 地址与相应的行地址是同步发出的,这一过程被称为“行激活”(Row Active)。行激活之后,将发送列地址寻址命令以及具体的操作指令,用以指示是进行读操作还是写操作,这两个命令也是同时发出的,因此通常以“读/写命令”来指代列寻址。

tRCD,即 RAS 至 CAS 延迟(RAS-to-CAS Delay),其中 RAS 代表行地址选通脉冲(Row Address Strobe),CAS 代表列地址选通脉冲(Column Address Strobe)。tRCD 指的是从行激活到读/写命令发出之间的时间间隔,这个间隔也被称作行选通周期。在 DDR 内存的时序图中,tRCD 是衡量从行地址激活到列地址访问准备就绪所需时间的关键参数,对于内存性能的优化至关重要。

时序图如下:

假设你有一条 DDR4-2400 内存,其时序参数为 16-18-18-38,其中第二个值 18 就是 tRCD 值。这意味着从行激活命令发出到列地址选通命令可以发出的最小时间间隔为 18 个时钟周期。

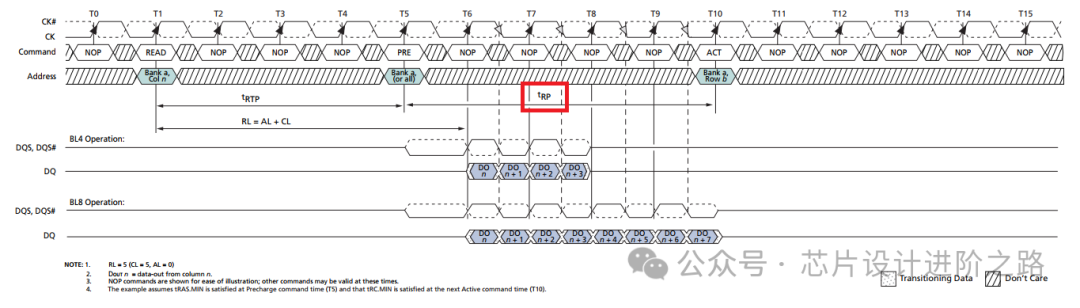

- tRP(Row Precharge Time)

tRP(Row Precharge Time)是指从行预充电命令(Precharge Command)发出到下一个行激活命令(Activate Command)可以发出的最小时间间隔。这个时间间隔以时钟周期为单位进行测量。

tRP 的作用

- 行预充电:

a. 在 DDR 内存中,每次访问数据时,首先需要激活一个行,然后访问该行中的列地址。

b. 当一个行不再需要访问时,需要通过行预充电命令将其关闭,以便释放资源并准备访问其他行。

c. tRP 定义了从一个行关闭到另一个行可以被激活的最小时间间隔。

- 性能影响:

a. 较小的 tRP 值:可以减少内存从一个行切换到另一个行的时间,从而提高内存的访问速度和整体性能。

b. 较大的 tRP 值:虽然会增加行切换的时间,但可以提高系统的稳定性和可靠性,适用于对稳定性要求较高的场景。

时序图如下:

假设你有一条 DDR4-2400 内存,其时序参数为 16-18-18-38,其中第三个值 18 就是 tRP 值。这意味着从行预充电命令发出到下一个行激活命令可以发出的最小时间间隔为 18 个时钟周期。

- tRAS(Active to Precharge Delay)

tRAS(Active to Precharge Delay)是指从行激活命令发出到行预充电命令可以发出的最小时间间隔。这个时间间隔以时钟周期为单位进行测量。

tRAS 的作用

- 行激活和行预充电:

a. 在 DDR 内存中每次访问数据时,首先需要激活一个行,然后访问该行中的列地址。

b. 行激活命令用于选择特定的行,而行预充电命令用于关闭当前行并准备访问其他行。

c. tRAS 定义了从行激活命令发出到行预充电命令可以发出的最小时间间隔。

- 性能影响:

a. 较小的 tRAS 值:可以减少内存从行激活到行预充电的时间,从而提高内存的访问速度和整体性能。

b. 较大的 tRAS 值:虽然会增加从行激活到行预充电的时间,但可以提高系统的稳定性和可靠性,适用于对稳定性要求较高的场景。

时序如下图所示:

假设你有一条 DDR4-2400 内存,其时序参数为 16-18-18-38,其中第 4 个值 38 就是 tRAS 值。这意味着从行预充电命令发出到下一个行激活命令可以发出的最小时间间隔为 38 个时钟周期。

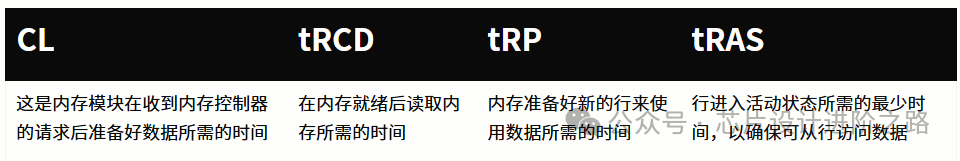

这 4 个就是最基本,也是最主要的时序参数了。总结一下,如下图所示:

二、DDR 的其他时序参数

- tRC (Row Cycle Time)

tRC(Row Cycle Time)是指从一行的激活命令(Activate Command)发出到同一行再次激活命令可以发出的最小时间间隔。这个时间间隔以时钟周期为单位进行测量。

计算公式:tRC=tRAS+tRP

tRC 越小,内存的行切换速度越快,性能越好。

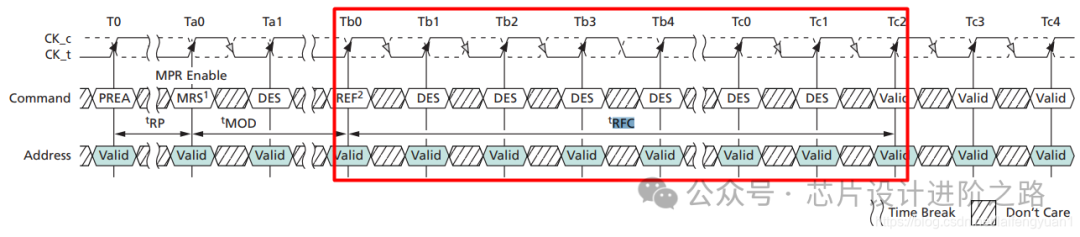

- tRFC (Row Refresh Cycle Time)

tRFC(Row Refresh Cycle Time)是指从一个行刷新命令发出到下一个行刷新命令可以发出的最小时间间隔。这个时间间隔以纳秒(ns)为单位进行测量。tRFC 定义了从一个行刷新命令发出到下一个行刷新命令可以发出的最小时间间隔,确保内存中的所有行都能在规定的时间内完成刷新。

tRFC 的值通常以纳秒(ns)为单位。例如,如果 DDR4 内存的 tRFC 值为 350 ns,那么从一个行刷新命令发出到下一个行刷新命令可以发出的最小时间间隔为 350 ns。

以下是不同 DDR 标准的典型 tRFC 值:

- DDR1:64 ns

- DDR2:64 ns

- DDR3:128 ns

- DDR4:350 ns

- DDR5:350 ns

- tRRD (Row to Row Delay)

tRRD(Row to Row Delay)是指从一个行激活命令发出到另一个行激活命令可以发出的最小时间间隔。这个时间间隔以时钟周期为单位进行测量。

tRRD 的值越小越好,延迟越低,表示下一个 bank 能更快地被激活,进行读写操作。然而如果延迟太短,会引起连续数据膨胀。

tRRD 可以分为:tRRD_S(Short Row to Row Delay)和 tRRD_L(Long Row to Row Delay)

tRRD_S (Row to Row Delay - Short):

- tRRD_S 指的是在不同 Bank Group(BG)之间发送行激活(ACTIVATE)命令时,两个连续 ACTIVATE 命令之间所需的最短时间间隔。这个参数确保了在不同 Bank Group 之间切换行时,内存有足够的时间来完成前一个命令,然后再响应新的命令。

tRRD_L (Row to Row Delay - Long):

- tRRD_L 则是指在同一个 Bank Group 内发送行激活命令时,两个连续 ACTIVATE 命令之间所需的最短时间间隔。与 tRRD_S 不同,tRRD_L 关注的是在同一 Bank Group 内部行地址切换的延迟。通常情况下,tRRD_L 的值会比 tRRD_S 大,因为它涉及到同一 Bank Group 内不同 Bank 之间的切换。

时序如下图所示:

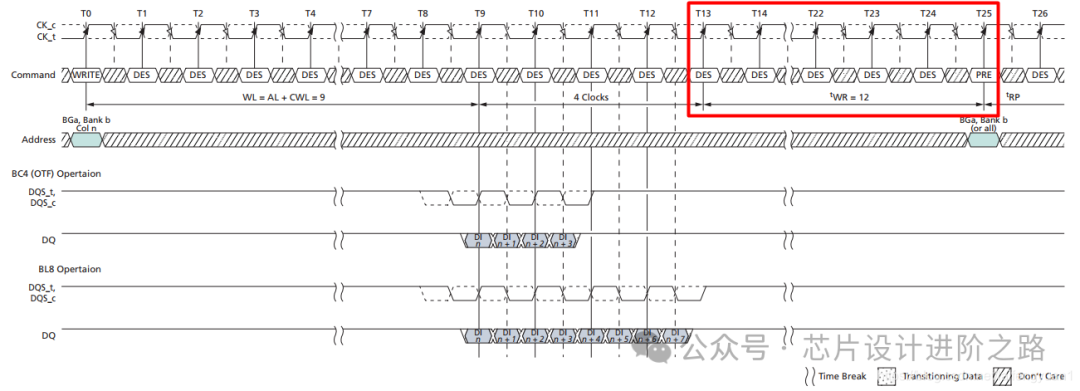

- tWR (Write Recovery Time)

tWR(Write Recovery Time)是指从最后一个写入命令发出到行预充电命令可以发出的最小时间间隔。这个时间间隔以时钟周期为单位进行测量。

- 在 DDR 内存中,数据写入操作完成后,需要一定的恢复时间,以确保数据正确写入存储单元。

- 行预充电命令用于关闭当前行并准备访问其他行。

- tWR 定义了从最后一个写入命令发出到行预充电命令可以发出的最小时间间隔,确保写入操作完成后有足够的恢复时间,避免数据错误。

- 较小的 tWR 可以提高系统性能,但可能导致数据还未完全正确写入内存单元,就发生了预充电操作,导致数据的丢失和损坏。

时序如下图所示:

- tWTR (Write to Read Delay)

tWTR(Write to Read Delay)是指从一个写入命令发出到读取命令可以发出的最小时间间隔。这个时间间隔以时钟周期为单位进行测量。该值表示的是,DDR 内存模块中的同一个单元中,在最后一次有效的写操作和下一次读操作之间必须等待的时钟周期。

- 在 DDR 内存中,写入操作和读取操作之间需要一定的间隔时间,以确保写入的数据已经正确存储并且不会干扰读取操作。

- tWTR 定义了从一个写入命令发出到读取命令可以发出的最小时间间隔,确保写入操作完成后有足够的恢复时间,避免数据错误。

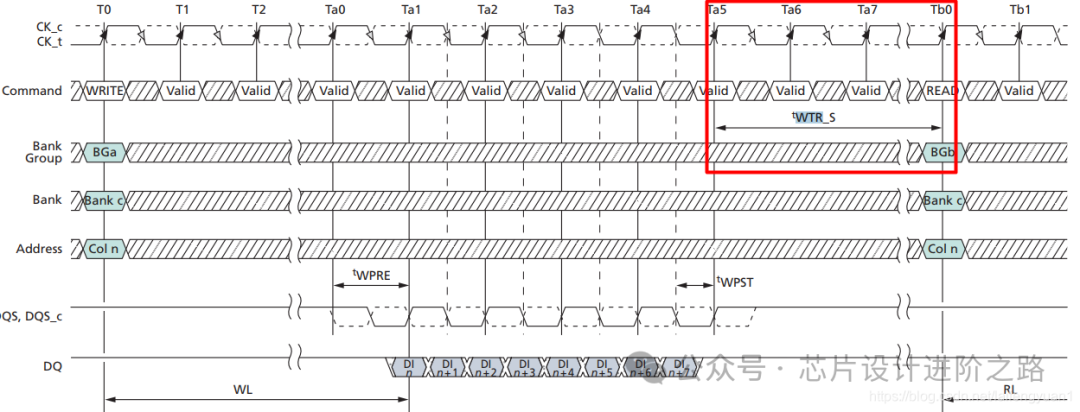

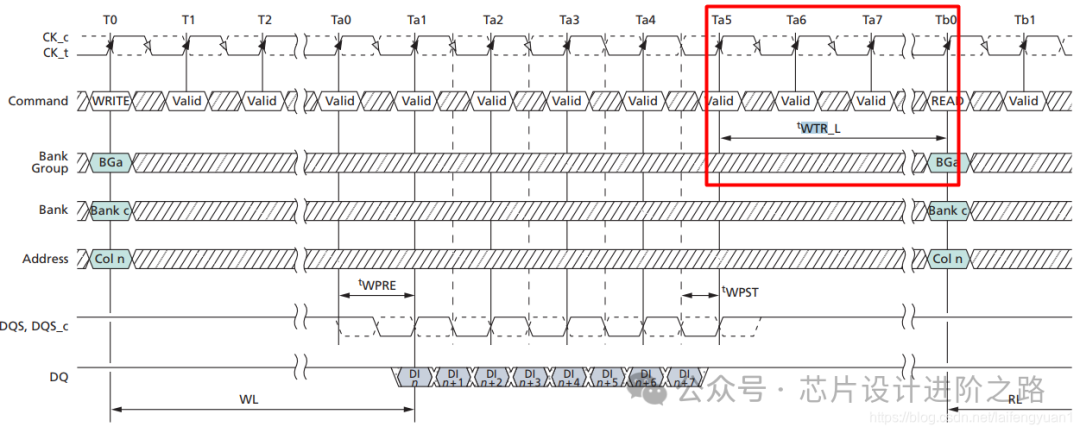

同样分为tWTR_S 和 tWTR_L

tWTR_S (Write to Read Delay, Short):

- tWTR_S 是指在不同 Bank Group(BG)之间,从写入命令开始到读取命令的延迟时间。这个参数涉及到跨 Bank Group 的操作,因此通常比同一 Bank Group 内的写读延迟要长。tWTR_S 的值越小,意味着在不同 Bank Group 之间进行写入后切换到读取操作的速度越快。

tWTR_L (Write to Read Delay, Long):

- tWTR_L 是指在同一 Bank Group 内,从写入命令开始到读取命令的延迟时间。这个参数涉及到同一 Bank Group 内的写读操作,因此通常比跨 Bank Group 的操作要短。tWTR_L 的值越小,意味着在同一 Bank Group 内进行写入后切换到读取操作的速度越快。

时序图如下所示:

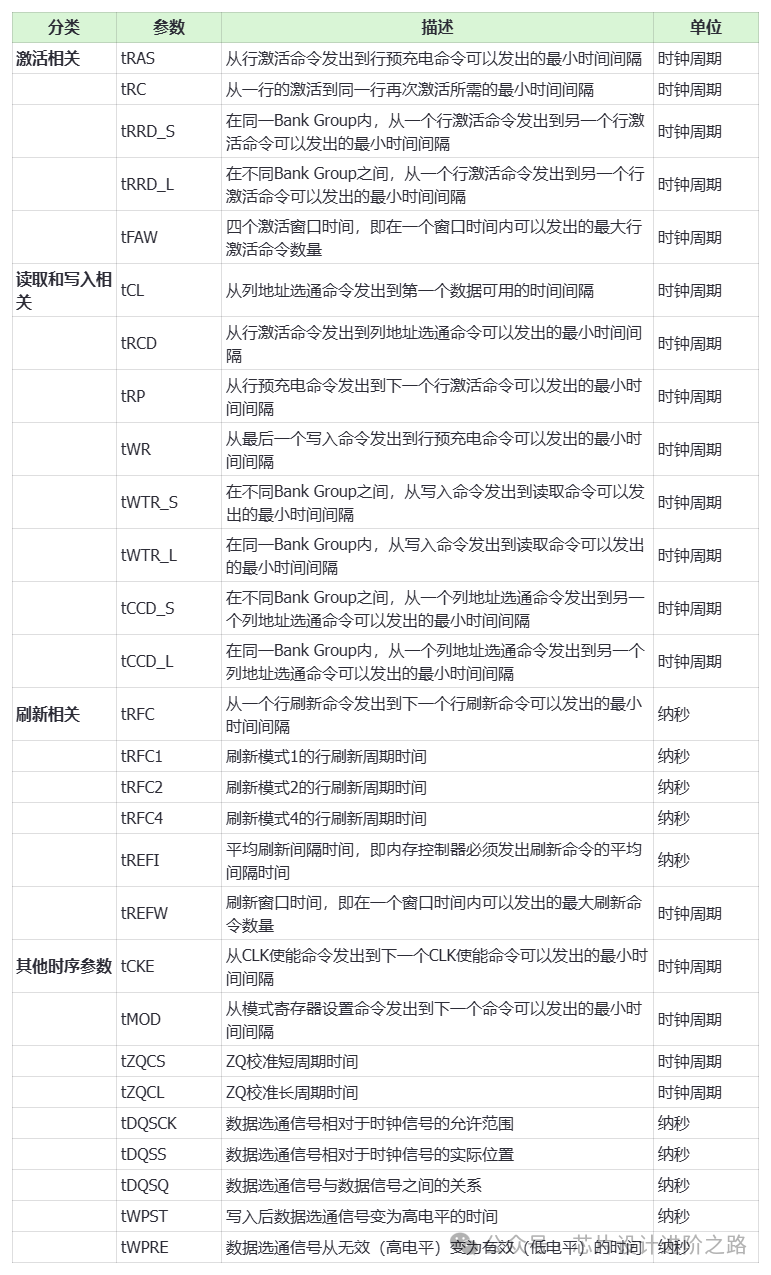

三、总结

DDR 时序参数对于内存的性能、稳定性和可靠性至关重要,它们定义了内存操作的时间特性和行为。DDR 有非常多的时序参数,而且又非常相似,有时候很容易让人头晕。

以上列举的是最基本的一些参数,也是我觉得需要熟练掌握的参数,对基本参数甚至要熟记。

总体来说,DDR 的参数可以分为按照激活相关,读取和写入相关,刷新相关还有其他时序参数这四大类,不同的类型对应的参数如下表所示:

感兴趣的可以自行去查询。

DDR 时序参数对于确保内存性能、稳定性和兼容性至关重要。它们影响数据访问速度,防止数据损坏,维持系统稳定,并支持超频和电源管理。适当的时序参数设置还能提高多通道内存的兼容性和系统的整体能效,同时在设计和故障诊断过程中发挥重要作用,满足不同应用场景的需求。

同时时序参数也是一个难点(至少对我来说),可能需要在不断的学习中去不断重复和强化才能完全掌握。

后纪

技术很重要,技术背后的思想更重要!

技术背后的某些思想就是你解决以后问题的钥匙。我的文章可能一篇中知识点不太多,但是力求让你能深入理解,为你进阶打下基础。如果有一点点收获,也算是我对中国芯片行业的一点点贡献吧。

参考文献

https://blog.csdn.net/laifeng...

https://www.systemverilog.io/...

END

作者:烓围玮未

文章来源:芯片设计进阶之路

推荐阅读

- 硅芯思见:【193】后仿真里的负延迟

- cocotb 仿真加速——合并

- 手把手教你从零设计一款算力超过 1000Tops 的智能驾驶芯片

- 深入了解 PCIe 协议

- 当机器人学会扫堂腿:一场踢向万亿市场的芯片机遇

更多 IC 设计干货请关注IC设计专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。