本文首发于知乎专栏【数字IC后端设计工程师修炼之路】,作者阎浮提。转载请事先联系。

功耗是衡量一款芯片优劣的重要指标之一。在实际的芯片后端设计中,功耗究竟是如何计算的呢?

功耗本质上就是电学术语中的功率,不同于一般简单的电学器件,芯片的整体功耗很难通过简单的电流,电压或者电阻值的的相乘来计算。其原因在于,由于芯片作为具有复杂功能的器件,其功耗会根据其不同时段的不同行为,不同的外部条件而发生很大的变化。

在实际设计中,一般会选取一些特定的条件,并辅以特定的功能设定来计算芯片的功耗。

那么,芯片的整体功耗都有哪些组成部分呢?最根本的组成部分有两个,即静态功耗和动态功耗。

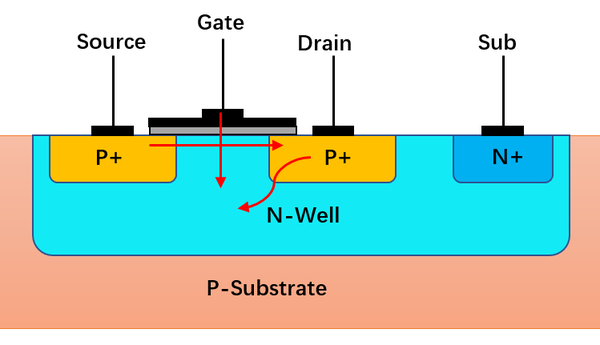

1. 静态功耗(Static Power),又称漏电流功耗(Leakage Power)。其原理请参见下图:

PMOS Leak 电流示意图

上图中红色箭头表明了在通电状态下PMOS内主要的泄露电流及其走向,意即:

泄漏电流(Leakage Current) = 漏极->N-Well + Gate->N-Well + 源极->漏极

泄露电流存在的原因在于,MOS管中的多种掺杂区形成导电区域,同时这些区域会组成多个PN节,从而在通电后形成一系列微小的电流。

尽管在现今芯片的工作电压已经很低的前提下,每个MOS管的漏电流很小,但由于每颗芯片中集成的晶体管至多几亿甚至几十亿,积少成多,导致芯片的整体leakage power变得越来越恐怖。

在后端设计中,由于每个标准单元(standard cell)的leakage都集成在其liberty库文件(.lib)中,因此计算leakage power只需在制定条件下将design中所有的标准单元(包括各种Macro)的leakage值相加即可。目前所有的主流PR工具对此都有支持。需要指出的是,由于一个标准单元的leakage power和其面积成正比,因此在实际后端设计的各个阶段,尤其是low power设计中,一般会重点关注芯片中逻辑门的面积变化并以此快速推断design的leakage功耗变化。

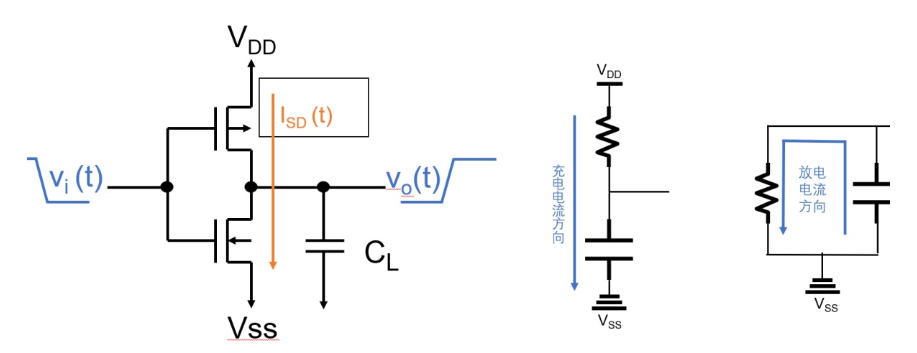

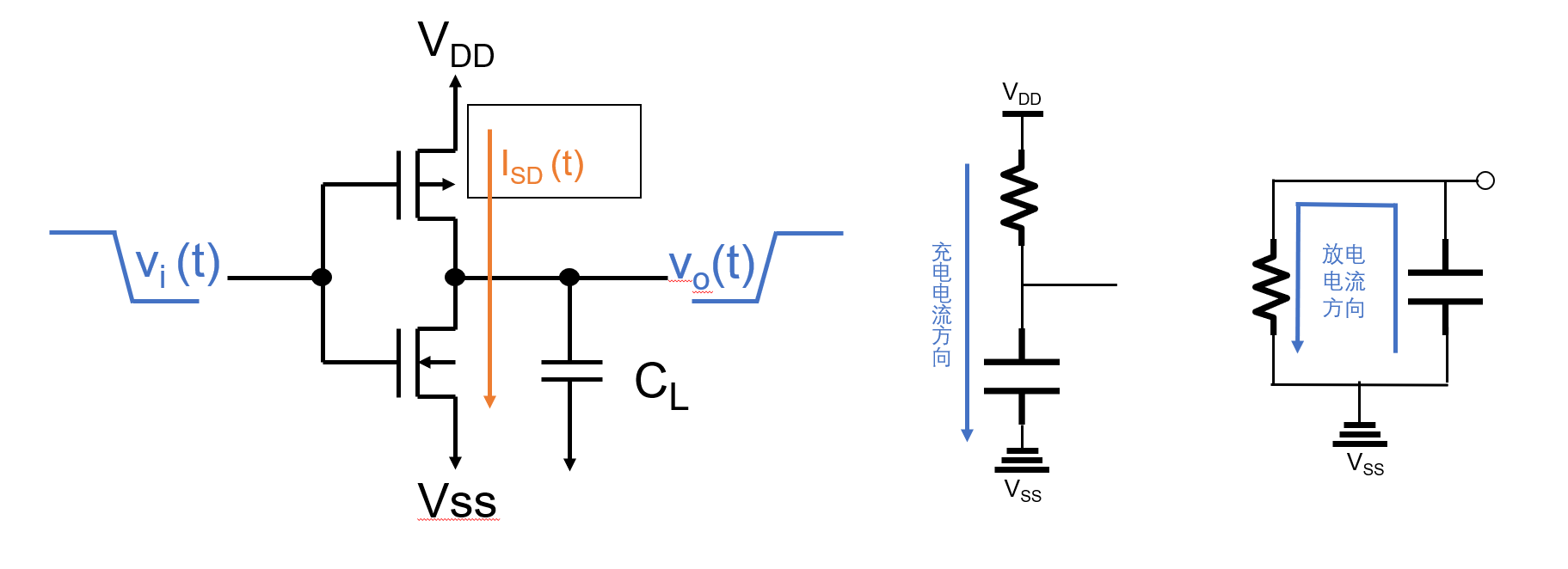

2. 动态功耗(Dynamic Power),主要是由于芯片中的寄生RC电路的充放电引起的。换言之,当芯片中的电路出现任何信号翻转,都将会产生dynamic power,其中所占最大比例的就是clock信号的翻转。下图展示了一个反相器(inverter)在信号翻转时的简单模型:

Inverter Dynamic Power Consumption

当我们把反相器简化成一个简单的rc电路时,就可以清晰的看清充放电时的电流走向。当芯片处于工作状态时,每一个工作中的标准单元都会随着clock or/and data的翻转而不断重复上述过程,从而产生大量的动态功耗。

在实际后端设计时,动态功耗由于和芯片的功能息息相关,因此在计算的时候会引入翻转率(toggle rate)的概念。翻转率是衡量单位时间内device上信号翻转时间所占的比率。在实际计算dynamic功耗的时候,又会分成两个部分。一部分为标准单元内部的dynamic功耗,又名Internal Power,这部分的计算是嵌入liberty库文件内部,通过标准单元的input transition和output load来查表得到的;另一部分为互连线(net)上的dynamic功耗,这部分的计算通过将所有net上每个翻转周期的功耗乘以其翻转率并相加得到。反转率通过某种固定格式的文件传入EDA工具,比较常用的格式有SAIF(Switching Activity Interchange Format)、VCD(Value Change Dump)以及FSDB(Fast Signal Database)文件。

目前主流的PR工具均支持此类用法,但是signoff时仍然需要比较专业的power计算工具如Synopsys PrimeTime PX或Cadence Palladium等。

至此,我们基本了解了一颗芯片整体功耗的计算方法。而在现今十分重要的低功耗设计中,所有的手法都是从降低以上两个方面(Static, Dynamic)的功耗着手的:

比如应用多个power domain以便在芯片的某一部分功能不用的时候将其断电关闭;或者通过升级更先进的工艺来降低每个晶体管的size从而降低整体面积;抑或通过改善时钟树综合手段来降低芯片中占比很大的clock network power。

往期问题以及回答:

问:library setup time和library hold time应该都是正值,但是它们是否有可能是负值?如果有可能,在什么情况下会为负呢?

答:在实际设计中,它们均可能为负值,其根本原因在于当前很多DFF的标准单元中并非纯粹的D触发器结构,而是会包含数量不等的buffer/inverter。详细的内容请参看我收藏的这篇文章:https://pan.baidu.com/s/1xLbwl1KnbuOUSZtiIBnmSw

相关文章

如果大家有任何后端技术与职业发展方面的问题,抑或关于数字后端感兴趣的技术话题想要了解和探讨,欢迎关注我的知乎专栏: 数字IC后端设计工程师修炼之路同时欢迎关注微信公众号:数字后端芯讲堂,一起探讨技术,共同提升!

本极术专栏也会同步更新芯片设计后端的技术干货,也请关注数字IC后端设计工程师修炼之路。