使用create\_clock命令创建的时钟都是ideal的,忽略了时钟网络的延迟。要进行准确的时序分析,还需要描述时钟网络的一些主要特征(比如,latency和uncertainty)

Latency(延迟)包括时钟源延迟(clock source latency)和时钟网络延迟(clock network latency)。

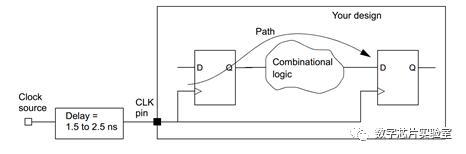

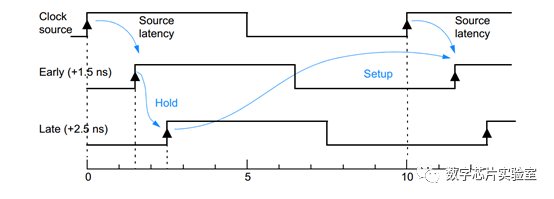

时钟源延迟是时钟信号从其时钟源传播到时钟定义点所需的时间。

时钟网络延迟是时钟信号从设计中的时钟定义点传播到寄存器时钟引脚的时间。

Clock uncertainty(时钟不确定性)是寄存器中时钟信号到达时间的最大差异。Clock uncertainty设置了额外的margin来更加严格setup和hold时序检查,我们可以为同一路径上的setup和hold时序检查指定不同的uncertainty。

设置Clock Latency

•通过时钟网络的传播延迟来计算Latency。这种方法非常准确,但只能在CTS之后使用。

•明确估计和指定每个时钟的延迟。 通常这种方法在CTS之前使用。

设置传播延迟(Propagated Latency)

EDA工具可以在CTS之后通过传播延迟来自动确定时钟网络的延迟。这时产生的结果非常精确,时钟网络中的单元和网络延迟都被反标(back-annotated)。从时钟源到寄存器时钟引脚的路径延迟会使时钟偏移(skew)。所以当设计具有实际的时钟树时,应该使用传播延迟:

set_propagated_clock [get_clocks CLK]删除当前时钟的传播延迟属性,使用remove\_propagated\_clock命令。

指定时钟源延迟(Clock Source Latency)

我们可以为ideal或者propagated时钟指定时钟源延迟。时钟源延迟是从时钟源到时钟定义点(端口、引脚)的延迟。寄存器时钟引脚的延迟是时钟源延迟(clock source latency)和时钟网络延迟(clock network latency)的总和。

对于内部生成时钟(generated clocks),EDA工具可以自动计算时钟源延迟。

对于prelayout设计**,传播延迟通常是不准确的,因为寄生参数不清楚**。对于prelayout设计,可以估计每个时钟的延迟并使用set\_clock\_latency命令直接设置该估计值。

要指定外部时钟源延迟的不确定性,可以使用-early和-late选项。例如,考虑可能从1.5到2.5 ns变化的源延迟。

要指定上图的时钟源延迟,可以使用以下命令:

create_clock -period 10 [get_ports CLK]

set_clock_latency 1.5 -source -early [get_clocks CLK]

set_clock_latency 2.5 -source -late [get_clocks CLK]对于setup分析,它使用late值。 对于hold分析,它使用early值。

以下示例了如何为上升沿和下降沿设置不同的源时钟延迟值。

要将CLK的上升沿延迟设置为1.2并将下降沿延迟设置为0.9

set_clock_latency -rise 1.2 [get_clocks CLK]

set_clock_latency -fall 0.9 [get_clocks CLK]可以使用remove\_clock\_latency命令用于删除指定的时钟网络延迟或时钟源延迟。

设置时钟不确定性(Clock Uncertainty)

在工具中,使用set\_clock\_uncertainty命令指定时钟的不确定性。

可以使用Clock Uncertainty来建模pre layout设计的时钟确定性。EDA工具会根据调整时钟不确定性后的时序检查最差情况,检查setup时间(maximum paths)时会从required time中减去Clock Uncertainty值,检查hold时间(minimum paths)时会在required time中增加Clock Uncertainty值。如果指定单个Clock Uncertainty值,工具会将其同时用于setup和hold检查。

例如:

set_clock_uncertainty 5 [get_clocks CLKA]

我们还可以为setup和hold分析设置不同的时钟不确定性:

set_clock_uncertainty -setup 0.21 [get_clocks CLK1]

set_clock_uncertainty -hold 0.33 [get_clocks CLK1]使用remove\_clock\_uncertainty命令设置时钟不确定性。

——

估计时钟引脚转换时间(Transition Time)

当尚未构建时钟树时,时钟网络上单个缓冲器可能会驱动10,000个寄存器时钟引脚。 这可能会导致寄存器的Transition Time过大,从而影响时钟网络延迟,以及setup和hold时间检查。(setup违例情况之一)

可以使用set\_clock\_transition命令估计整个时钟网络的Transition Time。

例如:

set_clock_transition 0.64 -fall [get_clocks CLK1]使用命令的-rise或-fall选项仅指定时钟的上升或下降沿的转换时间。

使用remove\_clock\_transition命令删除估计的时钟引脚转换时间。

本文转载自公众号:芯片数字实验室

原文链接:

https://mp.weixin.qq.com/s/7hJ-P2ge-VH7pPle73O4Aw

未经作者同意,请勿转载!

推荐阅读

想了解更多内容,欢迎关注芯片数字实验室专栏