今天跟大家分享一下开源RISC-V处理器蜂鸟E203的综合实践,然后比较一下Synopsys的综合工具DCG和DC NXT在相同条件下的表现。本来打算一篇就写完,后来发现内容有点多,所以就分成上下两篇,免得看得太累。

首先简单介绍一下相关背景。RISC-V大家应该听过很多,就不赘述了。蜂鸟E203作为数不多的国内作者开发的RISC-V内核开源处理器,非常适合处理器设计的初学者学习入门。不过今天我们的重点并不是它的逻辑设计和软件开发,而是逻辑综合。不同于其自带文档和环境中的在FPGA上低速时钟下的综合,我将按照ASIC设计方法中的综合流程,将时钟频率调高来尝试把它综合出来并尽量能在后端流程中把它实现。

关于综合工具,我们主要用Synopsys的Design Compiler(以下简称DC)。DCG(Design Compiler Graphical)作为当前复杂设计的主流版本,由于其能够在综合阶段考虑物理状况来优化设计而广受好评;而DC NXT作为新推出不久的下一代综合工具,相信很多一线工程师已经在用,而且对其效果有了相当程度的了解了。我在蜂鸟E203上做了一些实验来比较DCG和DC NXT在综合结果和PnR结果上的差异,今天把结果和大家分享一下。

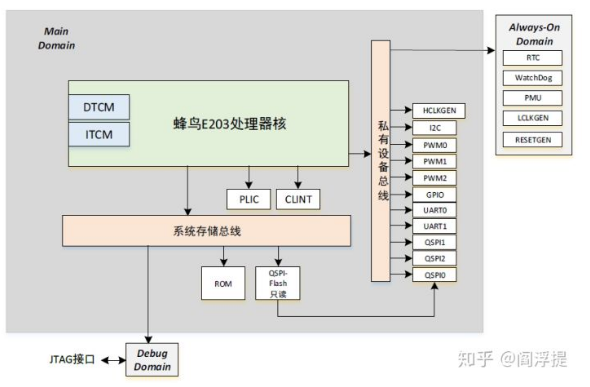

蜂鸟E203规模很小,但是称得上麻雀虽小五脏俱全。从其官方文档中可知其基本逻辑结构图如下,除了处理器内核还有对应的总线连接外设,可算是基本完备的SoC:

蜂鸟E203逻辑结构图

上图中我们还可以看到它有2个power domain,其中main domain还可以关闭。不过今天我们展示的综合并不会定义这2个domain,因为这样会让整体实现都变得更麻烦。这部分工作将会在以后的比较后端工具的部分补上。

对应的其时钟结构如下,整体的时钟也比较简单:

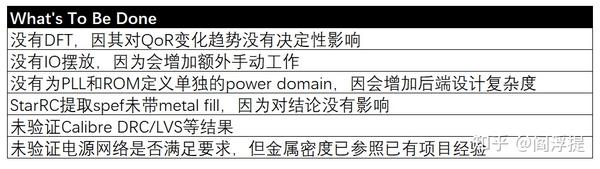

其他方面诸如总线、外设、电源域和IO信号等与本次内容关系不大,不作详述。有兴趣可以看看它的自带文档。下面简单介绍一下我做了什么,以及还有什么需要做:

上面没做的内容基本上都属于增加工作量而对本次实验结果没有决定性影响的东西,因此就暂时放弃了,这些东西后面有时间把这个处理器当作真正的芯片来做后端的时候会尽量都加上。

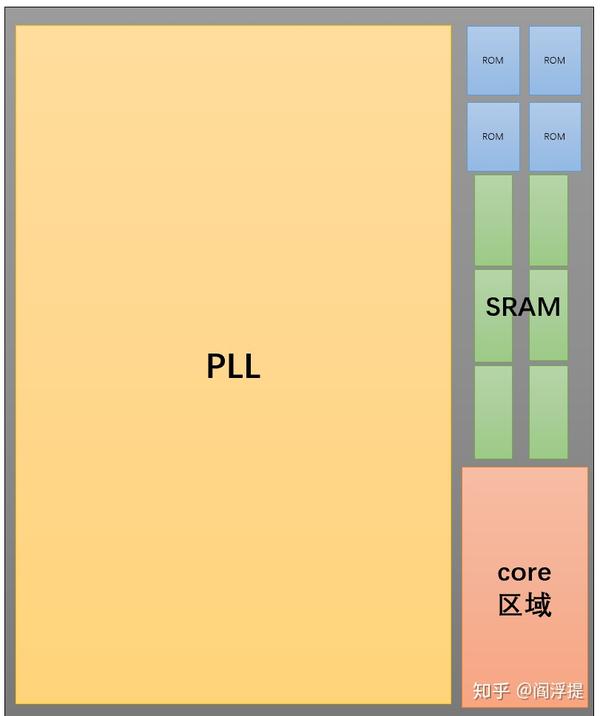

闲话少说,先来看看floorplan。本次实验用的是比较先进的工艺,为避免暴露太多东西,真实的floorplan图就不贴了,取而代之我画了一张等比例的示意图如下:

简单说明以下几点:

PLL之所以这么大,一是因为整个设计实在太小了,二是因为手头没有更小的PLL。本来打算拿掉PLL,但是由于它能在电源域方面带来一定的复杂度,对以后评估后端工具有好处,所以就保留了;ROM来自u\_sirv\_mrom\_top模块;SRAM来自ITCM和DTCM各3块;设计中的所有port均匀摆在die周围来模拟存在IO的情况;standard cell集中在右下角,core区域的utilization在50%-60%之间,算是中规中矩,其他区域都是soft或者buffer only的blockage;endcap和tap cell都按规则插好;PLL、SRAM、ROM和core区域使用不同的电源,UPF保证正确定义且电源网络也按规则打好;使用金属层较多,因此基本不存在绕线问题,故RC不受绕线性影响;PnR阶段的各种约束和margin (jitter, skew, SI等)都按照正常流程设置,具体数值可能稍有不准;

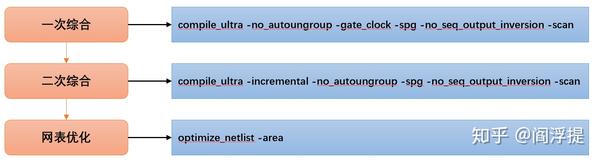

整体的综合流程是比较典型的三步走:

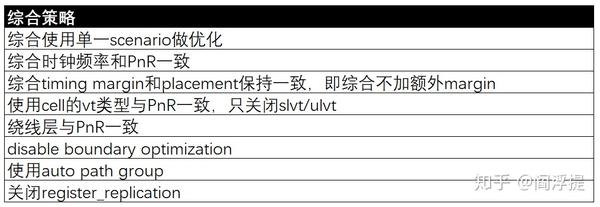

其他综合策略也不复杂,可以概括如下:

顺便提一下,DCG和DC NXT的命令基本上是通用的。本次实验就是用完全相同的设置分别跑了两个工具,并未发现什么问题。

至此,综合的所有准备工作基本就绪了,剩下的就是工具自己去跑了。

其实这个设计本来是为低功耗设计的,因此在很多地方并不利于做高频设计。如果看过它的文档就知道其主时钟频率默认只有几十MHz,很多在低频设计根本看不到的问题在提高时钟频率后都会显现出来:比如设计中存在很多逻辑深度非常深的timing path,有的多达60-70级;如果加入clock gating的话会发现有些gating的控制端也会有非常深的逻辑深度,因而极其容易出现大的setup violation;有些timing path要么是设计不合理要么是false path的,如从SRAM出发经过数十级逻辑再返回SRAM的地址位的。这些问题都会尽量想办法去暂时避开或者去优化,具体的结果将会总结出来并在下篇贴出,敬请关注!

相关文章

如果大家有任何后端技术与职业发展方面的问题,抑或关于数字后端感兴趣的技术话题想要了解和探讨,欢迎关注我的知乎专栏: 数字IC后端设计工程师修炼之路同时欢迎关注微信公众号:数字后端芯讲堂,一起探讨技术,共同提升!

本极术专栏也会同步更新芯片设计后端的技术干货,也请关注数字IC后端设计工程师修炼之路。