Low Power

低功耗是当今大多数芯片的关键要求。 芯片的功耗越大,设备就会越热,运行速度越慢。并且在高温下,芯片的可靠性会降低。

本文讨论如何在RTL级对功耗进行优化。

在RTL编码期间可以有哪些方法降低功耗?

在芯片逻辑转换期间,CMOS电路中的任何开关活动都会产生瞬时电流,因此增加了功耗。

设计中最常见的存储元件是同步触发器,它的输出会在输入数据和时钟改变时改变。 因此,如果输入数据和时钟只有在需要时才存在或者触发就可以减少

电路信号开关活动,降低功耗。 以下总结了一些降低功耗的机制:

1、减少输入数据的切换。

2、减少触发器的时钟切换。

3、减小芯片面积,因为可以减少门/触发器的开关切换。

以下深入讨论在RTL级降低功耗的实现问题:

如何减少触发器的输入数据切换来降低功耗?

对于相对于时钟很少更新的触发器来说,应该仅在合适的时候更新触发器,避免触发器输出没有必要的更新。

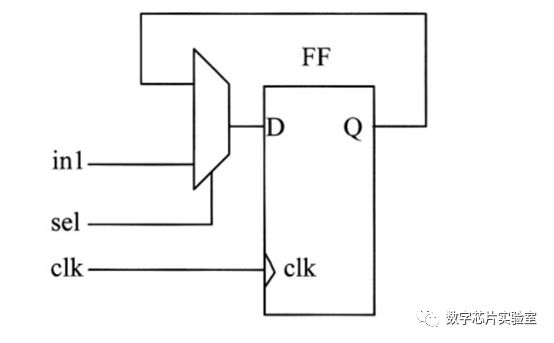

这可以通过使能触发器实现,如下图所示:

实现使能触发器的Verilog RTL的示例如下:

module enable_ff(

clk ,

sel ,

reset_n ,

in1 ,

out1 );

input clk ,reset_n,sel ,in1 ;

outpu out1 ;

reg out1 ;

always@(posedge clk or negedge reset_n) begin

if(!reset_n)begin

out1<= 1’b0 ;

end

else if(sel) begin

out1<= in1 ;

end

else out1 <= out1 ;

end

endmodule通过遵循上述的编码风格来降低功耗是不够的,因为它有一个缺点:

尽管使用使能触发器可以减少数据切换,但是它引入了额外的逻辑到触发器的D输入,可能会增加关键路径的延迟。

另一个副作用是,会增加芯片的面积。

时钟门控如何减少功耗?

时钟门控是节省功耗最常用的机制。这种技术通过以下方式减少触发器输出的切换:

1、无需在寄存器中重新加载相同的值

2、降低时钟网络功耗。

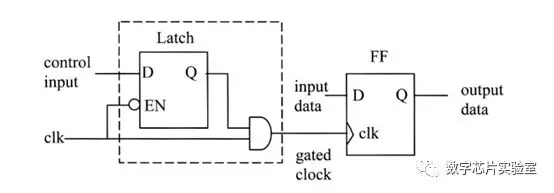

时钟门控最常用的方法是使用锁存器和一个门,如下图:

当clk处于低电平时,锁存器被使能。如果输入控制信号为高,则Q在时钟低电平时为高电平,并保持不变直到下一个clk的低电平。

电路中的锁存器输出很容易满足触发器的建立时间要求。当输入控制信号为低电平时,会阻止了clk的传播。这使得门控时钟网络没有任何转换活动。

一个简单的Verilog代码可以描述上述逻辑,如下:

module gated_ff(in1 , cntrl_in , clk ,reset_n , out1 ) ;

input cntrl_in , in1 ,reset_n;

output out1 ;

wire gated_clk ;

reg d_latch , out1 ;

always@(cntrl_in , clk ) begin

if(!clk) d_latch <= cntrl_in;

end

assign gated_clk = d_latch & clk ;

always@(posedge clk or negedge reset_n) begin

if(reset_n) begin

out1 <= 1’b0 ;

end

else begin

out1 <= in1 ;

end

end

endmodule在大型设计中门控时钟都是通过综合工具完成的,无需手动实现。

此外,门控元件AND门可以根据使能的逻辑电平和触发器边沿触发类型改变。

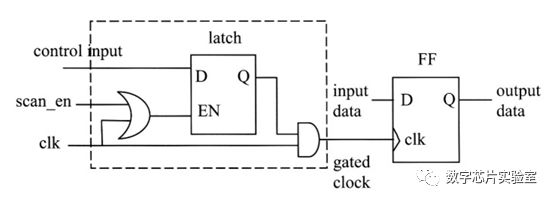

锁存器时钟门控有哪些副作用,如何去修复?

虽然使用锁存器时钟门控是一种很好的降低功耗方法,但是它引入了**可测试性问题。**因为使用锁存器门控时钟时,时钟信号现在仅受输入控制信号的控制。在测试时,如果此信号为低,则时钟信号无法传播。

要解决上述问题,需要添加其他逻辑增强可测试性。一种方法时钟是在锁存器的输入端引入一个控制逻辑,使锁存器在扫描测试期间处于“使能”状态。如下图所示:

一个简单的Verilog代码可以描述上述逻辑,如下:

module gated_ff (in1 , scan_en ,clk , reset_n , cntrl_in , out1) ;

input scan_en , in1 ,clk ,reset_n , cntrl_in ;

output out1 ;

wire gated_clk ,latch_en ;

reg d_latch , out1 ;

assign latch_en = scan_en | clk ;

always@(cntrl_in , latch_en ) begin

if(latch_en)d_latch <= cntrl_in ;

end

assign gated_clk = d_latch & clk ;

always@(posedge gated_clk or negedge reset_n) begin

if(!reset_n)out1 <= 1’b0 ;

else out1<= in1 ;

end

endmodule在大型设计中,上述逻辑可以通过综合工具完成的,无需手动实现。

在RTL设计阶段还有其他的低功耗设计技术么?

1、高频信号通过尽可能少的逻辑。一些必要的逻辑在高频下运行,其余逻辑可以相对较低的频率下运行。

2、仅使用必要数量的触发器来存储数据值,即如果仅使用32位寄存器的4位,则不需要剩下的28位寄存器。通常,未使用的触发器会综合工具优化掉

3、使用芯片片选信号。来自CPU的地址不断变化,不会一直指向所有的模块。在这种情况下,最好在各个模块根据地址译码生成一个片选信号,以减少不必要的信号切换。

4、状态机选择格雷码而不是二进制编码:由于格雷码转换只有一位发生变化,因此触发器切换以及它所驱动的逻辑的切换都会减少。但是,格雷码比二进制编码需要更多的触发器。

5、使用多路复用器而不是片上三态总线,因为三态总线可能会发生总线竞争,此时会导致内部总线短路。多路复用器的选择避免了总线竞争,但会增加逻辑门的数量。三态总线还需要内部上拉电阻和更高的电流驱动。

除RTL级外,有哪些系统级技术,影响芯片的功耗?

1、降低工作电压:功耗和电压的平方成正比,在较低的电压下工作是一种降低功耗的方法。许多工艺厂商都有专为低功耗而设计的库。

2、降低工作频率:功耗和频率成正比。设计可以考虑在较低的频率下工作,然后增加总线宽度,以维持数据速率要求。例如, 100MHz的32位总线的数据传输与50MHz的64位总线相同。

3、降低走线的电容。

在后端分析阶段,可以采用哪些降低功耗的技术?

功耗和时序敏感的逻辑走线更短。因为走线电容是长度,宽度和阻抗的函数,长的走线路径通常具有更高的电容。由于动态功耗与电容成比例,即电容越低,功耗越低。所以,相互通信的逻辑块placement需要彼此相互接近

本文转载自公众号:芯片数字实验室

原文链接:

https://mp.weixin.qq.com/s/-UUNkquRhc8LGs4rhKP9zA

未经作者同意,请勿转载!

推荐阅读

想了解更多内容,欢迎关注芯片数字实验室专栏