提高验证生产力的关键之一是提高验证的抽象层次。

DUT的实际接口是信号级的,我们有必要在事务级管理大量的验证任务,例如

产生激励和收集覆盖率数据。

UVM提供了一组可用于连接各个组件的事务级通信接口。 TLM接口的使用将验证环境中的组件相互隔离开来。当RTL被修改时,UVM验证环境只需要替换事务级接口和DUT信号级接口的****转换。

TLM(transaction-level modeling),事务级建模,是一种用于构建高度抽象组件和模型的建模风格。

在UVM中,事务是一个类对象,uvm\_transaction(从uvm\_object扩展),

包括建模两个组件之间通信所需的任何信息。下面是一个简单的总线协议事务级建模:

class simple_trans extends uvm_transaction;

rand data_t data;

rand addr_t addr;

rand enum {WRITE,READ} kind;

constraint c1 { addr < 16’h2000; }

...

endclass事务对象包括变量,约束以及操作数据的方法。

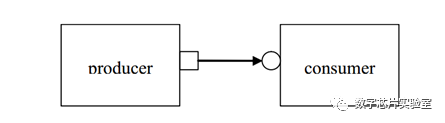

producer生成事务并将它们发送给consumer:

class producer extends uvm_component;

uvm_blocking_put_port #(simple_trans) put_port; // 1 parameter

function new( string name, uvm_component parent);

put_port = new(“put_port”, this);

...

endfunction

virtual task run();

simple_trans t;

for(int i = 0; i < N; i++) begin

// Generate t.

put_port.put(t);

end

endtask

consumerput调用put()。

class consumer extends uvm_component;

uvm_blocking_put_imp #(simple_trans, consumer) put_export; // 2 parameters

...

task put(simple_trans t);

case(t.kind)

READ: // Do read.

WRITE: // Do write.

endcase

endtask

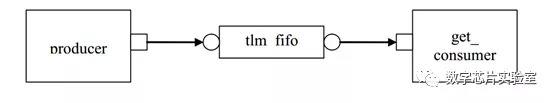

endclass在许多情况下,组件可能需要独立运行,producer创建事务的同时,而consumer同时操作事务。UVM提供了uvm\_tlm\_fifo通道以促进不同进程间的此类通信。producer将事务放入uvm\_tlm\_fifo,而consumer从uvm\_tlm\_fifo获事务:

TLM接口的使用将验证环境中的每个组件与其他组件隔离开来。

较小的组件可以分层次地形成更大的组件。父级组件可以对子级组件进行访问。

愿将你的时光,温柔以待

本文转载自公众号:芯片数字实验室

原文链接:

https://mp.weixin.qq.com/s/AA1cqcKkU1MoWWSa0825VQ

未经作者同意,请勿转载!

推荐阅读

想了解更多内容,欢迎关注芯片数字实验室专栏