上篇文章我们讲到开源RISC-V处理器蜂鸟E203的综合之前的准备工作,包括设计的修改,floorplan def的生成,综合流程、策略和约束的设置等。今天我们将把DCG和DC NXT的具体综合结果作比较,看看他们在效果上有何差异。

在比较结果之前,我们再次把主要的约束声明如下:

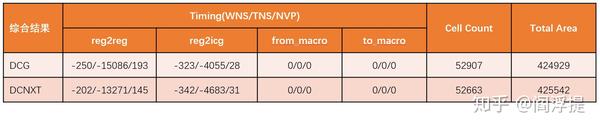

基于以上基本策略,两种工具在综合后的Timing和Area结果比较如下:

DCG vs DC NXT综合结果

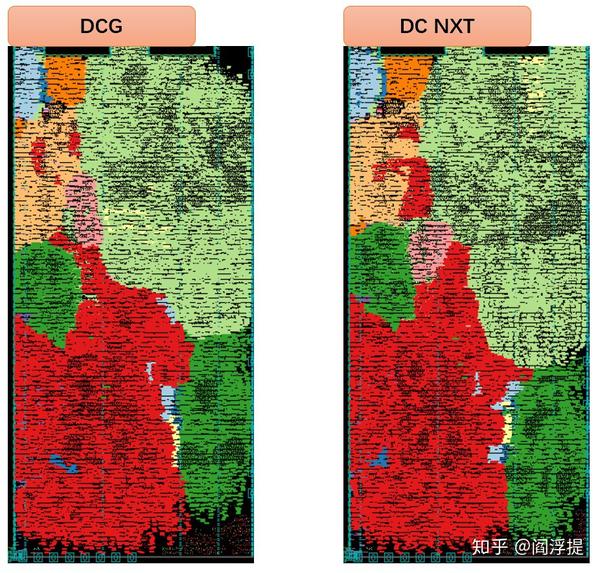

可以看出,DC NXT在reg2reg的timing结果和cell count方面优于DCG,其他方面则DCG占上风。再来看看各自的module分布图:

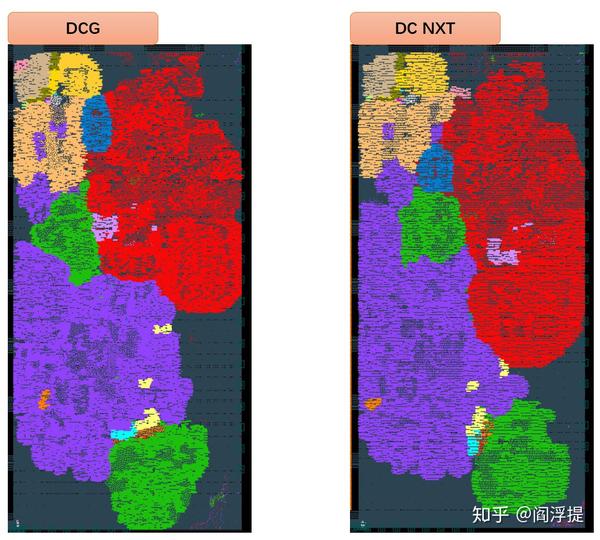

整体上二者除了某些module的大小形态略有不同,在相对位置和分布上没有太大区别。后面我们会再看看placement之后的分布有何变化。

尽管DC NXT在整体的timing TNS上有一些优势,但熟知综合的同学应该知道现在下结论还为时尚早。 主要原因在于综合和PnR结果之间的一致性,亦称correlation。换句话说,在看到真正的PnR结果之前,尤其是当两版综合网表的差距不大的时候,二者的最终QoR是无法确定和比较的。综合和PnR的correlation是一个大课题,即使是当前的DC NXT也没有完全解决,在实际设计中可能会发现DC的结果变差但PnR的结果反而变好的现象。

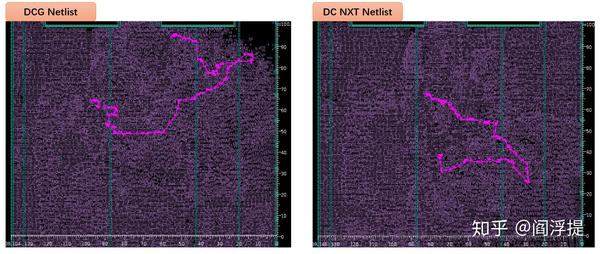

那么上面两版网表的各个阶段的的PnR结果比较如何呢?请看下面两张图:

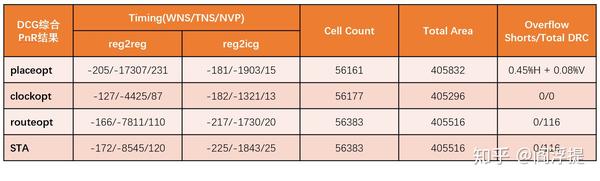

DCG综合网表的PnR结果

DCG综合网表的PnR结果

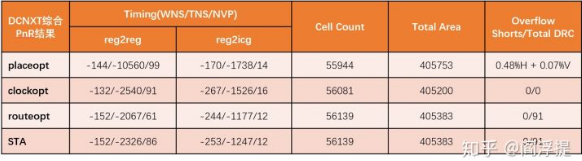

DC NXT综合网表的PnR结果

DC NXT综合网表的PnR结果

对应的placeopt阶段的module分布图比较如下:

至此,结论应该是比较清晰了。从placeopt开始两版网表的差距逐渐拉大,DC NXT版本的网表最终保持了比较明显的优势。而对比二者的module分布可以发现,宏观上大的module位置和形状基本一致,某些小module的位置有一些差异;那么微观上具体到某一条path的走向如何呢?下面我们比较一下完全相同的一条timing path在两个结果中的不同走向:

上图可以看出二者几乎没什么相似性可言。与此同时,这同一条path在两版网表中的逻辑级数也不相同,DCG版为82级而DC NXT版为77级,基本上都是综合逻辑,极少有PnR增加的buffer/inverter。整体上来说DC NXT能够在综合后对某些critical path的做出更出色的优化,从而给PnR更好的起点,进而影响critical path的placement和设计本身的QoR。

至此,本次实验的结果就告一段落了。其实还有很多其他东西可以研究和比较,限于篇幅和时间就不一一赘述,大家有兴趣也可以自己尝试看看是不是有相似的结果。

后续我会把整个实现过程缺失的部分补齐,看看以signoff为标准的前提下整个设计能做到什么样的PPA。另外在实现工具方面Innovus 20增加了一些有趣的更新,Synopsys的Fusion Compiler听说也表现不错,我会尝试在极限条件下比较不同工具的表现,并希望能够分享一些能够对大家实际有用的经验,敬请关注。

最后给大家留个小问题:在实现的过程中placeopt的timing和CTS之后的相差很多,是否正常?如果不正常可能是哪里引起的问题?

相关文章

如果大家有任何后端技术与职业发展方面的问题,抑或关于数字后端感兴趣的技术话题想要了解和探讨,欢迎关注我的知乎专栏: 数字IC后端设计工程师修炼之路同时欢迎关注微信公众号:数字后端芯讲堂,一起探讨技术,共同提升!

本极术专栏也会同步更新芯片设计后端的技术干货,也请关注数字IC后端设计工程师修炼之路。