可测试性(DFT)用来确保设计最终是可以测试的。DFT在增加故障覆盖率(fault coverage)的同时也增加了面积。

影响设计可测试性的主要因素是什么?

1、设计中存在三态总线

2、由一个触发器的输出驱动另一个触发器的复位

3、设计中存在生成时钟

4、设计中存在门控时钟

5、设计中存在锁存器

芯片上片上三态总线对可测试性有什么影响,该如何处理它?

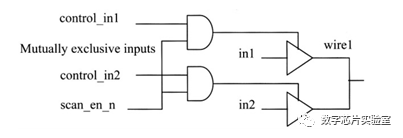

通常,芯片内不应存在三态总线,因为它们消耗更多的功耗。如果芯片上存在三态总线,应注意避免总线竞争,即同一时间在总线上驱动不同的值。总线冲突会消耗更多的功耗,进而导致芯片损坏。在扫描测试阶段避免总线竞争的途径是控制三态缓冲器的使能,即与扫描使能信号进行“与”运算。

在正常工作模式,scan\_en\_n信号为逻辑“1”,允许控制信号通过。

在测试模式下,scan\_en\_n信号为逻辑“0”假定这些使能的控制输入来自触发器的输出。如下图所示:

这些缓冲器的Verilog示例代码如下所示:

assign wire1 = (control_in1 & ~scan_en_n) ? in1 : 1’bz ;

assign wire1 = (control_in2 & ~scan_en_n) ? in2 : 1’bz ;芯片中的一些触发器的复位由其他触发器驱动对可测试性有什么影响,该如何处理它?

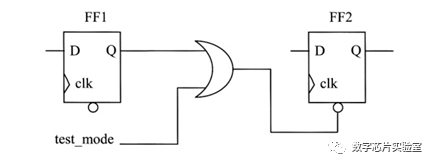

通常,触发器的异步置位或复位来自模块和设计的输入引脚。有时候,不可避免地由一个触发器的输出驱动另一个触发器的异步置位/复位。在这种情况下,在扫描测试期间,如果驱动触发器获得一个测试向量,使其复位另一个触发器,则会发生功能错误。为防止这种情况,复位信号应该和test\_mode测试模式信号异或。如下图所示:

在正常工作模式, test\_mode为1'b0。但是,在测试期间,test\_mode信号为1'b1,从而使异步复位失效。

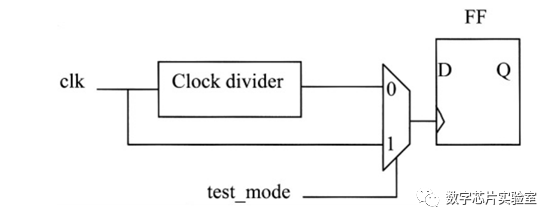

芯片中存在生成时钟对可测试性有什么影响,该如何处理它?

生成时钟由时钟分频器通过触发器或芯片中的PLL产生。

在这种情况下,需要在时钟路径中添加多路复用器,使用test\_mode作为控制信号,多路复用器的输入是常规时钟和生成时钟。

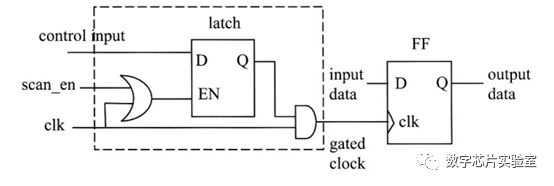

芯片中有门控时钟对可测试性有什么影响,该如何处理它?

在某些设计中,门控时钟是不可避免的,它可以用来降低功耗。因为时钟现在通过组合逻辑,从而无法扫描测试。

解决方法如下:

组合反馈逻辑对可测试性有什么影响,该如何处理它?

在任何设计的任何阶段都应该避免存在组合逻辑反馈。我们应该使用lint和综合工具定期地检查。组合逻辑反馈电路的存在会导致设计中不可预测的逻辑行为。由于组合逻辑环的行为依赖于延迟,我们无法使用任何ATPG算法进行测试。因此,在逻辑上应该避免组合逻辑环。

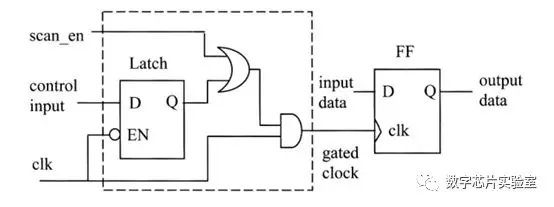

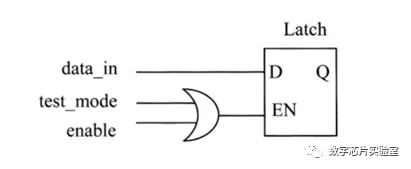

锁存器对可测试性有什么影响,该如何处理它?

为了使锁存器具有可控性,使能和测试模式信号进行异或。如下图

本文转载自公众号:芯片数字实验室

原文链接:

https://mp.weixin.qq.com/s/3PIsm-\_AbAw-dnRgQ7OoJw

未经作者同意,请勿转载!

推荐阅读

想了解更多内容,欢迎关注芯片数字实验室专栏