在数字物理设计流程中需要对多个目标进行优化,包括面积,走线长度和功耗,以及需要确保物理实现之后的网表满足设计的时序要求。

以下将概述芯片数字后端的基本步骤:

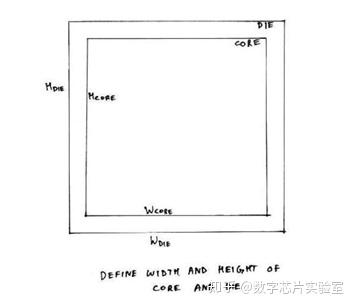

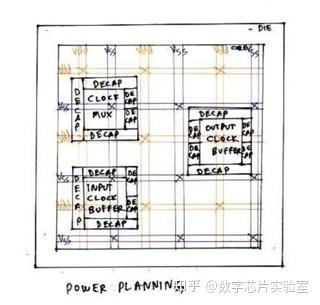

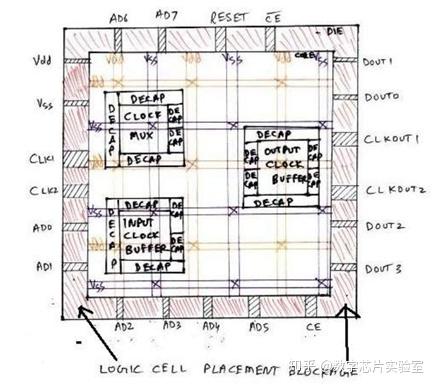

物理设计的第一步是floor planning,定义芯片(die&core)的宽度和高度,也就是芯片的面积。

“core”是芯片的一部分,在其中放置(place)设计的基本逻辑单元。

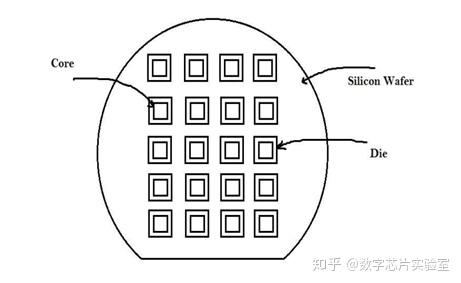

芯片在晶圆(wafer)上制造,晶圆然后切成小块,每块被称为“die”。

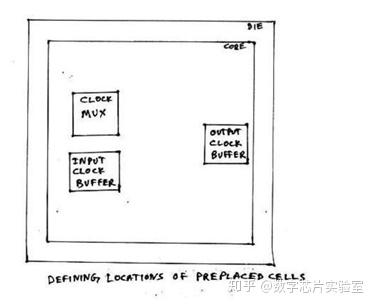

在placement 和routing(P&R)期间,工具会根据floorplan的一些要求放置逻辑单元。 必须在实际P&R阶段之前,预先摆放一些关键模块的位置,如RAM,ROM等等。这些单元被称为“preplaced cells”。

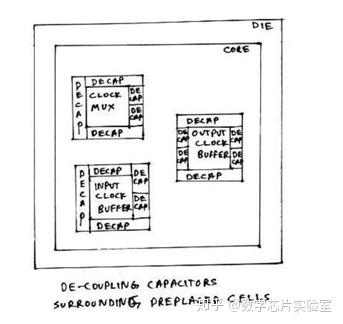

将关键模块摆放之后,围绕关键模块摆放Decap(decoupling capacitors),提高了芯片的可靠性和效率。

通常,在查看任何电路原理图时,我们只有一个“Vdd”和一个'Vss'。 但是,在芯片上,我们需要建立一个电源网络。

在floorplan阶段我们还需要摆放pin(block level)或者pad(chip level)

在floorplan完成(freeze)之后,它将和综合后的门级网表,时序库,物理库和设计约束一起作为布局布线(PNR)工具的输入。这些工具考虑设计约束(constraints),如时钟频率,时序余量(margin), Max capacitance 等,根据算法计算标准单元的位置(Flipflops,AND,OR,BUFFER等)并将它们放在core中。

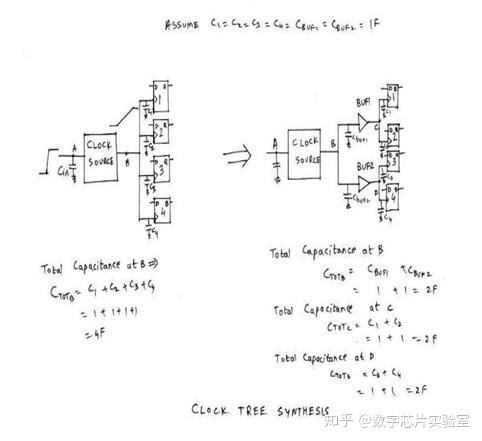

假设,该时钟网络上的maximum capacitance不应超过2F。现在考虑上图中的原理图。时钟节点'B'连接到4个触发器的'clk'引脚。

假设每个触发器的'clk'输入引脚的电容为1F。所以,PNR工具计算节点'B'上的总电容,即4F。然后该工具将此电容数与约束文件中**maximum capacitance,**2F进行比较。

由于节点'B'处的电容超过2F,工具将节点'B'上的负载通过2个buffer分开,如上图所示。它从库中选择buffer(假设每个buffer的输入电容为1F),并构建一个树(时钟树),以满足设计的maximum capacitance约束。整个过程称为'时钟树综合(Clock tree synthesis)。

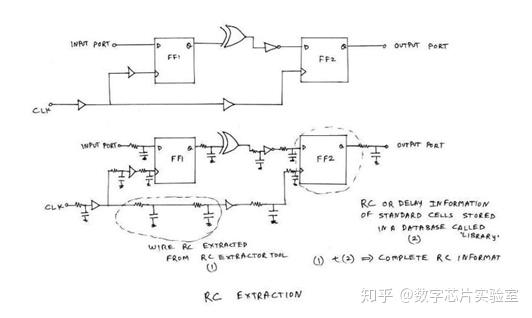

最后,当物理设计完成时,PNR工具会对原网表进行修改。例如:**添加buffer,改变单元大小(size)**等。之后,可以提取RC(resistances、capacitance),并将它们存储在一个单独的文件中,通常称为SPEF(Standard Parasitic Extraction Format)文件。

最后,使用静态时序分析(STA)工具进行timing sign off。

静态时序分析(STA)工具分析设计的路径是否满足约束文件中的时序要求,包括, Setup check,Hold check, Max Capacitance check and Transition Check等。

本文转载自公众号:芯片数字实验室

原文链接:https://mp.weixin.qq.com/s/12QIZioQkNeRTuCGzf1ybg

未经作者同意,请勿转载!

推荐阅读

想了解更多内容,欢迎关注芯片数字实验室专栏