在ASIC设计的早期,逻辑设计师使用原理图或电路编辑工具设计电路。随后,出现了两种硬件描述语言:VHDL、Verilog

随着逻辑综合工具的引入,代表电路功能的Verilog模型可以被综合成实际的电路,此后便可以采用自上而下的高效的设计方法。 设计者可以在寄存器传输级(RTL)对电路建模,然后使用综合工具转换为门级电路。

在今天的ASIC设计流程中,电路设计以RTL格式描述,和设计约束一起被综合成门级电路描述,最终导入到物理综合工具中进行物理实现。

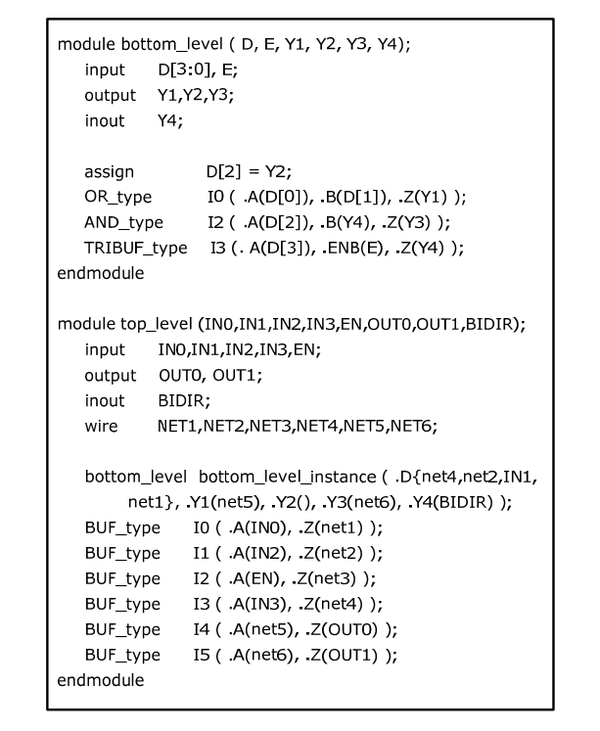

在ASIC物理设计中,只有少数门级Verilog结构用来描述电路,同时网表是区分大小写的,如module, endmodule, input, output, inout, wire和assign

Verilog中最基本的元素是具有相应输入输出端口的module定义。一个module可以是简单的门或复杂的网络。module中的端口可以是单比特或多位宽,每个端口可以定义为input,output或输入输出(即双向)端口。模块内部元素的网络连接由wire语句描述。

为了提高可读性, 单行注释以“//”开头,多行注释以“/ *”开头,并以“* /”结尾。

Verilog语言中的模块以关键字module开始,以关键字endmodule结束。每个模块名称必须是唯一的。

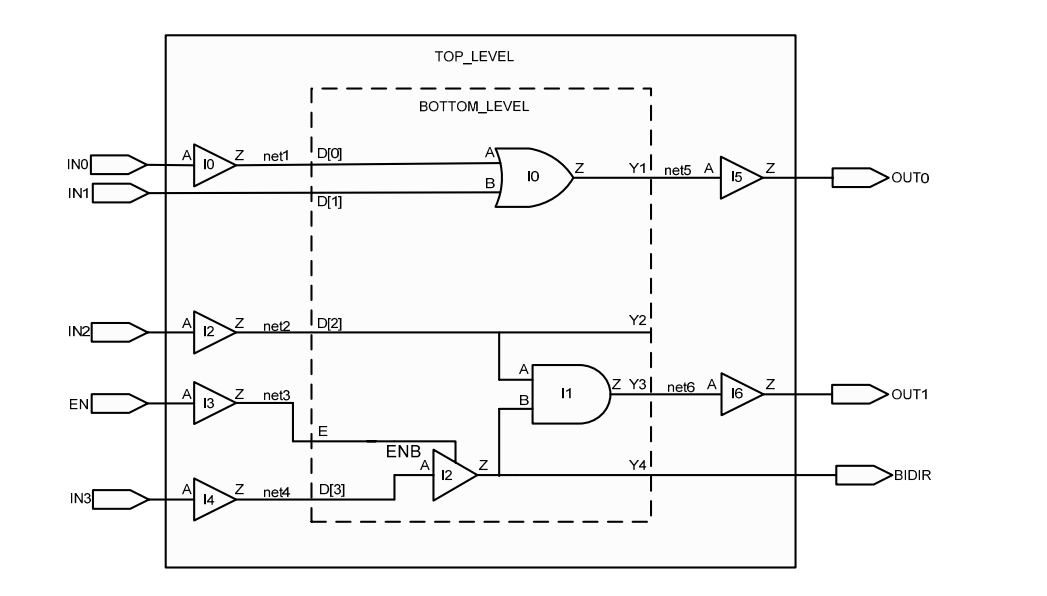

下面分别是Verilog描述和对应的电路图:

bottom\_level模块有一个由关键字assign描述的连续赋值语句。

虽然assign语句是行为级描述,但被广泛用于结构Verilog网表。 这意味着在导线两端具有两个不同的名字。

所以在ASIC物理设计中,需要小心处理assign关键字。在逻辑综合输出网表时和ASIC物理验证时都需要避免assign关键字导致的问题。

最常用的技术之一是使用buffer替换assign关键字。

本文转载自公众号:芯片数字实验室

原文链接:https://mp.weixin.qq.com/s/sMNK6aeb2uaM\_luBVCVv0A

未经作者同意,请勿转载!

推荐阅读

想了解更多内容,欢迎关注芯片数字实验室专栏