在之前的IC设计中,关注的参数主要是性能(timing)和面积(area)。 EDA工具在满足性能要求的情况下,最小化面积。功耗是一个不怎么关心的问题。 CMOS工艺在相对较低的时钟频率下具有相当低的功耗,漏电流可忽略不计。

然而,近年来,随着晶体管密度和时钟频率的显著增加,功耗也极大地增加。同时,随着电源电压和晶体管阈值电压降低,漏电流成为一个很大的问题。 结果就是,功耗已达到不可接受的限度,功耗问题变得和性能、面积一样重要了。

高功耗会在运行期间导致过高的温度。 这意味着必须使用昂贵的陶瓷芯片封装,代替塑料封装,并且在产品工作时,通常需要复杂昂贵的散热器和冷却系统。

笔记本电脑和手持电子设备可能会发热,变烫。较高的工作温度也会降低芯片的可靠性。

高功耗还会缩短便携式设备(如笔记本电脑、手机和个人电子产品)的电池寿命。 随着产品中添加更多的功能,功耗会增加,电池寿命会进一步缩短。 电池技术已落后于功耗的增加。

功耗的另一个影响就是数以百万计的计算机、服务器和其他大规模使用的电子设备的供电成本。即使微处理器或其他芯片的功耗略微降低,也可以为用户节省大量的总成本,并且对环境也有好处。

设计人员必须考虑两种类型的功耗,动态功耗和静态功耗。 动态功耗是指在晶体管开关期间的功耗,因此它取决于时钟频率和开关活动。 静态功耗是由于晶体管泄漏电流而产生的功耗,与时钟频率或开关活动无关。

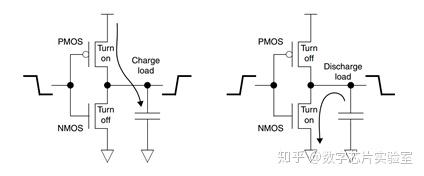

动态功率是电路逻辑转换期间消耗的功耗,由两个部分组成,开关功耗和短路功耗。 开关功耗来自对电路负载电容充放电的功耗。 短路功耗来自在电路逻辑转换期间,流过PMOS-NMOS的短路电流。

开关功耗的原因如图1所示。 反相器输出从0到1的转换期间通过PMOS对负载电容充电,从1到0的转换期间通过NMOS对负载电容放电。

所以,动态功耗取决于电源电压和电容负载以及时钟频率和开关活动。

在早期的CMOS技术中,漏电流可以忽略不计。 然而,随着晶体管尺寸和阈值电压降低,泄漏功耗正在变得越来越大,有时甚至接近动态功耗水平。

无论时钟和晶体管开关活动如何,只要向晶体管供电,就会发生漏电流。 通过减慢或停止时钟不能减少泄漏功耗。

但是,可以通过降低或关闭电源电压来减少或消除泄漏功耗。

后续,我们将介绍如何在IC设计的前后端流程中降低功率消耗。

本文转载自公众号:芯片数字实验室

原文链接:https://mp.weixin.qq.com/s/sMNK6aeb2uaM\_luBVCVv0A

未经作者同意,请勿转载!

推荐阅读

想了解更多内容,欢迎关注芯片数字实验室专栏