逻辑综合是设计从RTL到Netlist翻译优化的过程,类似于Design Compiler集成PrimeTime时序分析优化引擎,同样也集成了Power Compiler功耗分析优化引擎。

越高的设计抽象水平,可以优化的功耗空间就越大。

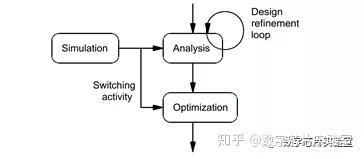

在逻辑综合过程中,针对不同的设计目标**(性能、面积和功耗)都需要经过Simulation**、Analysis和Optimization过程。

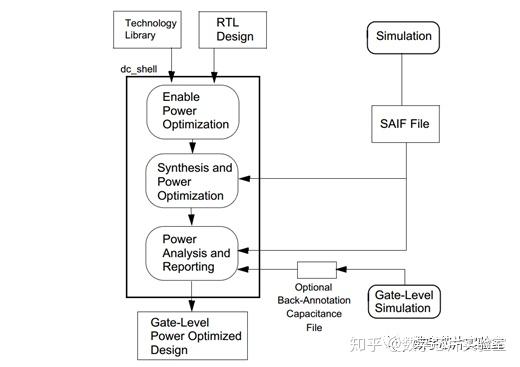

对于功耗目标,Power Compiler功耗分析优化引擎除了需要输入设计和工艺库之外,还需要仿真的设计内部信号的开关活动描述saif(Switching Activity Information Format)文件。

和设计的功能仿真一样,门级网表仿真也需要寄生参数sdf(Standard Delay Format)文件。

在功耗分析的过程中,Design Compiler输入的库文件需要包含功耗相关信息。

在功耗优化的过程中,也需要库文件包含额外的Cell,例如使用ICG cell优化动态功耗、使用MTCMOS优化静态功耗。

另外,在芯片物理实现流程中,集成功耗分析优化引擎也可以指导低功耗物理实现。根据动态功耗计算公式,物理实现过程中也可以通过影响负载电容,进而优化动态功耗。

但是在物理实现流程中,功耗优化的空间远小于算法级和RTL级。

本文转载自公众号:芯片数字实验室

原文链接:https://mp.weixin.qq.com/s/gzag9F0mWYOXuSehpafDlg

未经作者同意,请勿转载!

推荐阅读

想了解更多内容,欢迎关注芯片数字实验室专栏