源自微信公众号 “数字芯片实验室”

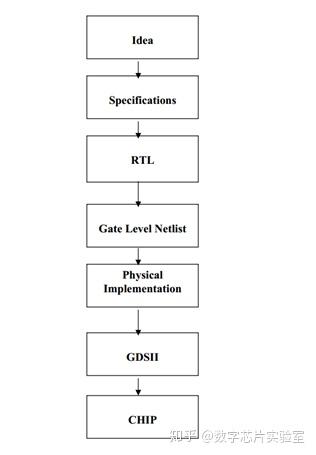

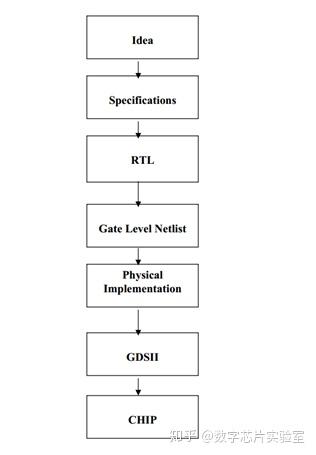

要设计芯片,需要知道想要设计芯片的内容(Idea)。 在ASIC设计流程中的每一步,Idea都在不断地改变着表现形式。 ASIC设计流程的第一步就是把Idea描述成规格(Specifications)。

Specifications包括:

•设计的目标和约束。

•功能

•性能,如速度和功耗

•面积

•制造工艺和设计方法

下一个流程是给出设计的结构和功能描述(Structural and Functional

Description)。 这意味着必须决定使用什么样的设计架构,例如 RISC / CISC,ALU,流水线等......

为了使设计复杂系统更容易,还需要将系统划分为几个子系统。 这些子系统的功能也在Specifications中定义了。

一旦定义了block\_level和top\_level,就要开始使用布尔表达式、有限状态机、组合逻辑、时序逻辑、原理图等进行设计的实现了。这一步称为RTL级逻辑设计(Register Transfer Level)。 RTL设计通常用硬件描述语言(Verilog、VHDL)描述。 硬件描述语言(HDL)是一种用于描述数字系统的语言,例如逻辑开关、微处理器、存储器、触发器等。 这意味着,通过使用HDL可以描述任何level的硬件(数字)。在此阶段需要进行验证以确保设计功能符合Specifications。

功能验证(Functional Verification)完成后的流程是逻辑综合(Logic synthesis),使用

Design Compiler (Synopsys),Genus(Cadence)等综合工具将 RTL转换为优化后的门级

网表(Gate Level Netlist)。综合工具输入RTL硬件描述和标准单元库(Standard cell

library),生成门级网表。 标准单元库是当今IC设计的基本逻辑模块。综合工具在进行逻

辑综合时,需要考虑约束(Constraints),如时序,面积,可测性,和功耗。 综合工具通

过计算设计各种实现方式的代价函数(cost function)来满足设计约束条件。 逻辑综合在找

到满足约束的实现之后,就会输出一个结构级的门级网表,网表中没有任何行为级的描述。

在此阶段,还可以验证门级网表的功能是否发生变化。

ASIC流程的下一步是门级网表的物理实现(Physical Implementation)。 门级网表被转

换为设计几何表示。设计的几何表示是设计的布局信息。 布局需要满足设计库中指定的设

计规则,用以满足工艺制程的DRC规则。 物理实现步骤包括三个子步骤:Floor

planning->Placement->Routing。 物理实现的输出是GDSII文件。 这是代工厂制造ASIC

使用的文件。该物理步骤由IC Compiler (Synopsys)、Innovus (Cadence)等软件执行。

后续还要进行物理验证(Physical Verification)。

对于任何以特定时钟频率工作的设计,必须进行时序分析(timing analysis)。

我们需要检查设计是否满足Specifications中提到的时序要求。 这是通过静态时序分析

(Static Timing Analysis)工具完成的,例如Primetime(Synopsys)。 它通过检查设计

中所有的时序路径,来验证设计的时序是否存在违规(timing violations)。例如:建立时

间(setup),保持时间(hold)。

在物理实现,时序sign-off之后,设计就可以进行制造(Fabrication)了。

在制造之后,晶片是切成单个芯片,然后经过封装和测试。

本文转载自公众号:芯片数字实验室

原文链接:https://mp.weixin.qq.com/s/3T0wSk6H1CrtaOtRoRs68Q

未经作者同意,请勿转载!

推荐阅读

想了解更多内容,欢迎关注芯片数字实验室专栏