大型设计通常根据功能划分成层次化的模块(block),使得前端设计验证和物理实现更易管理。

另外,在逻辑综合过程中,合理的设计划分(Design Partitioning),让综合工具充分优化设计中模块边界的时序和面积。

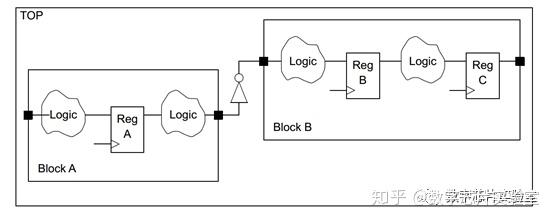

对于上图中的设计划分,RegA和RegB之间的组合逻辑被分别划分在模块A和模块B,并且它们之间还存在**“胶合逻辑(glue logic)”(一个反相器)**将模块A和模块B集成在一起。

Design Compiler默认无法跨越层次边界进行优化,也就是说无法对其中的胶合逻辑进行优化。

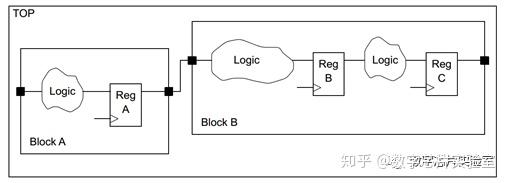

上图所示的设计划分将模块A和模块B之间的组合逻辑,以及“胶合逻辑”,完全移入模块B。

此时, Design Compiler就可以在模块B内优化所有组合逻辑,即实现更好的时序和面积的门级网表。同时,简化底层模块输入和输出的时序约束。

上图在RegA的输出,而不是在RegB的输入划分设计是因为Design Compiler可以选择更加复杂的触发器进一步优化模块A和模块B之间的组合逻辑。

当然,也没有必要同时寄存器输出和寄存器输入,这会造成寄存器资源浪费。

为了获得更好的综合结果,避免在不同的模块之间存在组合逻辑,将模块之间的组合逻辑和下游寄存器划分在同一模块中。

在之前的很多文章都提到过,数字IC设计流程中的工程师和EDA工具的交互,手动和自动,显式和隐式等等。对于设计划分也是一样,如果设计划分不够理想,我们也可以通过命令ungroup和group重新划分设计。

Design Compiler工具的compile\_ultra命令默认也会执行设计自动划分,对设计进行充分优化。

本文转载自公众号:芯片数字实验室

原文链接:https://mp.weixin.qq.com/s/m9f5CEOCL2TIqhZF55um4Q

未经作者同意,请勿转载!

推荐阅读

想了解更多内容,欢迎关注芯片数字实验室专栏