源自微信公众号 “数字芯片实验室”

在数字系统设计中,有一些重要的设计级别概念:

•行为级(Behavior Level):通过行为级算法描述数字系统。

•寄存器传输级(Register Transfer Level):在寄存器传输级,通过寄存器之间的数据传输进行电路功能设计, 例如有限状态机。

•门级(Gate level):数字系统按门级(AND,OR,NOT,NAND等等…)描述。通常不会进行门级设计,门级网表网表一般是通过逻辑综合的输出。

RTL可以用Verilog或VHDL描述。

Verilog是一种用于描述数字系统的硬件描述语言(HDL),例如Latches,Flip-Flops,组合逻辑,时序逻辑等......

基本上,你可以使用Verilog来描述任何类型的数字系统。

设计通常以top-down的方式编写的。 系统具有层次结构,使设计和调试更容易。 verilog模块的基本框架如下:

模块可以引用其他模块以形成层次结构。

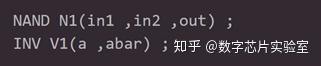

模块实例化(module instance)时,每个模块实例都包含被实例化的模块名称(例如NAND或INV),实例名称(在当前模块中的那个实例名称是唯一的)和端口连接列表。

上例中的实例名称是'N1和V1',它必须是唯一的。模块端口连接可以按顺序给出(位置映射),或者显式连接(命名映射)。通常首选是命名映射,因为降低了错误的可能性。

1.按名称进行端口映射:

INV V2(.in(a),. out(abar));

2.按顺序进行端口映射:

AND A1(a,b,aandb);

此时,端口列表顺序必须相同。

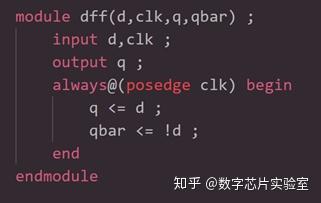

下面是一个简单的Verilog示例代码:D触发器

数字电路设计可以分为组合逻辑或时序逻辑。硬件描述语言用于建模数字电路的RTL,而RTL不过是组合和时序逻辑。

不是所有用Verilog编写代码都是可综合的。我们需要确保我们的代码综合成我们想要的电路。

大多数情况下,Verilog中一些时间相关的任务无法综合。例如,wait, initial语句, 延迟等。

可以在Verilog中建模电平敏感和边沿敏感的电路行为。两者都可以使用verilog中的always语句块建模。

“always”语句块建模组合电路时,每个输出都依赖于敏感列表。如果没有完全指定组合电路,可能会综合处到锁存器(latch)。

本文转载自公众号:芯片数字实验室

原文链接:https://mp.weixin.qq.com/s/zaWsH06DLQWqqCoYSRoQLw

未经作者同意,请勿转载!

推荐阅读

想了解更多内容,欢迎关注芯片数字实验室专栏