NC可用于数模混合仿真,即用verilog语言给画的电路图添加输入激励信号,然后查看输出信号,以验证电路是否正确。。

首先,nv虽然在cadence里面有集成,但是cedence自带没有verilog的仿真器,因此需要装verilog仿真器,也就是IUS。这里所用的是IUS9.

IUS需要破解,破解方法见网上所说,这里只说怎么用NC来仿真电路。

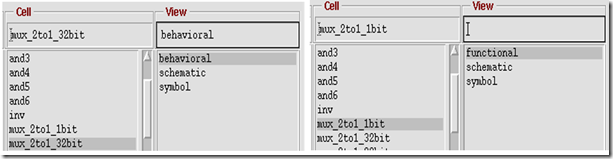

对于一个电路,要能用verilog来仿真,首先,电路的元件就必须要有verilog描述的模型。

也就是在元件view中,要有functional或者是behaviour。

这里用的库是NCSU_Digital_Parts库。

该数字库有对门有HDL描述,可以进行仿真。

以下以二进制加法器为例。

二进制加法器,接受两个加数和一个进位信号,输出一个和和进位信号。

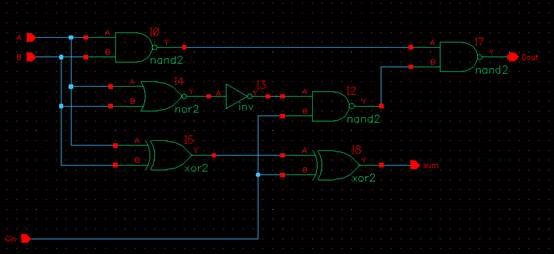

半加器

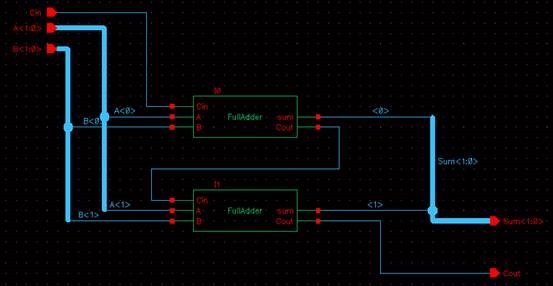

全加器,下图中的fulladder为上图原理图的符号例化。

首先,新建原理图,原理图的名字叫two_bit_adder。

原理图建好后,保存。

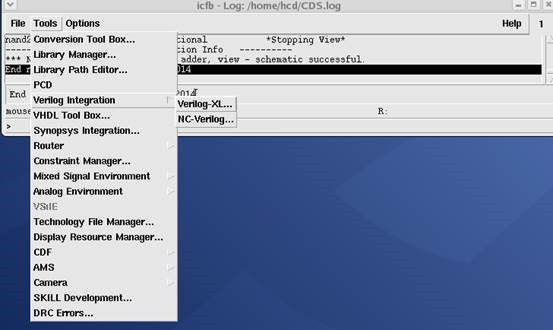

回到CIW界面,tools->Verilog interation->NC_verilog,打开软件NC。

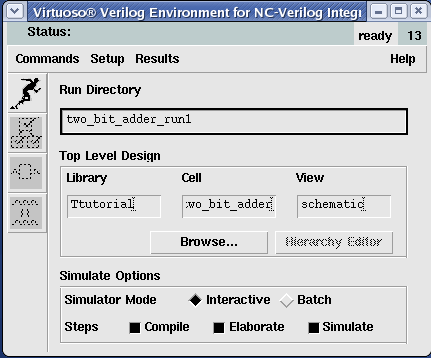

在弹出的界面中,点击browser,选择刚才所画的原理图,two_bit_adder。

Run directory是填写的运行目录,这里一般写 原理图的名字_run1。如two_bit_adder_run1。

然后选择commands->initialize design 或者点击界面左边那个跑步的图标。

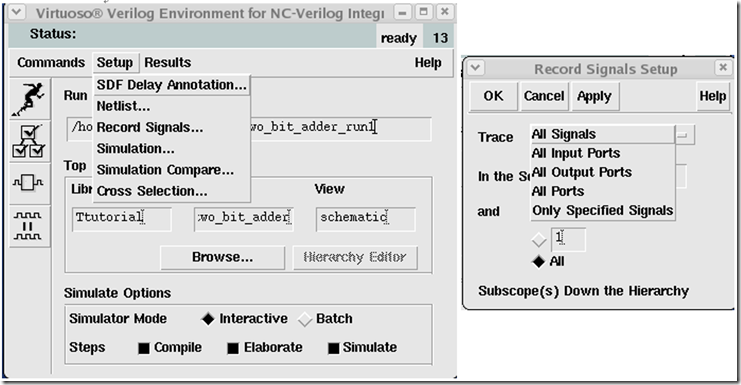

接着setup->record signals。这个是设置所查看的信号。

如上右图所示:可选择查看的信号类型。这里选择所有信号。

下面的1和all选项,是表示要看到模块的第几层。选择1就是看到模块下第一层,all是可以看到所有层。

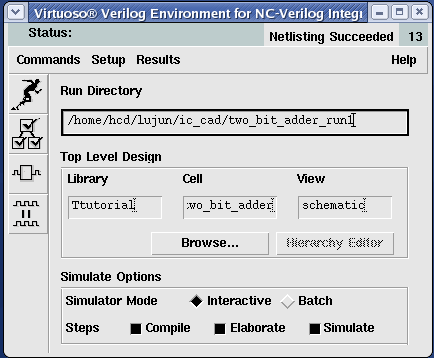

然后点击左边的第二个图标,三个勾的图标,生成网表。右上角有succeeded表示生成网表成功。

接着就要加载测试的文件了。也就是我们用verilog写的输入激励信号。

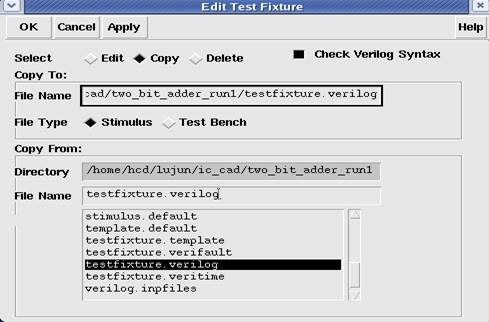

Commands->edit test fixture

这里我们用自带的模板来生成我们的激励文件。按如下图所示,设置好后,点击apply。

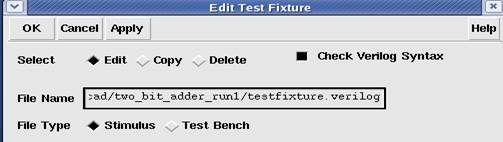

选中edit,点击apply。进入编辑激励文件。

文件是以vi打开的,vi的使用请自行上网查询。按照如下所写,然后保存退出。

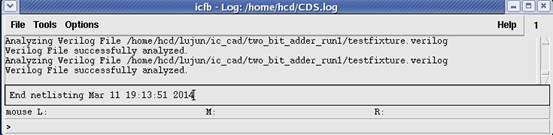

如果所写的激励程序没有错误,那么在CIW主界面会显示文件成功分析。

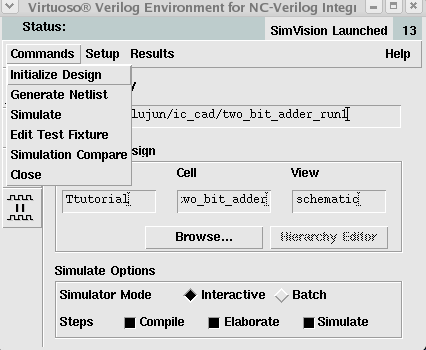

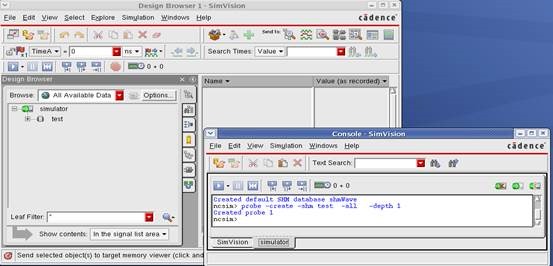

在nc主界面,然后点击左边第三个图标,启动仿真。会弹出两个界面

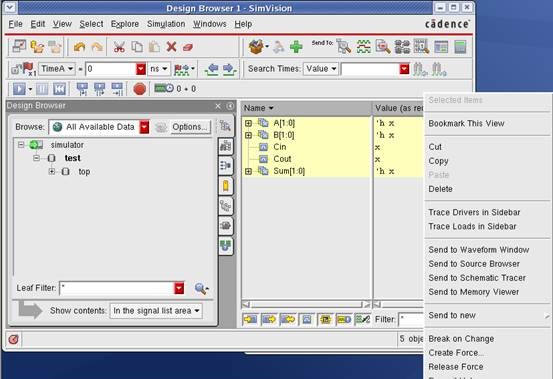

选中design界面,选中design brower中的test,则右边会出现顶层的信号。选择所有信号,点击右键,选择send to waveform window。

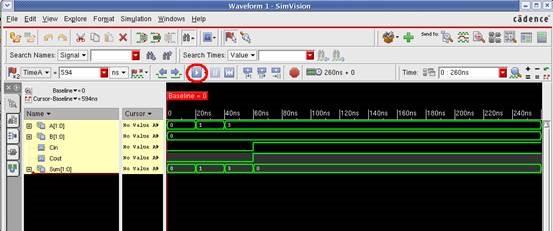

然后会弹出波形界面。选择启动仿真,就会出现波形了。查看波形可验证所画的电路图是否实现了加法器功能。