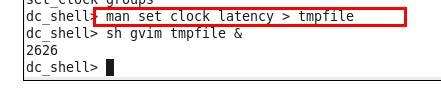

DC中,约束的时候,需要添加关于latency的约束。约束latency的命令是set_clock_latency。使用man命令,查看。这里,有个技巧,可以将man的结果重定向到一个临时文件中,可以可以方便查看。

sh表示使用shell命令。

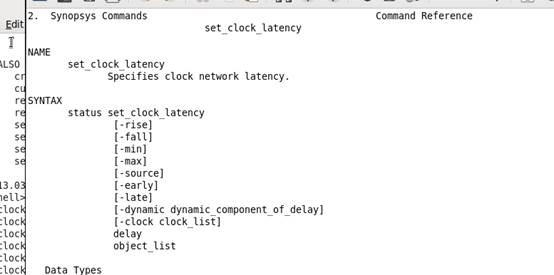

使用的方法如图所示,可以看出该命令有很多参数的。

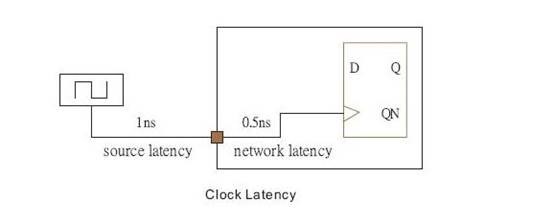

先来说一下-source参数。DC中将latency分成了两部分,一个是芯片外的source latency,一个是芯片内的network latency。

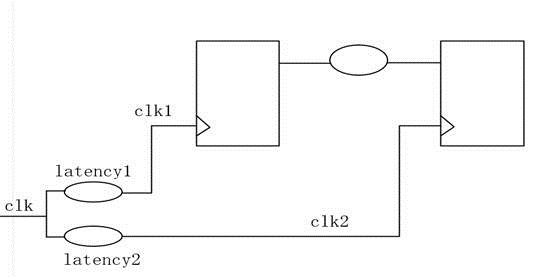

用下面一个图就可以说明了。

source latency是外部clock信号来源到芯片的clock输入端的delay,而network latency是指芯片clokc输入端到flip-flop clock输入的delay。所以对于上面的图,所施加的约束就是 set_clock_latency -source 1 [get_clocks CLK]

set_clock_latency 0.5 [get_clocks CLK]

当不指定-source参数时,表示是对network latency进行约束。

对于-rise和-fall,这两个参数比较简单,针对时钟的上升沿还是下降沿进行约束,不指定的话,表示对上升沿和下降沿约束的参数是一样的。

对于-min和-max,这两个参数从命名就知道作用是什么。这里就不解释了。

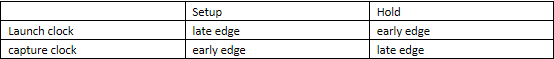

重点是-early和-late参数的理解。在网上找到这样的描述

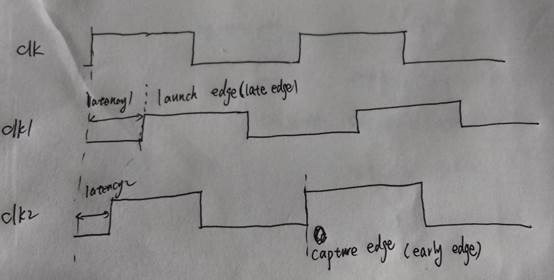

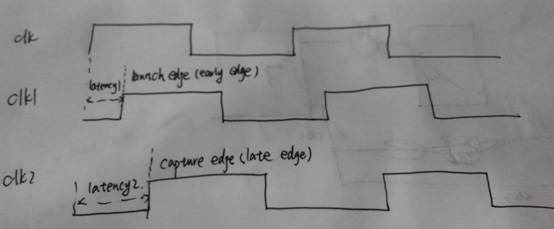

For setup analysis, Design Compiler uses the late edge for the launching flip-flop and the early edge for the capturing flip-flop. For hold analysis, Design Compiler uses the early edge for the launching flip-flop and the late edge for the capturing flip-flop.

说明这两个参数是对于建立时间和保持时间分析有用的。

在eetop上看到有人举例子:

set_clock_latency 4 -source -early ….

set_clock_latency 5 -source -late….

在计算setup 的时候 : launch clock 上的latency 用的是5,capture clock上的latency 用的是4.

在计算hold 的时候: launch clock 上的lactency 用的是4,capture clock的latency 用的值是5.

其实这两个参数,就是指定在建立时间和保持时间分析的时候,launch clock和capture clock的latency。有了这两个参数,能加紧约束。

如果上面的例子你没有看懂的话,说明你的建立时间和保持时间分析基本功还不够到位了。

下面,我就来说明一下:

对于建立时间,考虑上面的电路图。从时钟clk出来到寄存器的clk端口是有延时的,对于clk1的延时是latency1,对于clk2的延时是latency2。当然这延时是不确定的,有可能latency1大于latency2,也可能反过来。

考虑最差的情况。latency1大于latency2。这样的话,有效的时钟周期时间就变成T-(latency1-latency2)了,那对建立时间的约束就变紧了,因为有效周期小了。

对于保持时间,还是上面的电路图。考虑最差的情况,latency1小于latency2。约束的保持时间延时就要大于(latency2- latency1)了,对保持时间的约束也就变紧了。

以上,就是分析了这两个参数的作用。

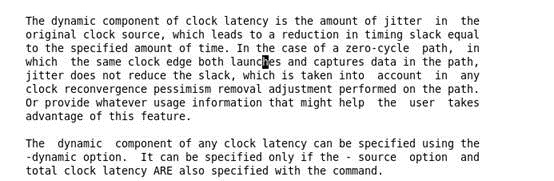

-dynamic参数,是指定时钟源的抖动的时间。

delay,指定latency的延时值。

object_list,指定施加latency约束的目标信号

理解了上面的参数的信息,对于latency约束就比较容易了。