随着当今芯片中使用越来越多的时钟,通常在芯片运行时需要对时钟进行切换。

我们可以在芯片中复用两个不同频率的时钟源,由内部逻辑控制多路复用器的选择信号。

所复用的两个时钟频率可以完全无关,也可以是彼此的倍数。在任何一种情况下,都有可能在时钟切换时产生毛刺。时钟上的毛刺会造成整个系统功能的故障,因为它可能被某些寄存器认为是时钟边沿而被其他寄存器忽略。

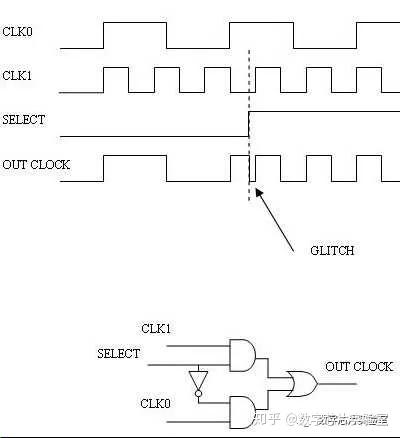

上图显示了使用AND-OR型多路复用器逻辑的时钟切换的简单实现。

多路复用器有一个名为SELECT的控制信号,

当设置为“SELECT= 1'b0”时,它将CLK0传播到输出,当设置为“SELECT = 1'b1”时将CLK1传播到输出。当SELECT值改变时,可能会产生毛刺。

上图中的时序图显示了当SELECT控制信号发生变化时,输出OUT CLOCK如何产生毛刺。

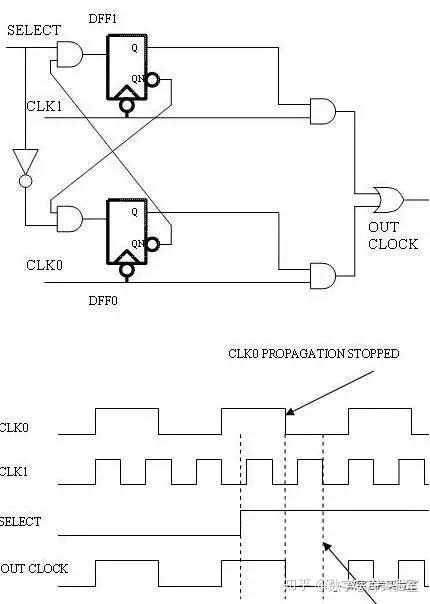

上图显示了防止时钟切换出现毛刺的解决方案。在每个时钟源的选择路径中插入一个负边沿触发的D触发器。在其他时钟不使能后,在时钟的下降沿寄存选择控制信号,可以防止输出信号出现毛刺。

在时钟的下降沿寄存选择信号可确保在时钟处于高电平时输出端不会发生变化。

在上面的时序图中,SELECT信号从0到1的转变,在CLK0的下降沿停止CLK0传播到输出,然后在CLK1的后续下降沿开始CLK1传播到输出。

该电路中有三个时序路径需要特别考虑 - SELECT控制信号到两个负边沿触发触发器,DFF0输出到DFF1的输入,DFF1的输出到DFF0的输入。

如果这三条路径中的任何一条路径上的信号与触发器时钟边沿靠近,则该寄存器的输出很可能变为亚稳态。

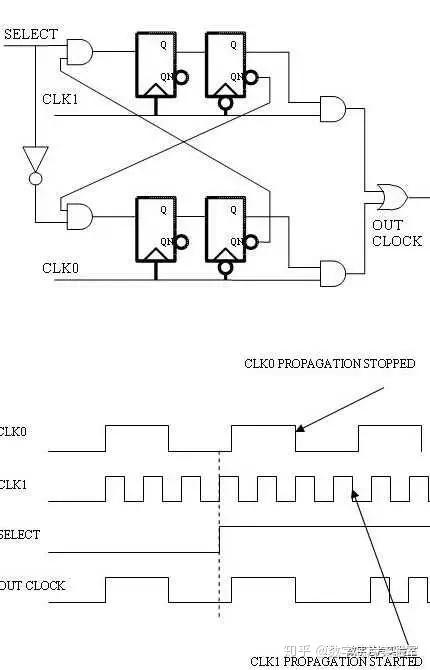

如上图所示,通过为每个时钟源添加一个额外级的正边沿触发器,稳定数据来防止亚稳态的传播。

上述glitch free的时钟切换技术以非常小的开销避免在时钟切换时产生毛刺。这些技术可以扩展到两个以上的时钟切换。

对于多个时钟切换,每个时钟的选择信号将接受其他所有时钟源的反馈信号。

本文转载自公众号:芯片数字实验室

原文链接:https://mp.weixin.qq.com/s/WzcfQeT1RMTUSShetI5n8Q

未经作者同意,请勿转载!

推荐阅读

想了解更多内容,欢迎关注芯片数字实验室专栏,由于工具,你可以专注在更重要的事情上。