纯粹的单时钟同步设计是一种奢望。大部分的ASIC设计都由多个异步时钟驱动,并且对数据信号和控制信号都需要特殊的处理,以确保设计的鲁棒性。

大多数学校的课程任务都是完全同步(单时钟)的逻辑。在真正的ASIC设计领域,单时钟设计非常少。

亚稳态

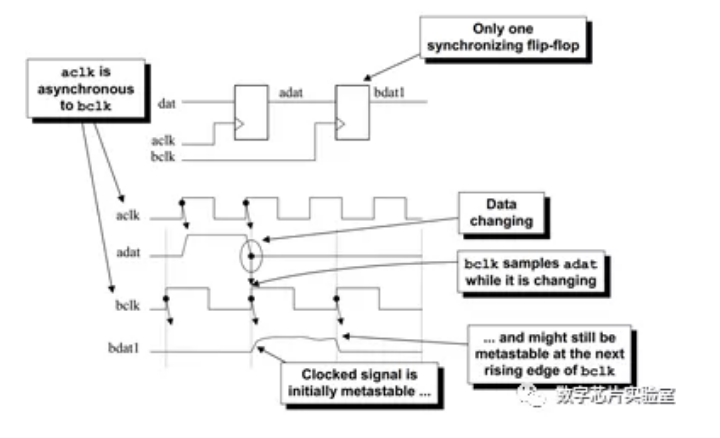

上图显示了在一个时钟域中生成的信号被采样时发生的同步故障,因为数据变化太接近另一个时钟域的时钟信号的上升沿。

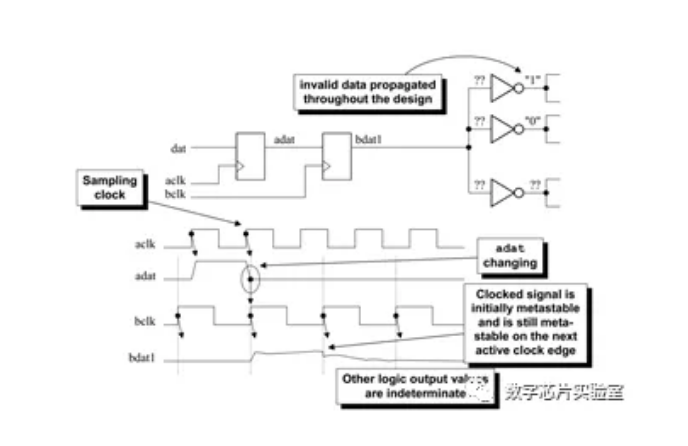

同步失败是由于亚稳态在下一次采样时还未收敛到稳定状态引起的。下图是亚稳态在整个设计中继续传播的事例

设计中使用的每个触发器都具有指定的建立(时钟上升沿之前数据必须保持不变)和保持(时钟上升沿之后数据必须保持不变)时间。由建立和保持时间指定的时间窗口保证数据信号变化不会太接近时钟信号的采样时间,从而防止设计变成亚稳态。

同步器

同步器是对异步信号进行采样并同步到采样时钟的模块。

数字设计人员使用的最常见的同步器是两级触发器同步器,如下图所示

第一个触发器将异步输入信号采样到新的时钟域并等待一个完整的时钟周期,以使得阶段1输出信号上的亚稳态衰减。然后对阶段1信号进行采样进入阶段2,此时阶段2信号是一个稳定有效的信号,并且同步到了新的时钟域。

理论上,在阶段1信号被采样时,也可能仍然是亚稳态,使得阶段2信号也变为亚稳态。

平均故障间隔时间(MTBF)是包括用于产生数据和采样数据的时钟频率等多个变量的函数。

对于大多数情况,两个触发器同步器足以消除所有可能的亚稳态。

静态时序分析

静态时序分析是验证设计中的每个信号路径是否满足所需时序要求的过程。静态时序分析不是用于验证设计的功能,只验证设计是否符合时序目标。从理论上讲,时序验证可以通过运行完备的布局布线之后的门级仿真来实现,其中利用SDF文件反标了实际的延时值。这通常被称为动态时序验证。

静态时序分析与动态时序验证相比有三个主要优点:(1)静态时序分析工具可以验证任何两个时序器件之间的每条路径,(2)静态时序分析不需要生成任何测试向量,(3)静态时序分析工具比动态时序验证快几个数量级。

对具有异步时钟的模块进行时序分析是不准确的,并且大部分都是毫无价值的,因为异步时钟之间的时序关系总是在变化。因此,静态时序分析工具必须检查异步时钟之间的无限数量的相位关系。

事实是,我们可以假设一个时钟域传递到另一个时钟域的信号总是会违反时序器件上的建立时间和保持时间。

这就是为什么需要同步器来缓解信号从一个时钟域传递到另一个时钟域时亚稳态问题的原因。

对于具有两个或更多异步时钟的RTL模块,设计人员需要通过“setting false paths”来指示静态时序分析工具忽略从一个时钟域到另一个时钟域的信号路径的时序检查。

除非遵守接下来的指南,异步时钟分析将会是一项单调乏味且容易出错的工作。

时钟命名约定

指南:使用时钟命名约定来识别设计中每个信号的时钟源。

原因:命名约定可帮助所有团队成员识别设计中每个信号的时钟域,还可以使用脚本中的正则表达式来对信号进行分组,以便更容易地进行时序分析。

每个设计团队都有自己的时钟命名约定。例如, uClk前缀标志微处理器时钟,vClk前缀标志视频时钟,dClk前缀标志显示时钟。

每个信号都与设计中的一个时钟域同步,所以每个信号名称必须包含一个标识该信号时钟域的前缀字符。任何属于uClk时钟域的信号都会有u前缀,例如uaddr,udata,uwrite等。任何属于vClk时钟域的信号都会有一个v-prefix,例如vdata,vhsync,vframe等。设计中其他时钟域中的信号命名都是用类似的方式命令。

命名约定对设计团队的生产力有很大贡献。使用这种技术,ASIC设计团队的任何工程师都可以轻松识别任何时钟域的信号,因此设计团队中存在更少的混淆。

设计划分

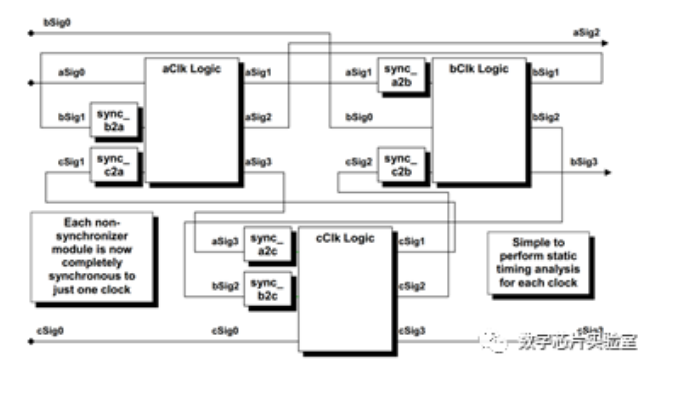

指南:每个模块只允许一个时钟。

原因:在单时钟模块上更容易实现静态时序分析和创建综合脚本。

指南:为从一个时钟域传递到另一个时钟域的每组信号创建一个同步器模块。

原因:信号从一个时钟域传递到另一个时钟域都会有建立时间和保持时间的问题。

综合脚本和时序分析

遵循之前的准则,只允许每个模块只有一个时钟驱动,进入异步时钟域的信号都需要经过同步器同步。

这时,多时钟域的综合现在变成了时序路径分组问题,识别false path然后执行最小-最大时序分析。

分组

将所有非同步器模块根据时钟域进行分组。每个时钟域内的逻辑都是同步设计。

识别false path

通常,只有同步器模块的输入需要"set\_false\_path"命令。如果时钟前缀使用了前面的命名方案,然后可用通配符轻松地识别所有异步输入。

例如,sync\_u2v 模块的所有输入应以字母"u"开头的。以下 dc\_shell 命令足以设置时序分析中的相关虚假路径:

1.set_false_path-from { u* }执行最小-最大时序分析

每个时钟域的模块现在都是一个完全同步的设计。Design Compiler或 Prime Time等工具,可用于执行最小-最大时序分析,验证setup time和hold time时序是否为例。

参考资料

《Synthesis and Scripting Techniques for Designing MultiAsynchronous ClockDesigns》

本文转载自公众号:芯片数字实验室

原文链接:https://mp.weixin.qq.com/s/FhZxkrOnjL2xHGUEECZgPQ

未经作者同意,请勿转载!

推荐阅读

想了解更多内容,欢迎关注芯片数字实验室专栏,由于工具,你可以专注在更重要的事情上。