控制信号从快时钟域同步到慢时钟域

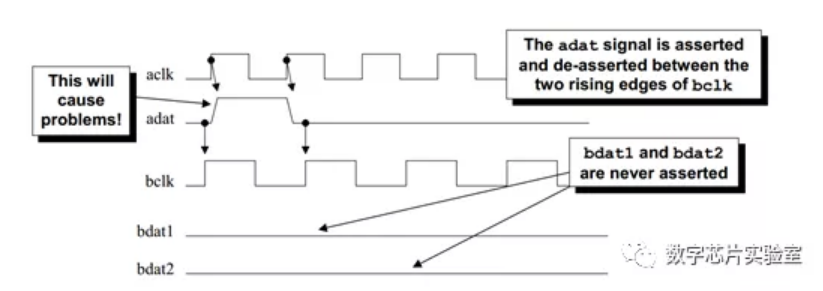

与同步器相关的一个问题是来自发送时钟域的信号可能在被慢时钟域采样之前变化。

将慢时钟域的控制信号同步到快时钟域通常不是问题,因为快时钟域将对慢时钟域的控制信号进行一次或多次采样。

在异步时钟域之间传递一个控制信号时,简单的双触发器同步器通常就足够了。

但是如果将控制信号从较快的时钟域传递到较慢的时钟域时,可能会出现问题,来自快时钟域的控制信号必须宽于较慢时钟的周期。否则如下图所示,快时钟域的控制信号无法被采样到慢时钟域。

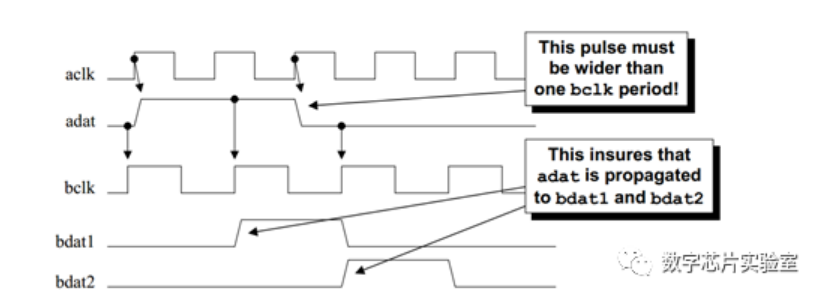

该问题的一个解决方案是扩展快时钟域的控制信号,使得控制信号至少被慢时钟域采样一次。

该问题的第二个解决方案是将快时钟域的控制信号同步到慢时钟域,然后将同步信号通过另一个同步器传回快时钟域作为acknowledge信号。虽然这种方式是一种非常安全的跨时钟域信号传输方式,但是存在相当大的延迟。

传递多个控制信号

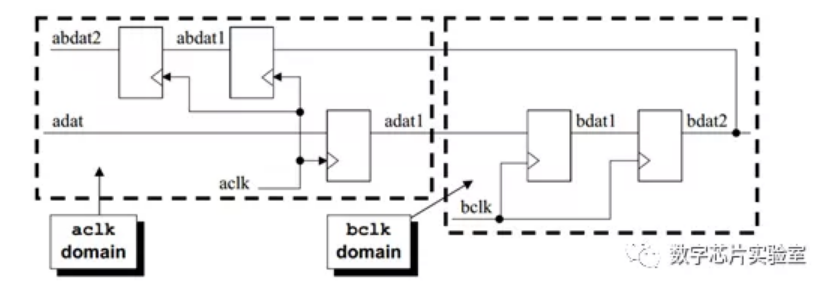

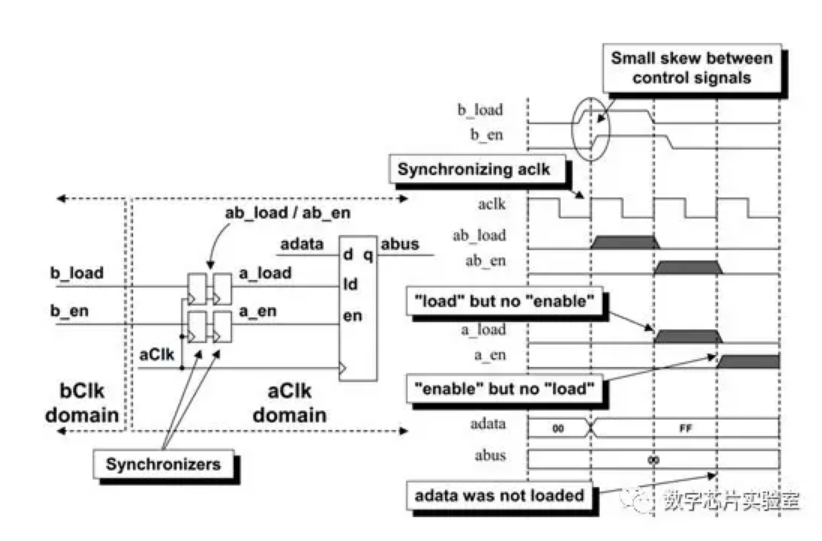

在多时钟设计中,工程师在传递多个控制信号从一个时钟域到另一个时钟域时,容易忽略了控制信号顺序的重要性。只是在所有控制信号上使用同步器是不够的。

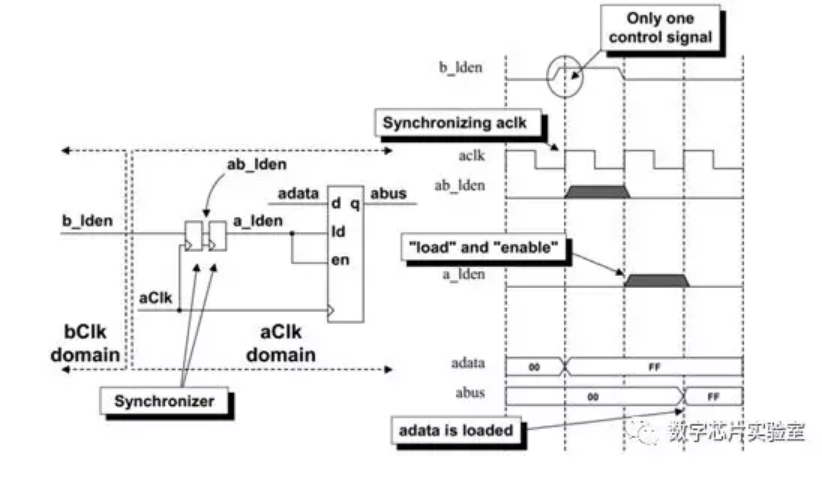

问题1 -同相位的控制信号

在上图所示的简单示例中,新时钟域中的寄存器需要load信号和enable信号以将数据值加载到寄存器中。load信号和enable信号之间的小偏差(skew)可能会导致两个信号在新时钟域内的不同时钟周期被采样同步。在上面的示例中,这将导致数据在新时钟域无法被加载。

一个简单的解决方案如上图所示,在发送时钟域中组合load信号和enable信号为一个控制信号。

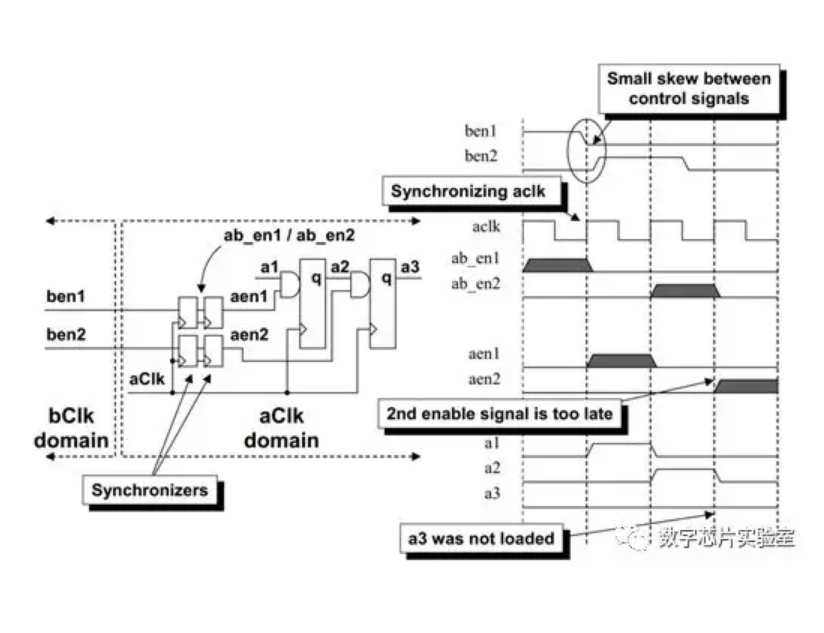

问题2 - 两个相位的控制信号

上图显示了两个使能信号ben1和ben2,用于流水线顺序传递数据信号。一个可能存在的问题是在第一个时钟域中,ben1控制信号可能会在ben2控制信号被置位之前无效,并且第二个时钟域可能会在ben1和ben2控制信号中间的微小的时间间隔采样,导致第二时钟域中的aen1和aen2中间形成一个周期的间隙。这将导致a3输出信号延后一个时钟周期。

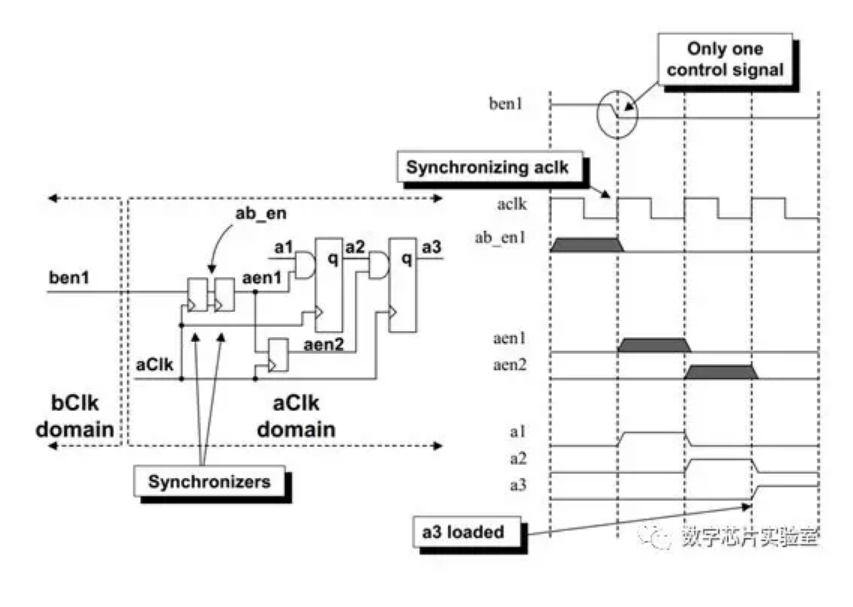

如下图所示,该问题的解决方案是将ben1和ben2组合成一个控制信号,并在新时钟域中产生第二个周期的顺序控制信号。

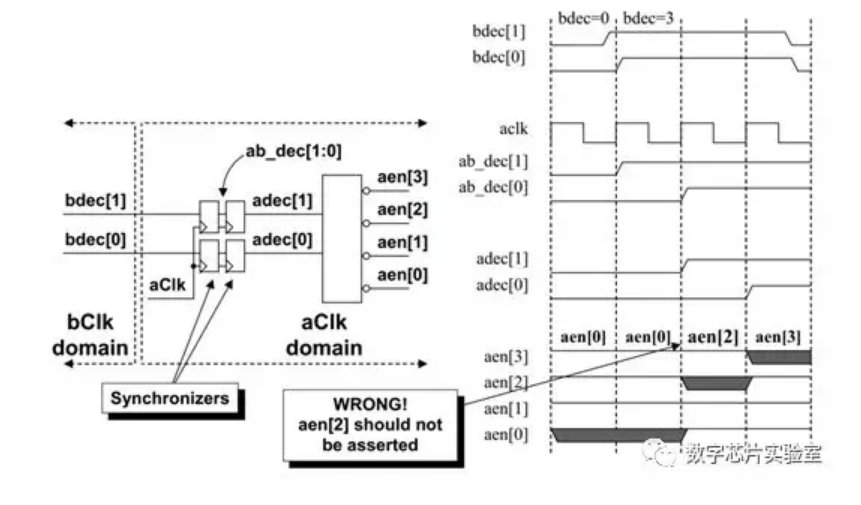

问题3 - 两个被编码的控制信号

上图中显示了在时钟域之间传递两个被编码的控制信号。如果两个控制信号在采样时存在skew,则新时钟域采样到的数据可能发生错误。

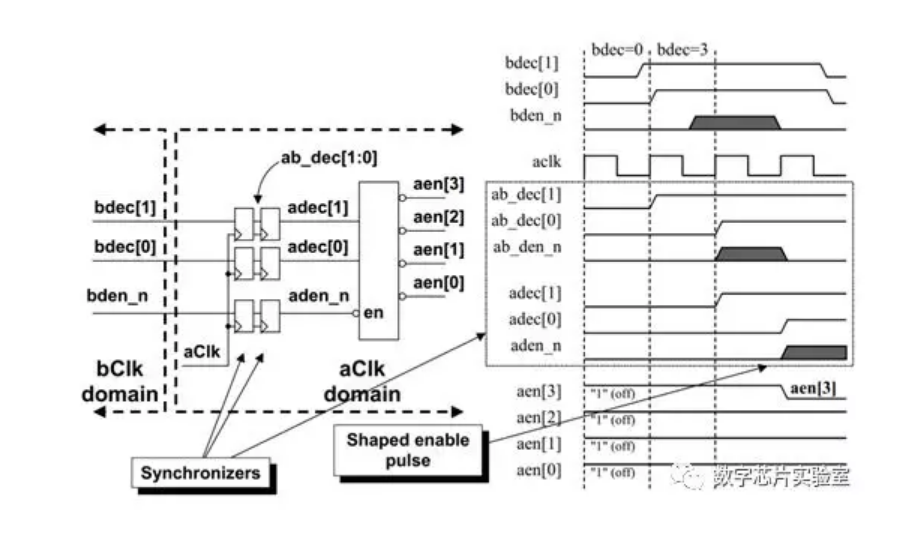

如上图所示,该问题的一个解决方案是使用一个使能信号以充当新时钟域“ready flag”。发送时钟域必须在控制信号输入之后的时钟周期生成使能信号。发送时钟域还必须在控制信号输入之前一个时钟周期移除使能信号。使能信号的宽度必须比接收时钟域的周期时间长。

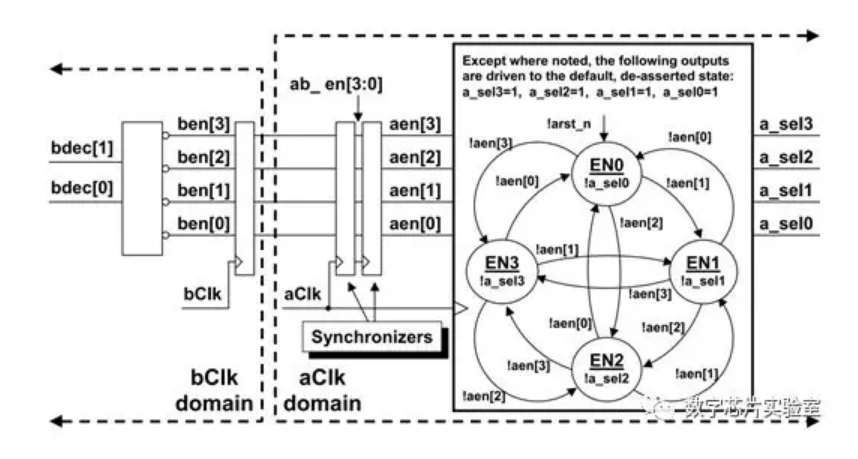

如上图所示,该问题的第二种解决方案是在发送时钟域解码,通过同步器来同步发送时钟域的输出到新的时钟域。在新的时钟域内,使用状态机确定何时被同步的输入有效。

如果没有解码输出,则意味着两个输出位同时变化。

如果有两个解码输出信号,则状态机将会改变。

发送时钟域需要保证解码输出持续时间比接收时钟域的周期时间宽。

任何时候有多个控制信号跨越时钟边界,都必须确保控制信号的顺序是正确的,从而不会导致设计的功能故障。

参考资料

《Synthesis and Scripting Techniques for Designing MultiAsynchronous ClockDesigns》

本文转载自公众号:芯片数字实验室

原文链接:https://mp.weixin.qq.com/s/B1VsyPXQatqMAlOXsUzdSg

https://mp.weixin.qq.com/s/Tr0R2VQ8iPCtta8jpP3i3w

未经作者同意,请勿转载!

推荐阅读

想了解更多内容,欢迎关注芯片数字实验室专栏,由于工具,你可以专注在更重要的事情上。