数字IC设计可谓环环相扣,很多环节都存在迭代发生的可能。

在最初芯片设计之前主要考虑PPA,即power、performance和area,但是实际项目中还存在仿真、测试及后端实现的问题。

本文主要介绍RTL设计引入的后端实现过程中的布线(routing)问题。

后端物理实现需要完成芯片中布局布线(place&routing)的工作。在物理实现过程中routing之前的floorplan阶段、placement阶段和CTS阶段都对routing效果有很大的影响,也有很多针对congestion的优化技术。

但是,实际项目中依然存在走线无法绕通的问题,可能是因为芯片对利用率要求可能比较苛刻,也可能是因为在RTL级别建模电路时造成了难绕线问题。

芯片物理实现中的macro走线、电源布线等占据走线资源,时序和串扰也会给走线引入更多的问题,我们应该尽量减少由RTL级别电路建模引入的无法走线问题。

下面举两个在RTL级别优化电路走线问题的示例:

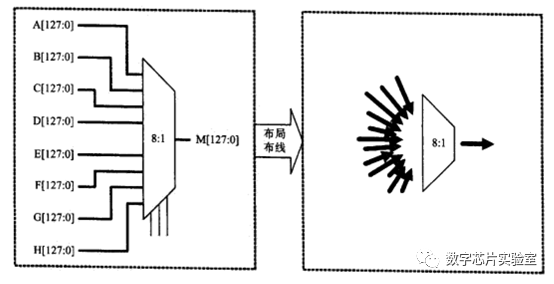

1、大扇入

reg [2:0] SEL ;

reg [127:0] A,B,C,D,E,F,G,H, SEL;

always@(*) begin

case(SEL)

2’b000:M <= A;

2’b001:M <= B;

2’b010:M <= C;

2’b011:M <= D;

2’b100:M <= E;

2’b101:M <= F;

2’b110:M <= G;

2’b111:M <= H;

endcase

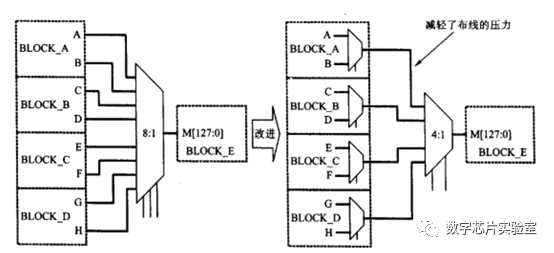

end在上面的电路中一个MUX电路具有非常大的扇入(8X128=1024)。可以通过级联MUX优化走线问题:

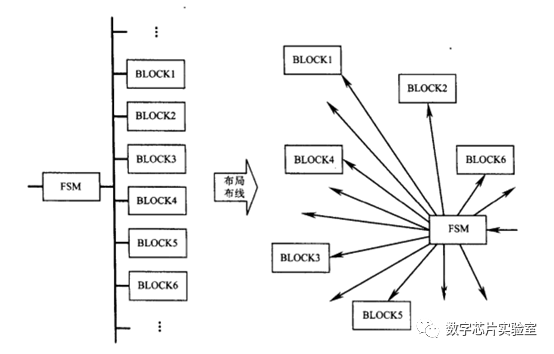

2、大扇出

设计中还存在一种被广泛使用的信号,这种信号具有非常大的扇出,例如时钟、复位和使能等。

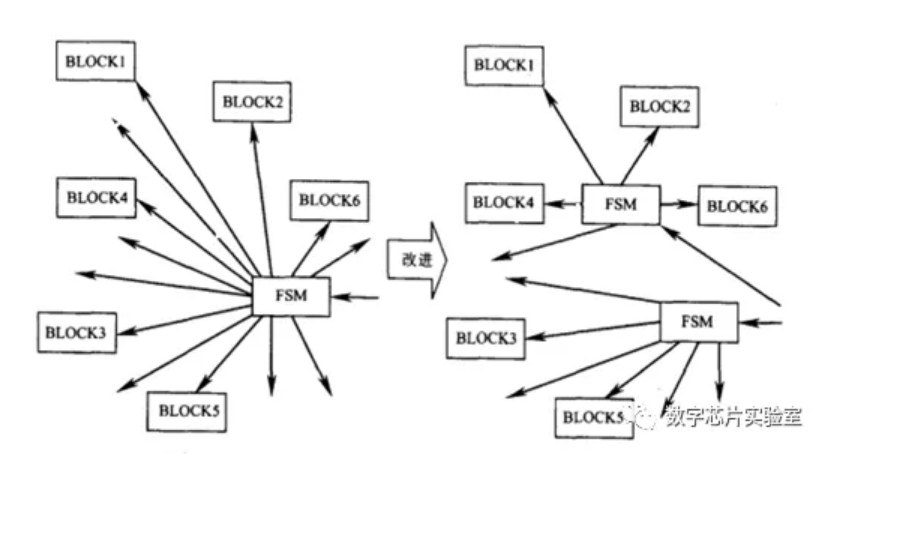

为了解决这个问题,可以复制信号源。这也体现了利于走线和硬件开销之间的折中。

上面这个有限状态机输出信号被多个模块使用,可以复制这个状态机,优化走线问题。

参考书籍:

数字IC设计——方法、技巧与实践

本文转载自公众号:芯片数字实验室

原文链接:https://mp.weixin.qq.com/s/obwFaM65\_yn7yoNZeJT48g

未经作者同意,请勿转载!

推荐阅读

想了解更多内容,欢迎关注芯片数字实验室专栏,由于工具,你可以专注在更重要的事情上。