本节重点介绍仲裁器在设计中的作用,包括时序和逻辑功能。

然后描述用来验证系统中仲裁器模块的SystemVerilog Testbench。

$VCS_HOME/doc/examples/testbench/sv/tutorial/arb01 仲裁器时序图

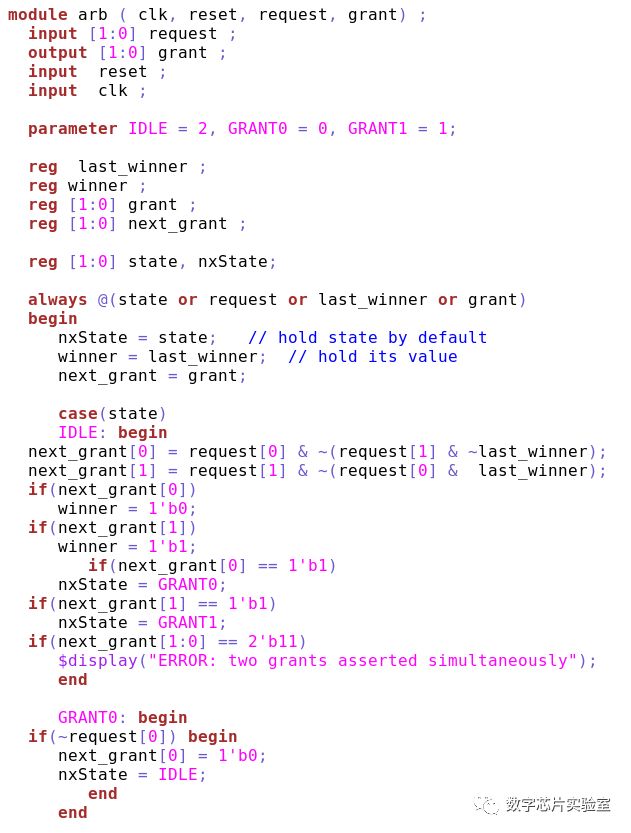

仲裁器实现了两个CPU之间的仲裁算法(round-robin)。每个CPU都可以驱动请求输入信号(request[0] 或者request[1])。 仲裁器对请求进行排队并确定哪个CPU的请求将获得对系统总线的访问权限。 仲裁者通过一个输出信号(grant[0]或者grant[1])进行仲裁。 CPU完成操作后会取消其request信号,并在随后的时钟周期,仲裁器解除其grant信号。 在所有grant信号被解除的情况下,仲裁器可以继续仲裁下一个请求

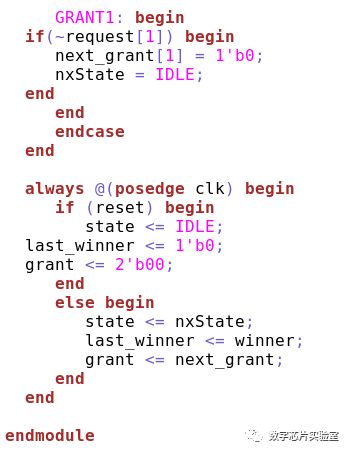

02 仲裁器RTL代码

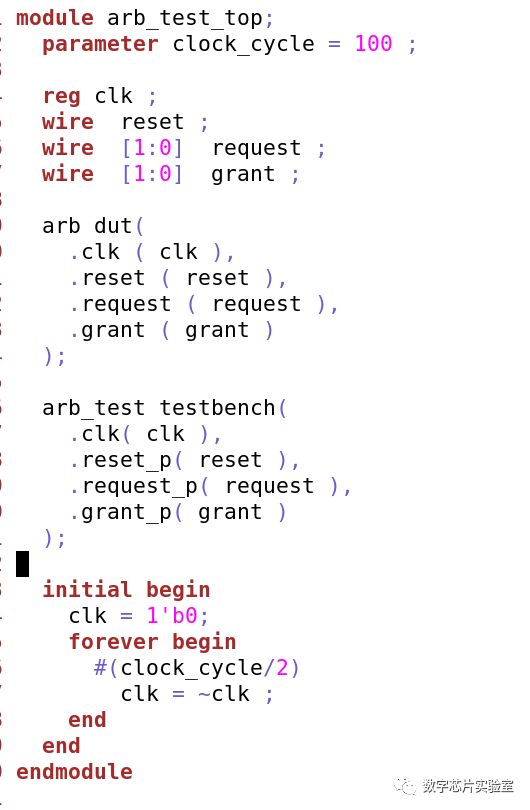

•testbench 顶层如下:

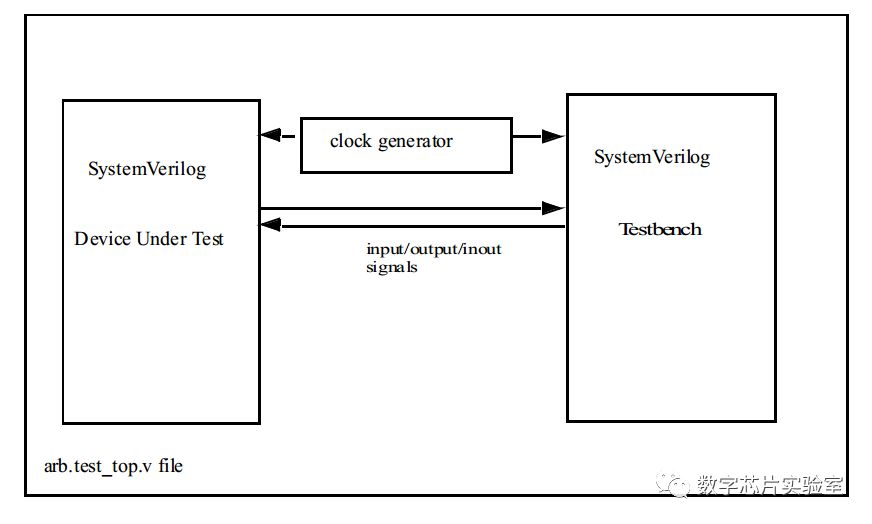

Test\_top顶层实例化DUT和SystemVerilog测试平台,并生成DUT和测试平台共同的时钟。示意图如下:

03测试平台文件

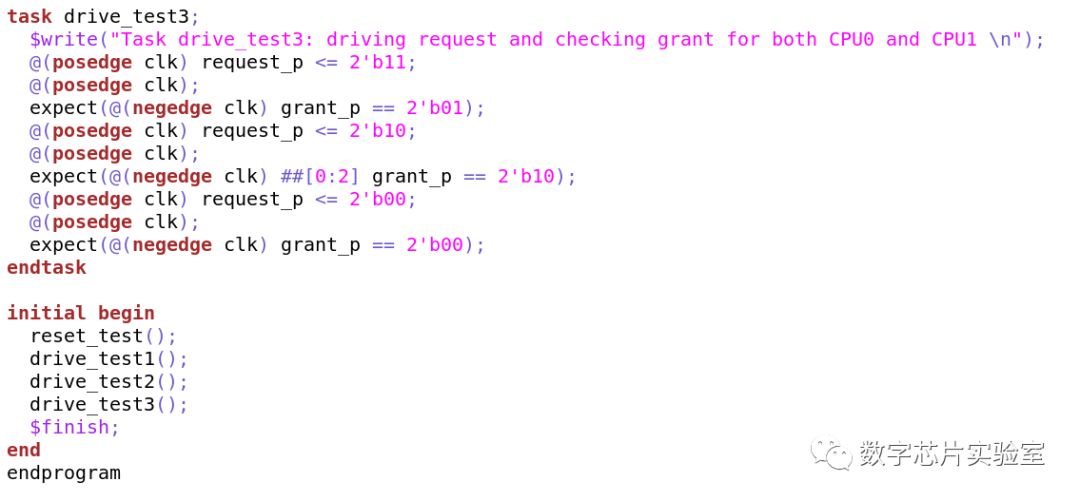

测试平台文件如下:

首先,验证仲裁器的reset。 然后,验证仲裁器是否能够处理简单的请求,并置位其中一个的CPU的grant信号。 最后,检查仲裁器是否正确处理了请求序列。

所有的信号操作都发生在指定的时钟边沿

expect运算符用于检查预期行为。

例如:

e1:expect(@(posedge clk##[1:3] xyz);

将在1到3个时钟周期内检查xyz是否被置位。

如果信号值与指定值相同,则进行仿真继续。 如果存在mismatch,则在用户定义的错误消息中将被打印。

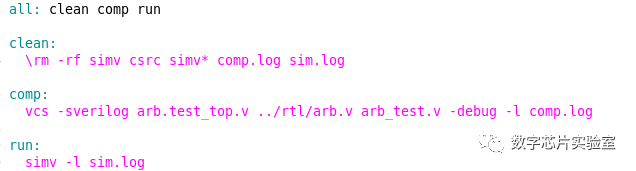

04 编译和运行脚本

•编译和运行脚本如下:

change simv -> ./simv

我们 make all 就可以执行所有仿真case

本文转载自公众号:芯片数字实验室

原文链接:https://mp.weixin.qq.com/s/hVE1XmROgStMrcC3TbcZNw

未经作者同意,请勿转载!

推荐阅读

想了解更多内容,欢迎关注芯片数字实验室专栏,由于工具,你可以专注在更重要的事情上。