STA用于分析设计中的所有时序路径是否都时序收敛,其不需要输入激励。对于数字芯片设计工程师,必须要了解不同的时序路径和相关的STA概念。

时序分析适用于任何ASIC设计的阶段,可在各个设计阶段执行。如果设计违反setup time或者hold time,则设计进入亚稳态。

因此,必须通过时序分析工具Synopsys PT找出并解决设计中的时序违例问题。

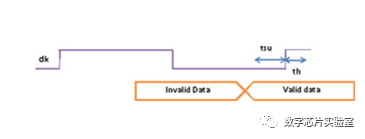

Setup Time& Hold Time

触发器输入信号'd'在有效时钟边沿到达之前所需的保持稳定值的最短时间,称为setup time(建立时间)。

触发器输入信号'd'在时钟的有效边沿到达之后应至少保持的时间称为hold time(保持时间)。

Frequency Calculations

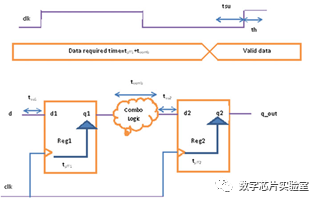

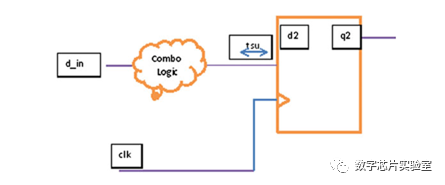

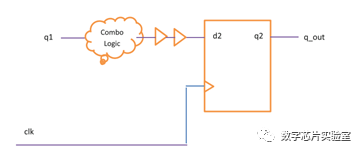

如下图所示,触发器(reg1)的时序参数为tpff1和tsu1,触发器(reg2)的时序参数为tpff2和tsu2。该数据路径中的组合逻辑延迟为tcomb。这些时序参数可以用于确定该设计的最大工作频率。

arrival time为tpff1 + tcomb,required time为Tclk-tsu2,其中Tclk是时钟周期,tsu2是第二个触发器的setup time。

因此,计算最大频率需满足:

tpff1 + tcomb = Tclk-tsu2

Tclk = tpff1 + tcomb +tsu2

Fmax = 1/( tpff1 + tcomb +tsu2)Skew in Design

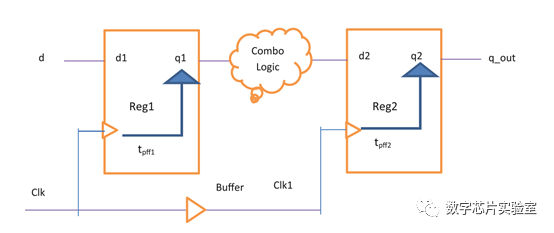

在上图中,触发1是launchflip-flop,触发2是capture flip-flop。

在上面的例子中,时钟路径上增加了buffer延迟。此时,最大频率为:

tpff1 + tcomb = Tclk-tsu2+tbuf

Tclk = tpff1 + tcomb +tsu2- tbuf

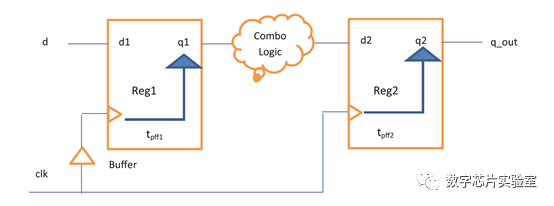

Fmax = 1/( tpff1 + tcomb +tsu2- tbuf)在上面的例子中,数据路径上增加了缓冲器延迟。此时,最大频率为:

tpff1 + tcomb +tbuf= Tclk-tsu2

Tclk = tpff1 + tcomb +tsu2+ tbuf

Fmax = 1/( tpff1 + tcomb +tsu2+tbuf)由此可以看出,数据路径和时钟路径上的skew会从相反的方向影响设计的性能。

Timing Paths in Design

STA通过检查设计中所有可能的时序路径来确定ASIC设计是否时序违例,并且只检查具有最差延迟的路径,而不关心设计的逻辑功能。

时序路径从寄存器时钟端口或input端口开始,称为Start point。

时序路径终止于寄存器数据端口或output端口,称为Endpoint。

对于任何RTL设计,可以有四类时序路径:

• Input-to-register path

• Output-to-register path

• Register-to-register path

• Input-to-output pathTiming Goals for the Design

在实际场景中,使用时钟和IO时序来定义设计的时序目标。因为定义了时钟之后,就意味着定义了Register-to-register path

Min-Max Analysis for ASIC Design

setup time Min-Max分析是基于最快的时钟到达和最慢的数据到达。

hold time Min-Max分析是基于最快的数据到达和最慢的时钟到达。

要fix setup time违例,数据应该快速到达,launch时钟应快速到达,capture时钟应缓慢到达。

要fix hold time违例,数据应该缓慢到达,launch时钟应缓慢到达,capture时钟应快速到达。

下面举两个分别优化setup time和hold time的示例:

Setup Violation Fix

现在流行的编码技术是优先编码(priority encoding)和多路复用编码(multiplexed encoding)。

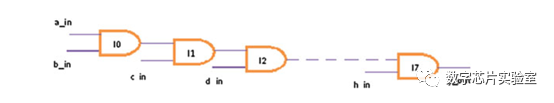

assign y_out=a_in && b_in&& c_in && d_in && e_in && f_in&& g_in&& h_in;上面的语句生成优先级逻辑,其中h\_in具有最高优先级。

在优先级编码方法中,总延迟为7tpd。为了提高设计性能,必须减少组合逻辑的传播延迟。

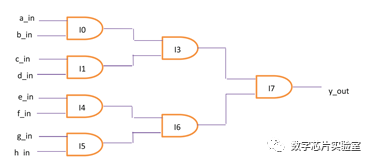

下图是多路复用编码,总传播延迟仅为3tpd。(并行化的体现)

Hold Violation Fix

对于上图中的设计,如果组合逻辑延迟较小可能发生保持时间违例。

要修复设计的保持时间违例,可以在数据路径上插buffer,但需要注意不能够导致建立时间违例。

Timing Exceptions in the Design

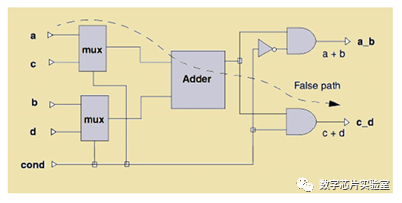

1、Asynchronous and False Paths

如果设计中一个信号或端口的变化不影响输出,需要设置成false path。

异步路径也被视为false path,不需要进行时序检查。

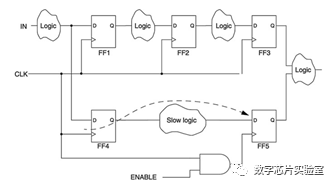

2、Multicycle Paths

如果设计中的时序路径延迟允许超过一个时钟周期,则路径为被视为多周期路径。

set_multicycle_path –setup 2 –from [get_cells FF4 ] –to [ get_cells FF5 ]

set_multicycle_path –hold 1 –from [ get_cells FF4 ] –to [ get_cells FF5 ]

本文转载自公众号:芯片数字实验室

原文链接:https://mp.weixin.qq.com/s/VEry5Zue1FrmJU-XMW\_VsQ

未经作者同意,请勿转载!

推荐阅读

想了解更多内容,欢迎关注芯片数字实验室专栏,由于工具,你可以专注在更重要的事情上。