来源:知乎

ID :FreeZynq

作者:王yifei

最近逻辑组任务较多,人力不足,因此招了一些新员工。最近一段时间,也面试了很多人,各个行业和公司的都有,形形色色的人面试多了,也有一些感触,另外,年近而立,也需要总结一下。在此记录下来,与君共勉。

关于行业

面试了几个月,收到了几百份简历,面试的人也有好几十。回想一下,投简历的大概有以下几类:

完全不懂逻辑的,比如,有网吧的网管,也投简历做逻辑验证工程师。应届生做视频、安防相关行业的、做芯片的、通信行业的小公司、通信行业的大公司,甚至超声行业。其中,第1,2两类,肯定是完全不考虑的。

第3类,做视频和安防的,面试过几个,一般这种公司,逻辑的人员规模都比较小,经常有人做个2-3年,就做到逻辑组长了,但是他们一般水平都不高,基本的时序约束都不做,仿真也不做,一般逻辑规模都比较小,直接上板用signaltap调试,对整个逻辑研发的流程也不熟悉。

第4类,asic工程师,这类工程师,一般代码水平和仿真水平都还可以,整个设计流程也比较严谨,但是纯粹的asic工程师,如果没做过fpga,并不适合我们公司,对fpga内部器件不了解,对时序约束的经验也不多,而且asic的工期很长,几年下来,做不了几个项目。一般纯粹做asic的,都难以通过第一面,有一部分做过asic的fpga验证的,或者中途转行,既做过asic,也做过fpga的,水平还可以,其中有几个进入了二面。总体而言,asic工程师并不太适合转作fpga。

第5类,通信行业的小公司,也面试过一些。一般通信行业的小公司,里面都有一些人,之前是在华为、中兴做过的,整个公司的逻辑水平,还比较好,因此,这一类的求职者,水平也还可以,不过主要是看个人,有一些知识较全面,也有一些懂得并不多。

第6类,这一类,一般就是华为、中兴,最近这两家公司离职的人也较多,面试的有一半以上,都有华为、中兴的工作经历。这一类,一般工作年限3年以上的,水平都比较好,知识面比较全,整个流程也比较清楚,而且流程和文档做的比我们公司要好。但是缺点就是很多人做的比较窄,基本上只做一个点,虽然知识面还好,基本都懂一些,但是很多方向都没有自己动手,有一些部门,写代码一拨人,编译工程一拨人,仿真验证一拨人,查bug又一拨人,导致对整个全局把握较少,另外,这些人原本待遇就比较高,尤其是华为,很多人比我工资都高好多。

第7类,超声行业,这一类是比较对口的,但是人很少,只面过几个,对超声有一些了解,但是逻辑水平确实比M公司要差一些。

关于公司规模

好多人在一开始找工作的时候,往往面临一个选择,是去一个大公司,还是去一个小公司。大公司比较正规,可以学到很多知识,小公司机会比较多,说不定过几年就成领导了。

以上两种说法都有道理,但是都不全面。

大公司比较正规,流程等也比较正式、全面,技术积累也比较好,确实可以学到很多,而且都是正规套路,比如华为,有非常正式的流程,从方案到设计文档,每个时间段都有严格规定,等到写代码的时候,基本已经成竹在胸了。比如中兴,新人做一个设计,基本上都有非常全面的文档来告诉你,怎么做,以前出过哪些问题,基本上一个智商正常的人都可以顺利完成。

但是大公司也有一些缺点。首先,分工太细,不仅仅是设计上,也在流程上。比如之前面的一个人,做了5年,一直在做接口,而且是同一个接口,这个地方可能已经做的很好了,甚至可以说水平在国内都是比较高的了,但是知识面太窄,其他的不了解。还有一些人,只做代码,连工程都不需要编译,这样,就对代码的器件实现了解不多,实际工程经验也很少。之前面试过一个中兴的,主做信号处理,做了3年,基本上完全不知道fpga是啥,只懂信号处理的verilog代码实现,连逻辑基本单元由查找表和寄存器组成都不清楚。

另外,大公司一般项目进度都比较严谨,在多年的经验积累中,项目进度一般都定的比较准确,这就意味着你必须每天都在做项目,跟进度,很少能留出时间来自己学习,更不用说拿几个星期出来,改改逻辑架构,做些自己有兴趣的事。不利于个人的提升。

对小公司而言,要自由的多,能够接触到的也要多一些。我面试的一些小公司的人,一般都能从头到尾都接触到,包括方案,代码,仿真,调试,debug。也有一些2-3年就成为逻辑组长的。

不过,小公司的缺点也是很明显的。除非小公司有技术很牛的人,否则,一般都难以有很完善的流程,技术上也很难做到比较精深。很多小公司的,连仿真都不做的,而且只做时钟频率约束,管脚的输出输出时序约束都完全不做。所以,小公司出来的,一般都不那么正规,而且水平也很难做高。

面试过许多人后,再回想一下,应该说,M公司还是提供了一个很好的平台的。

虽然M公司有种种缺点,比如,流程很简陋,对文档的要求比较低,基本上文档就自己写写,然后评审一下,文档写的不正规,而且过一段时间,代码跟文档都对不上。整个逻辑的配置管理也比较乱,很多项目都说不清楚逻辑是复用了哪个的,又改了些啥。

对代码的要求也很低,或者说,有要求,但是没执行。每个人都按照自己的习惯来,以至于我不用看说明,随便从代码中找出一段看看,就知道这段代码出自谁手。

积累和培训做的不好。基本上,我在M公司被培训到的逻辑知识比较少,有过一些培训,但是效果并不好,大部分都是在项目实践当中学到的。基本就没有一个培训体系,全靠自己悟,自己问。

但是M公司还是一个比较好的起点。首先,逻辑规模足够大、足够多样、足够复杂、更改足够多。规模大,就会有机会使用比较大,比较高级的芯片,而且,规模大,对人的掌控能力也有很高的要求。足够多样,知识面就会比较广,当前的逻辑有各种接口,包括transceiver,pcie,spi,uart,i2c,ddr,lvds,ssram,ccir656,rgb等等各种接口。以及相应的各种逻辑。既包括信号处理相关,也包括各种复杂控制,还有视频相关等。足够复杂,对于提高逻辑水平有很大帮助,当前有很多逻辑设计都是比较复杂的,比如数据缓存,pcie上传,xx控制等。更改足够多,就意味着有很多新东西可以做,而且需求的多样性更改,才能催生一系列的设计思想。软件就是因为要处理各种复杂、多变的需求,才衍生出了各种思想,如面向对象、设计模式等。

另外,每个人负责的逻辑设计,流程上可以走完整。包括老项目的维护,在研项目的需求、方案、设计、仿真、调试、debug,以及新项目的预研,都可以全程参与,对逻辑的整个流程会有比较深刻的认识。而且,不仅仅是写代码,包括设计的编译,调试,debug等工作,可以对负责的逻辑设计,有更加深入的认识,对逻辑的可阅读性、可复用性、可调试行等原则有所感触。

另外,得益于逻辑组一定的流动性,可以将逻辑的各个模块都做一遍,而不是只能一年一年的只能做同一个设计。我来公司几年,做过的设计包括 视频、电源管理、按键板、XX、XX管理、newC、pcie上传、XX、数据缓存、信号处理、XX控制,基本上,超声相关的逻辑,除了xx,其它的,或深或浅的都做过,即使xx,我也曾自己花了2个星期的时间企图重构过,对其设计也有一定的理解。这在大公司,是不可能的。

另外,由于我们公司的超声还没到世界领先水平,以及系统组同事无穷无尽的新想法,每个逻辑设计的方案,都在不同的项目之中变来变去,而且不同于通信领域的固定处理方式,我们公司的逻辑基本上是没有参考的,完全由做逻辑的人来确定,有非常大的发挥空间。

另外,由于我们公司还比较低级的项目管理水平,项目进度的安排并不怎么合理,有些项目中,是有时间可以做一些事情的,当然,最近一两年几乎没有了。但是前几年,我曾经有几次,可以抽出几个星期的时间,并行的做一些我感兴趣的事情,比如逻辑重构。

综上所述,在职场的起点,选择一家好的公司,是非常重要的。

一个逻辑工程师的成长之路

面试了很多人,有些水平高,有些水平低,有一些公司有严格的职级,比如华为,完全可以根据其职级来得知其逻辑水平,而且华为的业务职级和技术职级还是分开的。我们公司也有职级,但是,不同的公司之间,或者说,逻辑工程师,没有一个比较普遍、统一的标准来衡量其水平。

我一直比较困惑于这个问题,原因来自于从小受到的教育和长大后经常看的小说。小时候的学习成绩,是非常容易识别和量化的,分高分低,一比就知。成年以后,看过各种小说,武力高低,也是有非常明确的量化的,一个人完全可以非常清楚的知道,自己的级别。比如xxxx,用魂力来表征水平,从1-100,每10个级别为一个大的等级,虽然这不能代表真正实力,但是至少让读者可以看到主角的逐步成长。不过,这也只是小说,现实生活中,是没有这个东西的。

鉴于这些困惑,在本章,按照我自己的简单的经历和粗浅的认识,对逻辑工程师的水平做一下初步的划分。

第一阶段:能用

阶段特点:这个阶段,基本上处于刚刚接触到verilog代码一段时间,知道大概的语法,能够把一个需求用代码实现出来,并且能够调试出来。总体而言,处于一个能用的位置,可以实现,但是并不清楚代码与实际器件实现的关系,对逻辑的硬件思维基本没有。

阶段评价:此时,尚且不算一个逻辑工程师,因为只会写代码,没有逻辑思维

提高途径:如果有审美,有需求,自己有内部推动力,将开始进入到第二阶段(我有见过中兴的3年的算法工程师,做了3年只懂算法实现,完全没有逻辑硬件思维,因此,时间长短跟水平并没有直接关系)

第二阶段:可用

阶段特点:这个阶段,开始关注代码风格,开始把自己的代码写的风格统一,并且开始关注代码的硬件实现,突出标志就是开始关注rtl视图,可能还不怎么关注器件视图。但是基本知道器件的大概结构,知道fpga里面有le,ram,dsp,全局等等。比较能明确的区分可综合语句与仿真语句的区别。

阶段评价:这个阶段,基本可以称为是一个逻辑工程师了。能够完成设计实现,仿真,调试,能够做出逻辑设计说明。

提高途径:此时,一般开始负责一个模块,如果该模块在其他项目上复用,并且略有更改,有的人会直接修改,而有些人开始有更多的考虑,由此进入第三阶段

第三阶段:好用

阶段特点:这个阶段,由于上一个阶段已经可以实现设计,在这个阶段,开始考虑设计的复用,开始考虑模块的划分,注重模块接口,平台化等等。

并且,此时对模块内部的代码书写有了更加深刻的认识,模块内部的写法开始更加统一,基本上,模块内部的代码可以直接生成rtl视图。

并且,此时开始关注器件结构,了解fpga的内部架构,时钟网络,route,对时序约束有了基本的了解。

阶段评价:这个阶段,可以认为是一个基本成熟的逻辑工程师了,逻辑所需要掌握的知识方向,基本都有所了解,而且,不仅能够完成设计,还能在设计之前做出方案,而且做出的设计,模块的划分比较合理了。

提高途径:此时,一般会开始接手一些比较大的前人的设计,有的人会尽量复用,有些人会有更多的考虑,由此进入第四阶段。

第四阶段:易用

阶段特点:这个阶段,会接手一些比较大的设计,开始有架构的考虑,对于模块的划分,模块接口,模块职责,整体方案的实现,开始有更多的考虑,此时,可以做出比较好的,合理的方案,而且对逻辑的各个方向的知识,都有了比较全面而深入的了解,比如仿真,器件结构,时序约束,模块划分等等。

阶段评价:这个阶段,可以认为是一个比较优秀的逻辑工程师了。能够在项目之初给出比较好的逻辑方案,并且能够快速而高效的完成设计,仿真和验证。对应可能发生的时序,等等问题,也有比较好的考虑。

提高途径:此时,如果有机会可以带领一个团队,会进入一个不同的领域,能够接触到更多的东西。

第五阶段:逻辑架构师

阶段特点:这个阶段,会负责一个团队,或者一个项目的逻辑设计。开始对整体的逻辑架构有所考虑,并且开始准确的划分逻辑架构,并分配不同的工作任务,由于需要团队协作,因此要求对逻辑方案,逻辑进度,逻辑技术,有非常深刻的认识。

阶段评价:可以给团队制定逻辑代码规范,逻辑设计流程,

可以轻松的完成逻辑整体方案的设计,并且准确识别风险点

可以准确的划分逻辑架构,模块接口,功能划分,工作职责,

可以准确的预估项目的风险,进度

可以准确的做出逻辑的整体方案,仿真方案,调试方案,对于整体的业务流有全面而深刻的认识

对于逻辑的各个知识方向有非常深刻的认识,

熟知各个厂家的各种逻辑器件的内部结构,基本逻辑单元结构,以及由此带来的代码风格的相应的改变

熟知时序约束,并且能够采取各种手段,解决各种时序问题

对于逻辑的布局,数据流走向有深刻的认识,

对仿真有深刻的认识,熟知仿真器原理,并且开始搭建可重用,复用性好合效率高的仿真平台,或者使用高级仿真

此时,基本有10万代码量。

提高途径:由于本人仍在此阶段挣扎,因此,尚不知如何提升。也许可以关注一下板卡,向硬件系统方向发展,或者补充验证方法学,向数字部门方向发展,或者整合逻辑、软件、系统,向系统方向发展。在此阶段,逻辑本身相关的技术,也许已经到达一个瓶颈了。

由以上各个阶段的发展可知,一个好的逻辑工程师,一是要有好的环境,可以学到东西,二是要有机遇,可以遇到不同的情景。但是最重要的还是,对自己有要求,有追求,自己内部有不断的推动力,可以使自己不断的学习进步

一个逻辑工程师的成长之路-实例篇

第一阶段(2008-2009)

第一阶段:能用

在我刚进公司时,勉强算是第一阶段,严格来讲,我虽然学过数字电路设计,但是当时用的教材很老,并没有讲述跟fpga相关。后来在实验室,买了一块开发板,才慢慢开始学习fpga。

刚进公司的时候,完全没有硬件时钟的概念,没有时序约束的概念,刚刚处于能用verilog代码完成需求的阶段。

不过机会很好,当时就赶上了M1项目,负责了电源管理和视频。比较适合新人的两个设计。

比较顺利的完成了代码和仿真,调试的时候,也还比较顺利,开关机,屏幕显示,都按时完成了。

不过,此时并不太明确verilog代码与fpga器件实现之间的关系,写代码时,不是考虑fpga能否实现,而是考虑是否符合verilog代码的语法。

此时大概是2008年下半年和2009年初。

这个阶段,写的代码其实是比较差的,不管从代码风格,还是从代码设计,模块划分等。不过鉴于本人良好的重构习惯和对代码风格的极致追求,这段时期写的代码,基本上都看不到了。

后来做完M1之后,在做M2(2010)之前,大概有1年的时间,这段时间内,项目进度没有那么紧,有一些时间可以学习,开始进入第二阶段。

第二阶段(2009)

第二阶段:可用

2009年这段时间,做了xx的一块板子,M3的键盘板,svideo,万能按键板等3个项目。

时间比较充足,加之本人的习惯,喜欢对一个事情追根究底,希望可以弄明白,想清楚。

这段时间,学习了很多关于综合,关于器件结构等的知识,在网上也搜了很多资料,自己也研究了altera的cyclone3的器件。还曾经想写一个ppt,把逻辑中常用的代码,对应的综合结构和布局布线结构都搞清楚,后来做的时候才发现,跟理论值不一致,才作罢。这个阶段也看了很多关于时序约束的内容,不过此时对时序约束的理解还不深入,而且随着做的项目的增加,debug经验的丰富,水平开始逐步提高,能算得上是一个合格的逻辑工程师了。

2010年,开始做M2项目和M4项目。涉及到了xx逻辑的重构和svideo视频的重构,开始进入第三阶段。

第三阶段(2010-2011)

第三阶段:好用

2010年主要做了两个设计,一个是M2的发射逻辑,一个是M4的视频逻辑。

发射逻辑是一个比较典型的例子,当时对逻辑设计有了一定的认识,也有了一定的想法。M2的发射逻辑是基于M1的发射逻辑的,但是被我完全重构了,此时开始考虑逻辑的模块划分,接口时序。

而且由于发射逻辑扇出较多,开始考虑代码的布局布线与时序收敛。

同时,对代码的书写开始有要求,这个阶段的代码,应该说开始有了自己的风格,而且写的比较好。这部分的代码,后来未再修改,还可以在svn上看到。

M2的发射逻辑是做的比较顺利的,在板卡回来之前1个月,基本上设计和仿真就全部完成了,也有一些时间来学习,后来调试也非常顺利,发射几乎没出bug。

下半年做视频逻辑。

由于在M1做了视频逻辑,M2的视频由其他人负责,在做M4的视频逻辑时,水平有了一定的提高,而且时间也比较充足,兴趣也比较强烈。在M4的视频逻辑上,做了很多重构的工作。

其中,lpc总线模块,就重构过2次,对于状态机的写法进行了深入研究,svn上可以看到M4的lpc代码和M1的代码是不一样的。

svideo部分的代码,起初是09年xx写的,后来我接手后,曾经重构过一次,把代码全部整理了一遍,并彻底搞懂。由于M4的视频需求更改,由一路svideo变成两路:svideo和dvr,所以又将这部分代码再次做了颠覆性的重构。

这个阶段,可以说对逻辑的架构,已经有了初步的认识和一定的经验。而且视频大多跟外设打交道,此时对时序约束已经比较清楚了,有些时序上的问题,已经可以比较容易的解决了。

此时写的代码,不管是代码风格,模块划分,接口,逻辑架构,都已经比较好了。

不过,此时多是在折腾自己的代码,比较熟悉的代码。(svideo算是一个中小的,别人写的代码)。真正考验逻辑架构能力的,是对别人留下的一个中等的、复杂的、功能正常的逻辑做重构,变成一个架构合理、简单易用的逻辑,而且整个过程还要尽量少出bug。

等待的时间不算太久,10年底到11年初,还做了一个M4的newc,完全是一个全新的逻辑,也算是初步了解了信号处理,而且全部从新的设计,也增加了架构经验。11年中,做了任意波的方案,虽然只做了方案,没做具体设计,但是此时对于逻辑方案,架构,已经有驾轻就熟的感觉了。

很快,机会就来到了。

2011年下半年,开始做M5的pcie上传逻辑。

这个设计,完全满足一个架构能力进阶的要求。

第四阶段(2011-2012)

第四阶段:易用

从2011年下半年的M5,到2012年的M6,是属于第四阶段的。

上传逻辑是一个别人留下的一个中等的、复杂的、功能正常的逻辑,对此做重构,挑战还是非常大的。之前对此完全没有了解。不过svideo的重构也为此打好了一定的基础。

这段时间是进公司以来积极性比较高的阶段,不停的在学习,几乎将整本《PCIE系统体系结构标准教材》全部翻完。而且每天都在消化,修改代码。由于这段时间白天很多杂事,经常晚上工作到半夜。

上传逻辑的重构,应该说是做的比较好的,短时间内将一个复杂的设计重构,而且设计上仅出了1个bug。后来该设计复用到后续所有的项目,M6,M7,M8,M9。

M5的联调,也仅用了2个星期,非常顺利。然后各种模式的联调,也都非常顺利的出了。

上传相关的总结,已经放在《pcie协议介绍,ip介绍,上传逻辑介绍,上传设计经验分享.ppt》

2012年.开始做M6项目。

这个项目,是将全部的超声逻辑,都放入到了一片fpga当中,所接触到的、所能修改的架构,变得更大。也是一个非常好的可以提高水平的设计。

对于其中的xx、xx、数据缓存、pcie上传都做了修改。

不过,之前的重构之路一直很顺利,终于在M6上栽了跟头。重构失败,最终又退回到老版本。

其中种种,已经放在《xx项目总结-逻辑方向.ppt》

经过两个项目的洗礼,对于逻辑设计,器件,时序,架构等等的认识,更加深入了。

此时,对于xx控制逻辑的重构,也有浓厚的兴趣。M5做完,M6开始之前,还曾花了3周看xx代码,只是当时已近年关,效率较低,年后即投入M6,xx重构未在进行下去。不过xx控制的重构后来倒是做了。

此时,应该算是一个比较优秀的逻辑工程师了。

对于器件和时序的认识,比较深刻。例如给出了《FPGA的管脚分配指南-时序相关.doc》

2012年中,成为逻辑leader,不过由于M6事物繁忙,直到大概9,10月份,才开始着手管理团队。

第五阶段(2013-)

第五阶段:逻辑架构师

之所以认为,要进入第五阶段,必须要成为逻辑相关管理人员,是因为此时需要操作的代码和设计是非常多和复杂的,所以需要一个团队来共同完成。而且,开始更多的从整体开始考虑。

这个阶段,主要主导完成了M7项目和M8项目。

开始对整体的逻辑架构有所考虑,并分配不同的工作任务。

对于整个项目的逻辑设计开始负责,完成整体方案,识别风险点,保证时间节点,并且熟悉整个业务流。

由于这2个项目换用了全新的fpga,因此再次加深了对器件和时序的认识。例如M8的管脚时序约束的风险解决。

并且开始搭建可重用,复用性好合效率高的仿真平台。

M7项目7周出图,但是基本相同的工作量和参与人员,M8只用了2周出图。对于项目整体的把握,有了提高。

此时,已经写过11万代码

目前,仍处于本阶段之中。

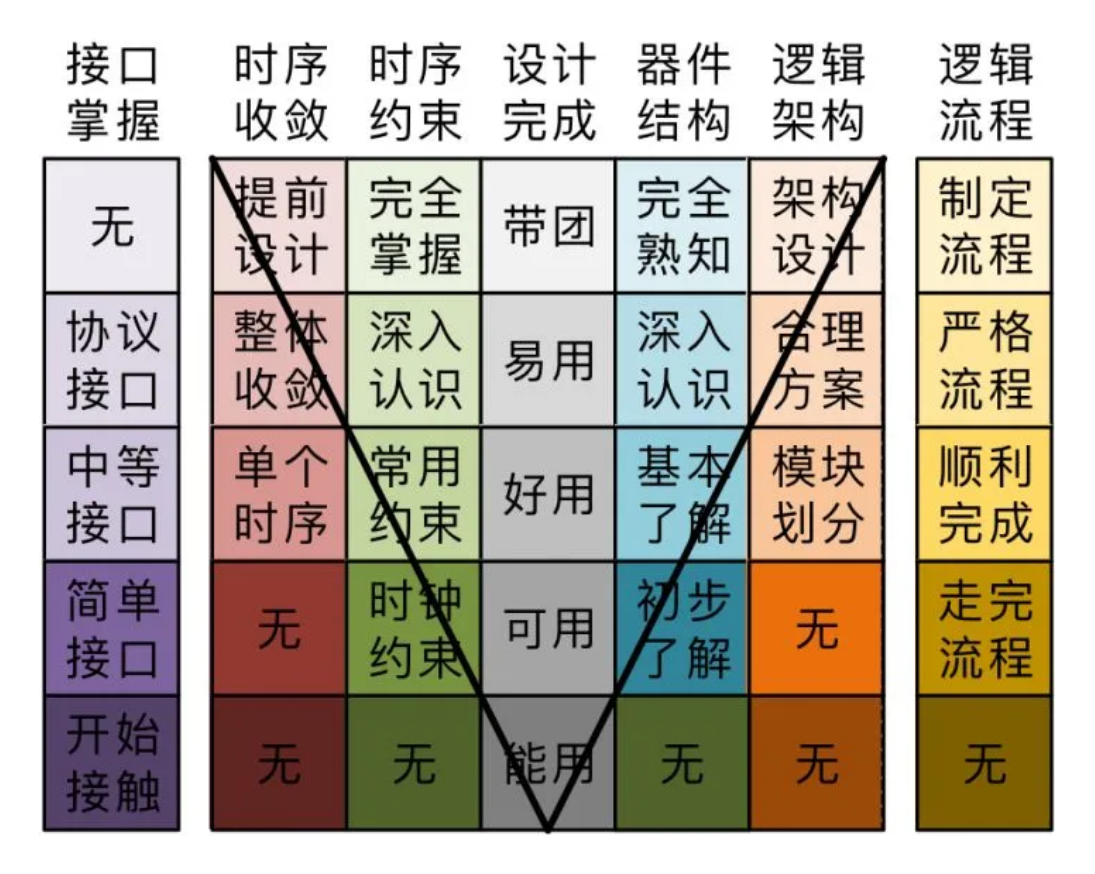

逻辑工程师水平的V模型

第3章讲述了一个逻辑工程师是如何发展的,并且给出了各个阶段的特征,但是,仍然没给出清晰的量化,本章,尝试对这个问题给出一个解决方案。

逻辑工程师应该掌握的各种能力

大概设置了5种能力,每种能力在不同的阶段有不同的要求。其中,设计完成能力是最基本的要求。

设计完成能力

第一阶段:可以完成设计,基本知道verilog的语法,能够把一个需求用代码实现出来,并且能够调试出来,经常会上网搜索现成的模块,对逻辑的硬件思维基本没有

第二阶段:开始关注代码风格,开始把自己的代码写的风格统一,并且开始关注代码的硬件实现,突出标志就是开始关注rtl视图,比较能明确的区分可综合语句与仿真语句的区别

第三阶段:在这个阶段,对模块内部的代码书写有了更加深刻的认识,模块内部的写法开始更加统一,基本上,模块内部的代码可以直接生成rtl视图。而且,开始考虑设计的复用,开始考虑模块的划分,注重模块接口,平台化等等

第四阶段:该阶段已经可以比较轻松的完成一个逻辑设计,而且结构合理,易读,可复用。

第五阶段:可以带领一个团队完成比较大规模的逻辑设计,分配不同的工作任务,可以准确的预估项目的风险,进度,可以准确的做出逻辑的整体方案,仿真方案,调试方案,对于整体的业务流有全面而深刻的认识

器件能力

第一阶段:知道FPGA的意思,但是基本上不知道fpga的内部结构

第二阶段:不怎么关注器件视图。但是基本知道器件的大概结构,知道fpga里面有le,ram,dsp,全局等等,对逻辑器件有了基本的认识

第三阶段:此时开始关注器件结构,了解fpga的内部架构,时钟网络,route,对时序约束有了基本的了解

第四阶段:对器件结构有了比较深入的认识,开始认识到不同厂家器件结构的不同

第五阶段:熟知各个厂家的各种逻辑器件的内部结构,基本逻辑单元结构,以及由此带来的代码风格的相应的改变

时序约束能力

第一阶段:基本不知道什么是时序约束

第二阶段:知道时序约束,会做时钟约束,可以根据简单的公式计算输出输出约束

第三阶段:懂得时序约束与布线的关系,熟练掌握最基本的常用约束

第四阶段:对时序约束有深刻的认识,可以主动设计整体时钟和复位系统

第五阶段:熟知时序约束,并且能够采取各种手段,解决各种时序问题

逻辑架构能力

第一阶段:无

第二阶段:有一点点概念,知道大概可以划分模块,对模块的功能,接口没有要求,一般有需要就直接加一个接口信号,不能在项目开始就主动设计

第三阶段:开始考虑设计的复用,开始考虑模块的划分,注重模块接口,平台化等等

第四阶段:接手一些比较大的设计,开始有架构的考虑,对于模块的划分,模块接口,模块职责,整体方案的实现,开始有更多的考虑,此时,可以做出比较好的,合理的方案

第五阶段:对整体的逻辑架构有所考虑,并且开始准确的划分逻辑架构,模块接口,功能划分,工作职责,协同交流

时序收敛能力

第一阶段:无

第二阶段:无

第三阶段:开始接触到时序收敛,有单个时序不过的信号,能够予以解决

第四阶段:开始主动设计时序,基本可以完成整个设计的时序收敛任务。

第五阶段:对于逻辑的布局,数据流走向有深刻的认识,能够在项目支出就通过设计来保证时序收敛。

接口掌握能力

第一阶段:开始接触简单的接口,

第二阶段:开始掌握如串口,spi,i2c等简单的外部接口

第三阶段:开始接触ddr,ssram,ad,lpc等等略复杂的接口

第四阶段:开始接触pcie,transceiver,rapid io,phy,等等复杂且带协议的接口

第五阶段:无,此阶段,不需要用掌握接口的多少来衡量

逻辑流程掌握能力

第一阶段:基本不知道正规逻辑流程,基本无设计文档

第二阶段:能够根据已知的流程完成设计,写出文档

第三阶段:比较熟练逻辑流程,并且能够顺利完成设计文档

第四阶段:有比较严格的逻辑流程,并且完成各种文档,对流程的认识比较深刻

第五阶段:可以根据现状,制定合理流程和文档要求

仿真验证水平

其他

逻辑工程师水平的V模型

根据以上不同阶段对各种能力的要求,可以完成V模型

其中,完成设计是最基本、核心的要求,随着水平的增长,对其他能力的要求也随之变高。

社招逻辑工程师笔式题库

最近公司招了很多人,不仅仅硬件在招,软件也在招人,实际上,我是非常羡慕软件的面试人员的,因为他们有笔试题。不过是自己出的也好,网上搜的也好,总之软件的很多知识,是可以通过一份试卷来先考察一下的。我经常看到软件的人把求职者带到会议室,给一份卷子,做完后来面试一下,也许半个小时就面试完了。而我,每次面试都要一两个小时。

我也在网上搜过逻辑的笔式题,不过,基本都是应届生的,社招的人,看来早已经没有兴致来分享一下自己的面经了。

其实,我每次面试,有一半的时间,都是在问每个人同样的问题,暂时就把这些问题,整理一份试卷吧,同时也参考上一章的V模型。

设计完成

主要针对简历中的设计提问。

请画一下该设计的硬件系统框图

主要考察对整个系统的了解,不仅仅要了解自己所做的部分,而且要了解跟自己像个的部分,积极主动、多思考多学习的人进步更快

针对fpga外围接口继续发问:

请画一下该接口/该模块的信号,时序图

逻辑工程师必须对外围接口信号,时序,有非常清晰的认识。

常用的逻辑电平有哪些

请画一下该设计的逻辑框图

主要考察其对自己所做逻辑的了解,以及讲述是否清晰,是否可以抓住重点,而不是纠结于细节。

以及画出的框图,是否清晰美观。很多人画的框图,面试完后再看,完全看不出是个逻辑框图。

该设计使用了多少逻辑资源

整个设计是用哪个芯片实现的,占了该芯片的多少资源,编译软件版本是多少,编译一次要多久

该设计有多少代码,方案、代码、仿真、调试,分别用了多久

请画一下该设计的时钟域

主要考察对逻辑的整体把握。可以继续发问时钟域转换的速率匹配等。

跨时钟域有哪些类型,分别应该如何处理

请画一下该设计的数据流

主要考察是否对整个设计非常了解。

实际设计考察

有一个设计,外部有一个ad芯片,lvds输入到fpga,其中有帧时钟,位时钟,数据有8根。上下沿采样,每个帧时钟里面有14个数据。帧时钟为40M。

请问在altera的器件上实现,你会如何做。

如果用cyclone3/4器件,io可以实现上下沿采样么。arriv系列呢。

位时钟要上全局么,为什么

如果在xilinx器件上实现,你会如何做。

如果用spartan6器件,位时钟需要上全局么

如果用kintex7实现,位时钟需要上那种资源,为什么,这几种时钟有什么区别

管脚分配时,需要考虑哪些

如果时序不过,有哪些手段,需要做位置约束么,需要将第一级寄存器放入iob么

管脚的时序约束如何做

数据采好后,跟内部时钟域怎么切换

器件结构

请写出任意一款使用过的fpga的型号全称

请解释该型号的每个字母段的意义

请分别写出xilinx和altera的低、中、高三个系列的名称

请画出任意一款fpga芯片的基本逻辑单元的框图。如altera的le结构,xilinx的slice结构。

针对该问题的进阶问题:(如果画的图跟datasheet的比较像,不过我至今没碰到过)

请画出移位寄存器是如何实现的

请画出组合逻辑级联是如何实现的

请画出任意一款fpga芯片的结构,包括内部逻辑要素结构,时钟树结构。

大概画出内部有ram,dsp等,ram和dsp是如何分布的。

时钟树必须画全

针对该问题的进阶问题:

请问该fpga有多少个全局时钟线

分别分布在哪里

有哪些信号可以上全局

pll的输入有哪些信号可以上

pll的输出是否要上全局,是否可以不上全局

pll有多少种模式,分别是什么意思

全局时钟线的延时大概为多少

请画出任意一款fpga芯片的内部路由示意图

请画出任意一款fpga芯片的io模块示意图

在fpga内部,下降沿采样时如何实现的

为什么xiliinx不建议使用异步复位

xilinx和altera的器件有什么区别。软件有什么区别

时序约束

一个完整的逻辑设计,应该包括那些时序约束

请画图解释tco\_max=2ns,tco\_min=1ns的意义

针对一个具体的管脚,做一个输入时序约束,输出时序约束

请画图解释multi\_cycle

请问clk\_group有什么作用

逻辑架构

逻辑模块划分的原则是什么,请举例说明

如何让一个模块的可复用性更好

如何让一个设计可以在不同的fpga芯片上实现

是否有代码重构的经历,为什么,新旧代码的区别在哪里

如何评价一个逻辑设计的优劣

时序收敛

在cyclone4的-8的器件上,160M时钟下,组合逻辑级联最多可以做多少级

请讲解一个遇到过的时序收敛的实例

如何保证一个设计的时序收敛

如何规划整个fpga内部的模块位置,以及外部的管脚分配,数据流应该遵循哪些原则

接口掌握

请画出i2c的时序

请画出spi的时序

请画出ddr用户端的时序。

请画出pcie的基本协议

请画出Transceiver的内部结构

逻辑流程

逻辑设计的整个流程包括那些

每个阶段占的时间大概有多少

与其他方向的交互都发生在哪些阶段

需要有哪些输入输出文档

逻辑的详细设计文档一般包括哪些内容

对于逻辑进度是如何评估的,在整个项目周期中,平均每天的代码量是多少

对于设计质量,是如何评价的,每千行代码,允许的bug数目在多少

逻辑工程师的水平是如何划分和评价的,主要有哪些方面,不同等级的要求是怎样的

其他

你做过的,认为最好的一个设计是什么,为什么

你对于以后的职业规划师如何考虑的

你觉得你的逻辑设计水平处于什么阶段,有哪些还需要提高

本文转载自公众号:芯片数字实验室

原文链接:https://mp.weixin.qq.com/s/w6aQVyG1i3iRHvn9UUMrLg

未经作者同意,请勿转载!

推荐阅读

想了解更多内容,欢迎关注芯片数字实验室专栏,由于工具,你可以专注在更重要的事情上。