转载自:知乎

首先附上传送门:

https://hdlbits.01xz.net/wiki/Truthtable1

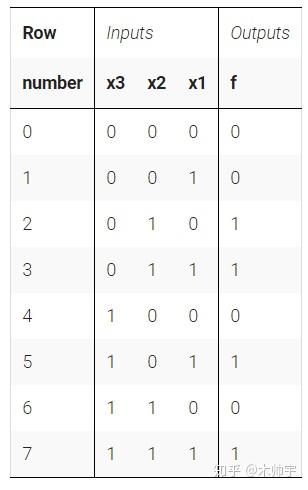

Problem 50 Truth tables 真值表

在前面的练习中,我们使用简单的逻辑门和多个逻辑门的组合。这些电路是组合电路的例子。组合意味着电路的输出只是其输入的函数(在数学意义上)。这意味着对于任何给定的输入值,只有一个可能的输出值。因此,描述组合函数行为的一种方法是显式地列出输入的每个可能值的输出应该是什么。这是一张真值表。

对于n个输入的布尔函数,有2n个可能的输入组合。真值表的每一行列出一个输入组合,因此总是有2n行。输出列显示每个输入值的输出应该是什么。

上述真值表适用于三输入一输出函数。它为8个可能的输入组合中的每一个都有8行,以及一个输出列。输出为1时有四个输入组合,输出为0时有四个输入组合。

从真值表合成电路,且仅限使用一组标准逻辑门,将如何构建电路呢?

本解析采用最小项之和的方法来构建电路图,最小项表达式为真值表中每一个对应函数值为1的输入变量,将上图真值表中函数值为1的最小项取出相加,便是函数最小项表达式。

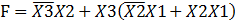

上图最小项表达式为:

化简后如下所示:

(具体化简公式可自行百度)

module top_module(

input x3,

input x2,

input x1, // three inputs

output f // one output

);

assign f = (!x3 & x2) | (x3 & x1);

endmodule

Problem 51 Two-bit equality

创建一个两输入inputs A [1:0], B[1:0],一输出Z。当A 与 B 相等时,Z 输出为1, 否则为0;

牛刀小试

//Module Declaration

module top_module ( input [1:0] A, input[1:0] B, output z);

module top_module ( input [1:0] A, input [1:0] B, output z );

always @ (*)

begin

if(A == B)

z = 1;

else

z = 0; //注意需要else,不仅为符合题意,且需要消除latch。

end

endmodule

Problem 52 Simple circuit A

牛刀小试

创建一个电路,其功能可以实现 z = (x ^ y) & x

//Module Declaration

module top_module (input x, input y, output z);

assign z = (x ^ y) & x;

endmodule

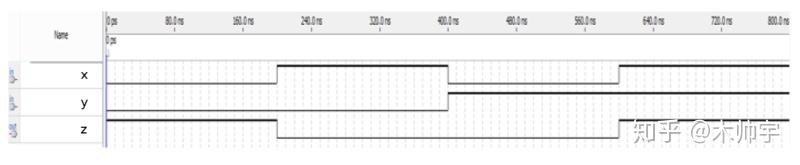

Problem 53 Simple circuit B

牛刀小试

根据仿真时序图创建电路B。

根据时序图可画出真值表,再推导出电路图。但根据观察所得输出 z 为 x 与 y 的同或输出,即相同为1, 不同为0;故实现代码如下:

//Module Declaration

module top_module (input x, input y, output z);

assign z = x ^~ y;

endmodule

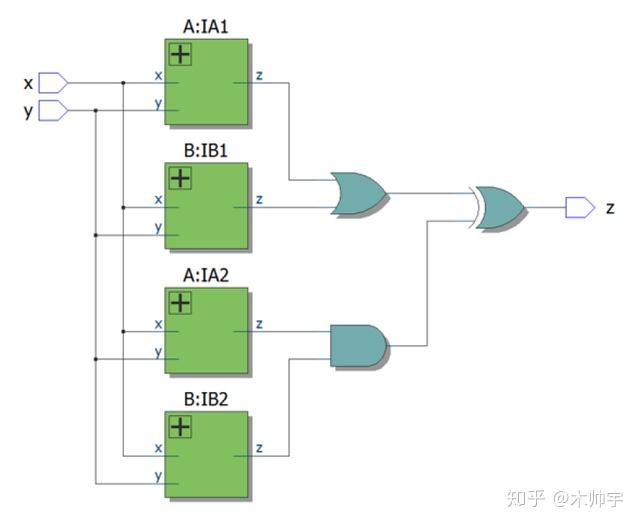

Problem 54 Combine circuits A and B

根据子模块Problem 53 与 54 来实现如下电路:

//Module Declaration

module top_module

(

input x,

input y,

output z

);

wire z1, z2, z3, z4;

assign z1 = (x^y) & x;

assign z2 = x ^~ y;

assign z3 = (x^y) & x;

assign z4 = x ^~ y;

assign z = (z1 | z2) ^ (z2 & z3);

endmodule

推荐阅读

- HDLBits:在线学习 Verilog (十 · Problem 45 - 49)

- HDLBits:在线学习 Verilog (九 · Problem 40 - 44)

- HDLBits:在线学习Verilog(八 · Problem 35-39)

关注此系列,请关注专栏FPGA的逻辑