环境设置

创建一个单独的目录(例如,innovus)。创建子目录synth和lib

1、 将full\_adder\_pads\_syn.v移动到synth目录

我们可以看出来这是一个综合后gale-level的verilog门级网表。

2、将osu05\_stdcells.lef移动到lib目录

读入设计

1.在Unix提示符后,键入:innovus

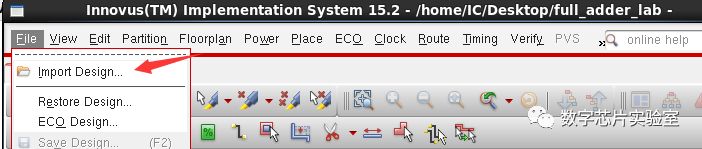

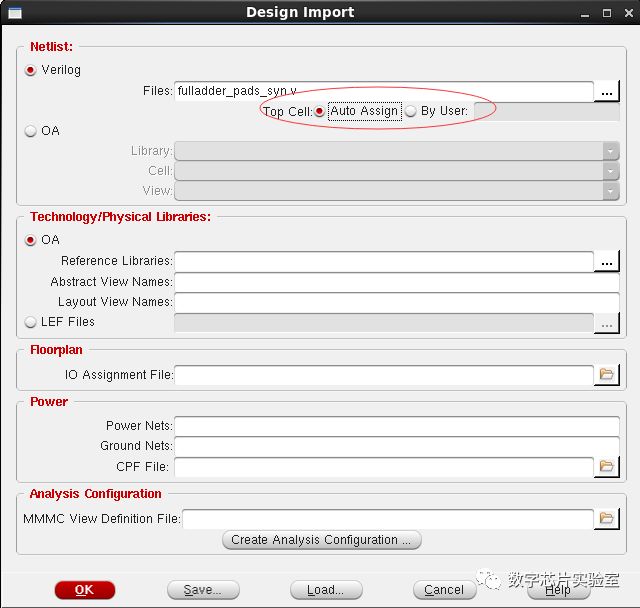

2.出现innovus工具窗口时,在菜单栏选择File->Import Design 读入设计

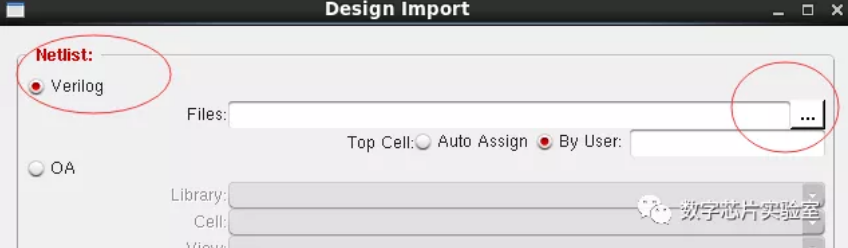

单击 [...]读入Verilog网表文件

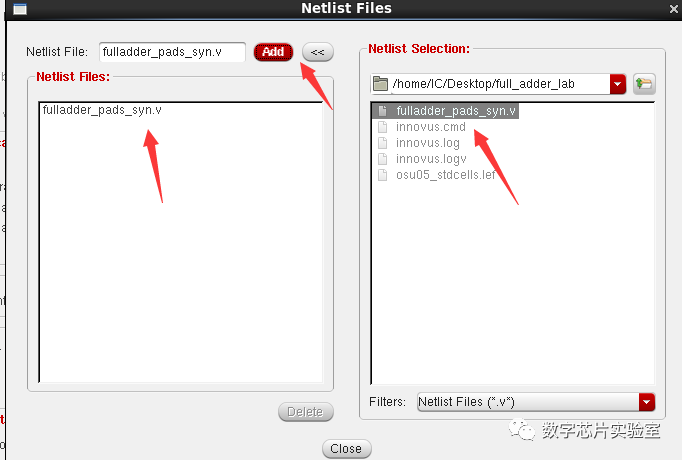

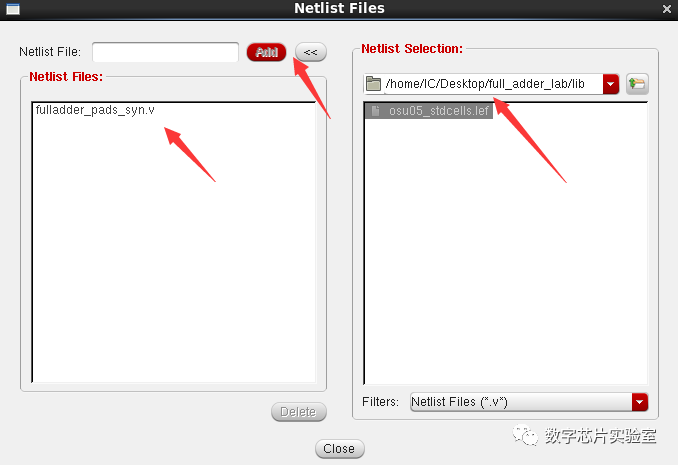

1. 单击**“>>”**按钮展开窗口以显示目录

选择文件full\_adder\_pads\_syn.v并单击Add按钮将其添加到Netlist文件列表中。

6.对于Top Cell,选择**“Auto Assign”**

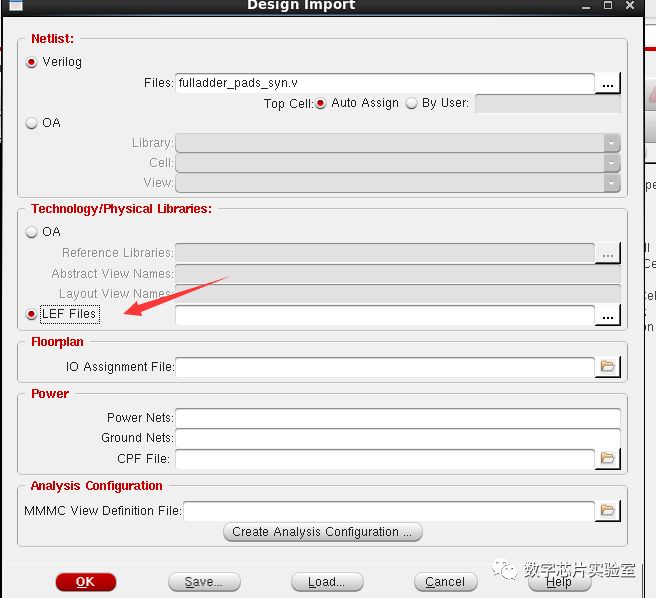

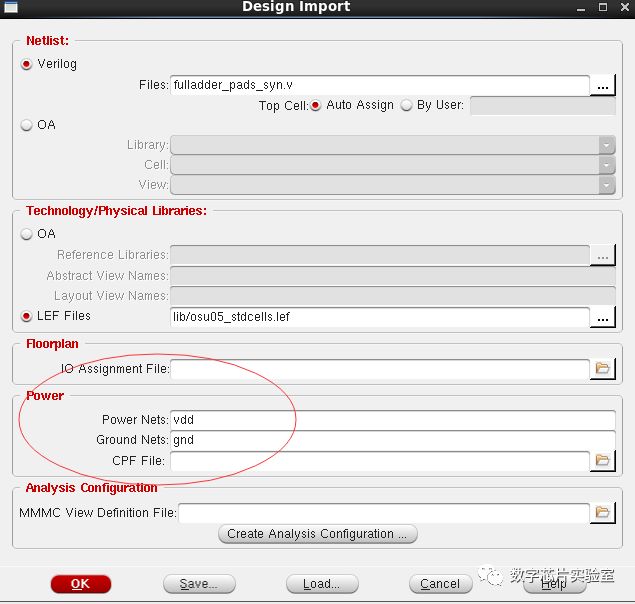

对于Technology/Physical Libraries,选择**“LEF文件”。单击[...]**按钮打开LEF文件

使用与读入Verilog Netlist文件相同的方法,选择文件lib/ osu05\_stdcells.lef

对于Power,输入以下内容:

a. Power Nets: vdd

b. Ground Nets: gnd

点击 OK

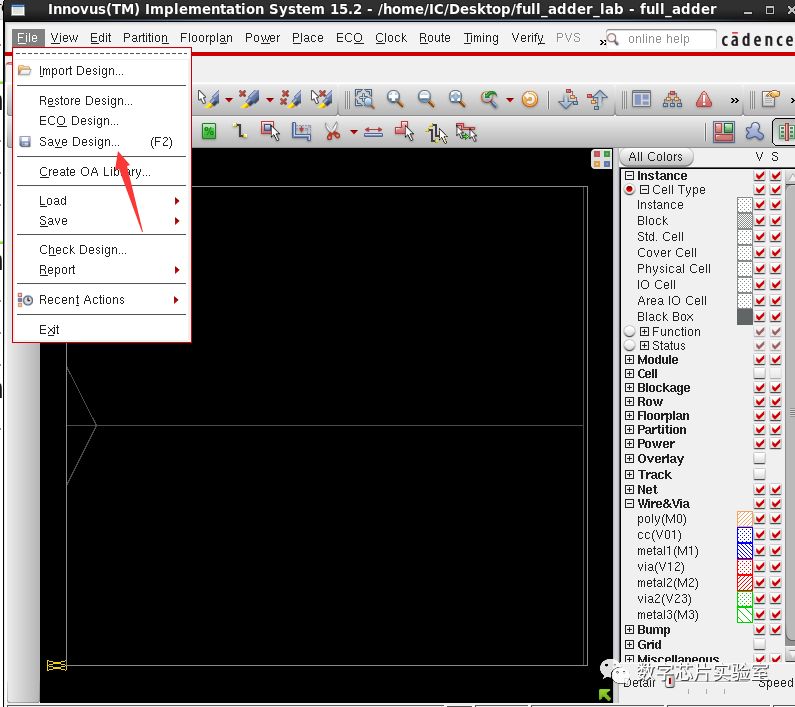

保存和恢复设计

NOTE:切记要及时保存你的设计选择File, Save Design

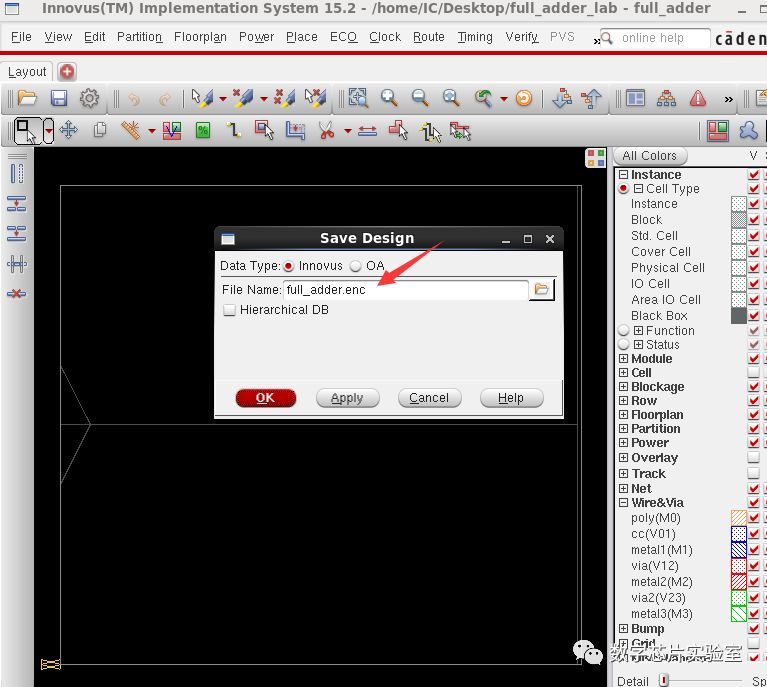

在Save Design窗口中,选择数据类型:innovus。程序将分配一个扩展名为*** .enc**的默认文件名。可以更改名称,但不要更改扩展名。

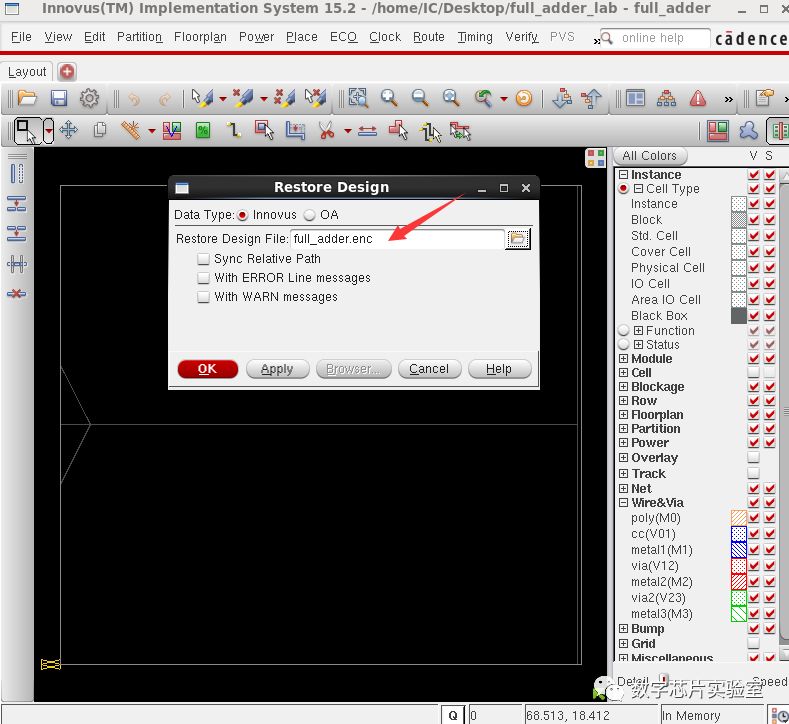

要加载已保存的innovus文件,请执行File, Restore Design。 在“Restore Design”窗口中,选择数据类型:innovus。选择要还原的文件。

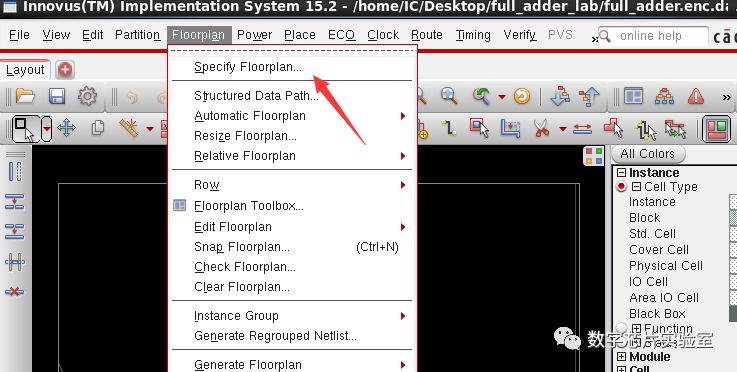

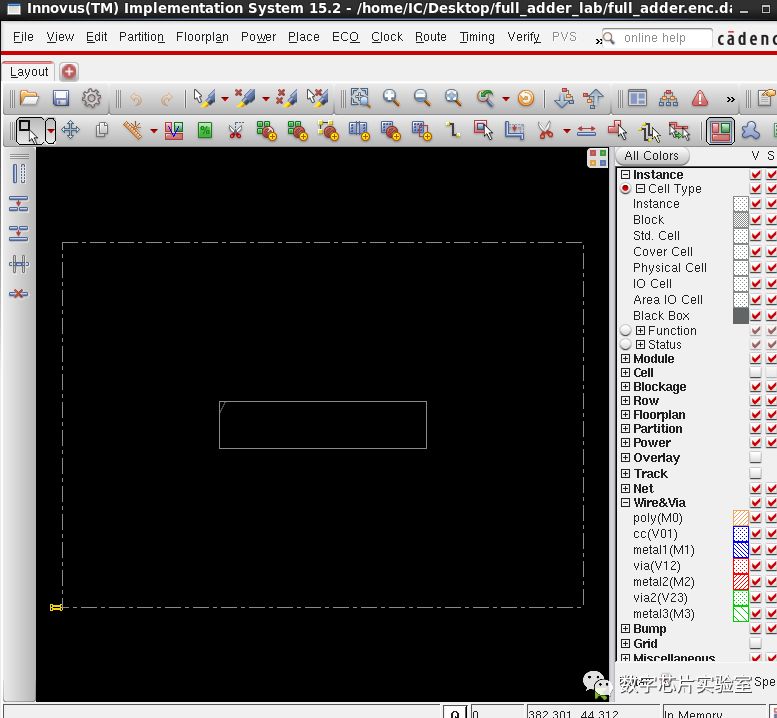

Floorplanning

在innovus工具菜单栏中,选择Floorplan,Specify Floorplan

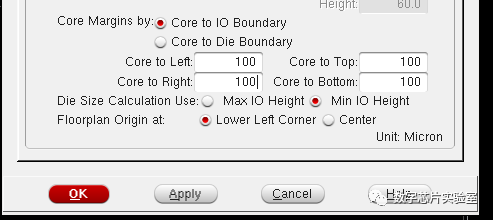

1.在“Basic”选项卡中,选择以下选项:

Core Margins - 选择Core to IO Boundary并设置为100

2.单击“OK”

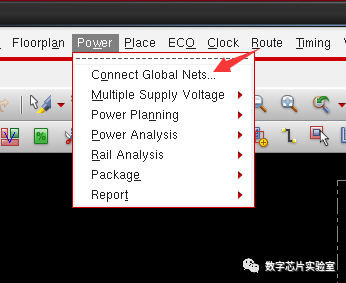

Power Planning

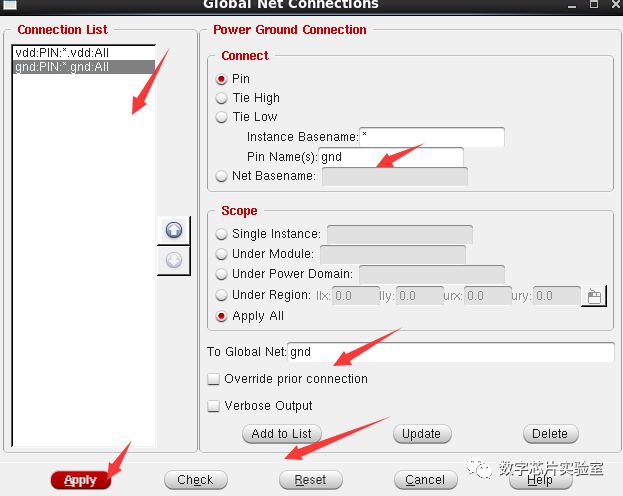

在innovus工具菜单栏中,选择Power,Connect Global Nets以进行全局电源网络连接

1. 在Power Ground Connection中。

a、在Connect区域中,选择Pin

b、“Scope”区域中,选择“Apply All”

2.对于每个net( vdd和gnd),执行以下操作:

a、在以下框中输入net名称(vdd或gnd):

i. To Global Net

ii. Pin Name(s)

b、 单击“Add to List”按钮

3.单击“Apply”,然后单击“Cancel”

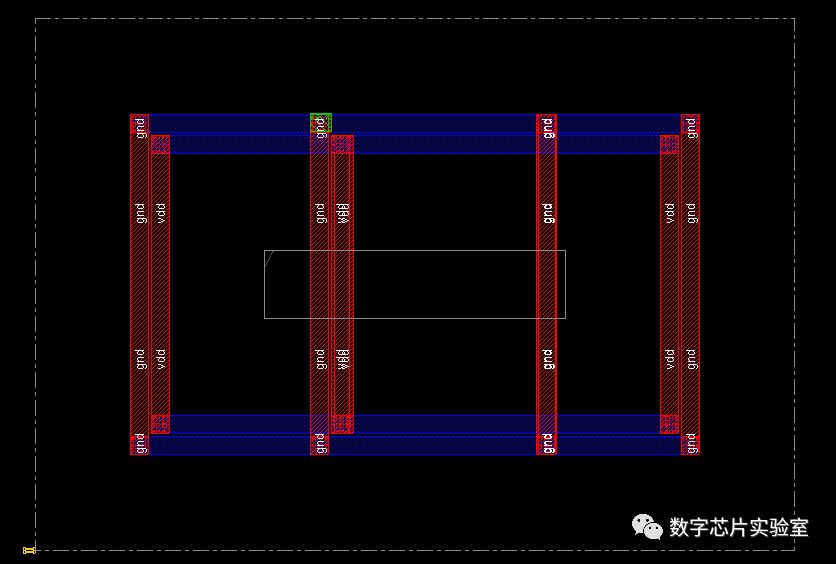

Power Rings

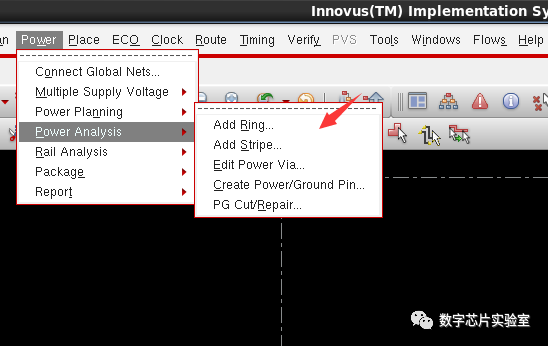

在innovus工具菜单栏中,选择Power->Power Planning->Add Rings

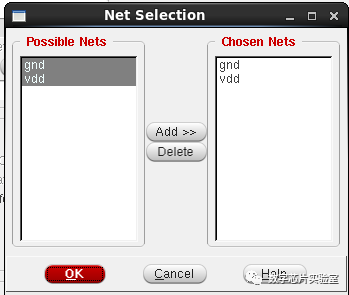

对于Net(s),输入vdd和gnd,如下所示:

a、单击[...]框进行Net Selection

b、从Possible Nets列中选择vdd和gnd

C。单击“Add”以复制到“Chosen Nets”列

d。单击OK

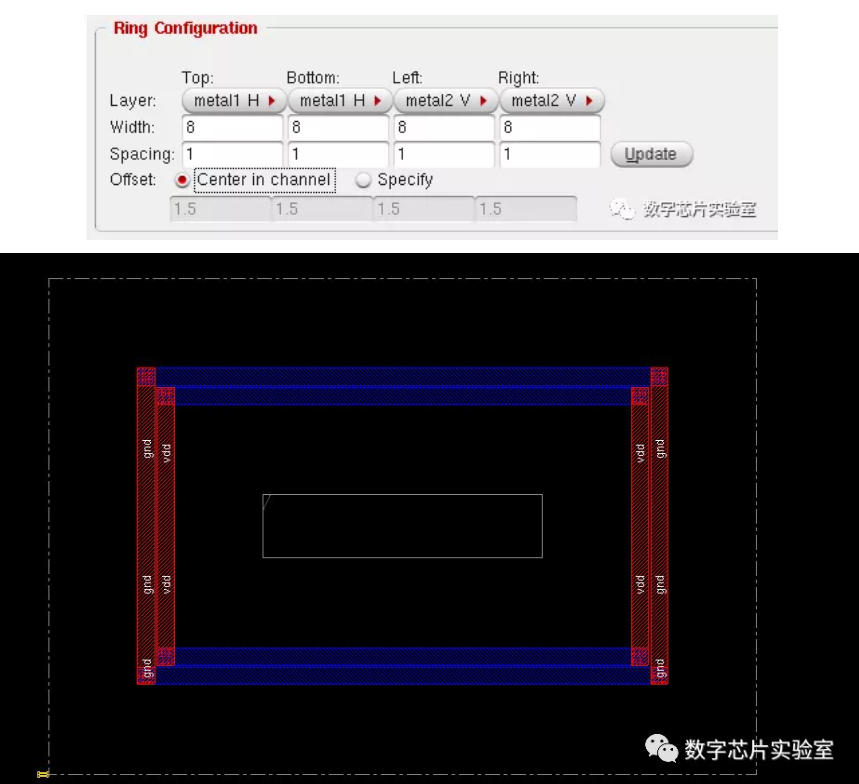

在Ring Configuration中,选择metal1作为Top和Bottom,metal2作为Left和Right

a、宽度为8

b、间距为1

C、Offset为 “Center in channel”

单击“OK”

Power Stripes

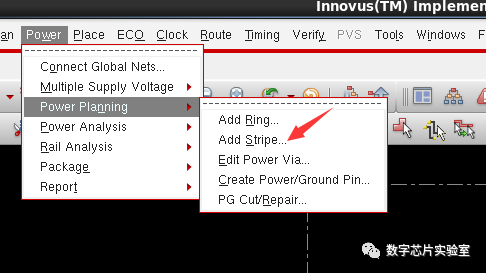

在innovus工具菜单栏中,选择Power->Power Planning->Add Stripes

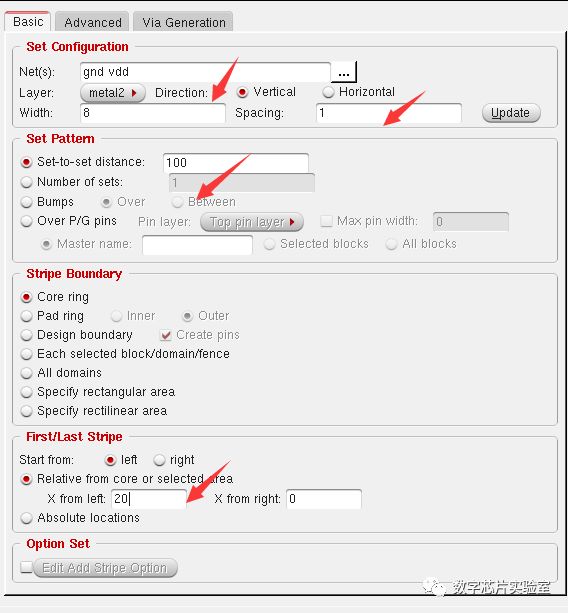

1. Basic

对于Net(s),输入vdd和gnd nets,如下所示:

单击[...]框以获取“Net Selection”窗口

从Possible Nets列中选择vdd和gnd

单击“Add”以复制到“Chosen Nets”列

单击OK

在Set Configuration中,选择Layer metal2和Direction vertical。宽度应为8、间距为1

在“Set Pattern”中,将“Set-to-set”设置为100

在First/Last Stripe中,设置从左到右相对于core或选定区域的距离为20

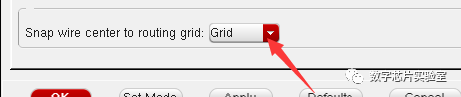

Advanced选项

将Set Snap wire center to routing grid设置为Grid

单击“OK”

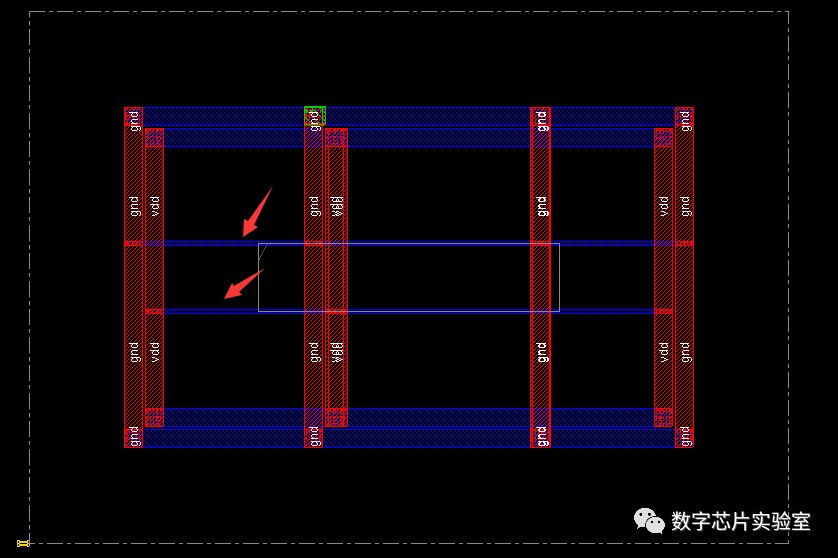

将电源连接到Standard Cell Rows

在innovus工具菜单栏中,选择Route-> Special Route,然后单击“OK”。生成power(vdd)和gnd(gnd)给standard cell rows供电。

Placing the Standard Cells

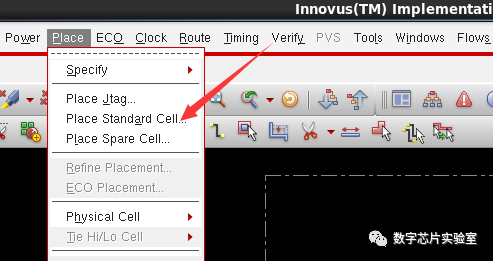

在innovus工具菜单栏中,选择“Place”,“Standard Cells”

选择“Run Full Placement”和“Include Pre-Place Optimization”

单击“OK”

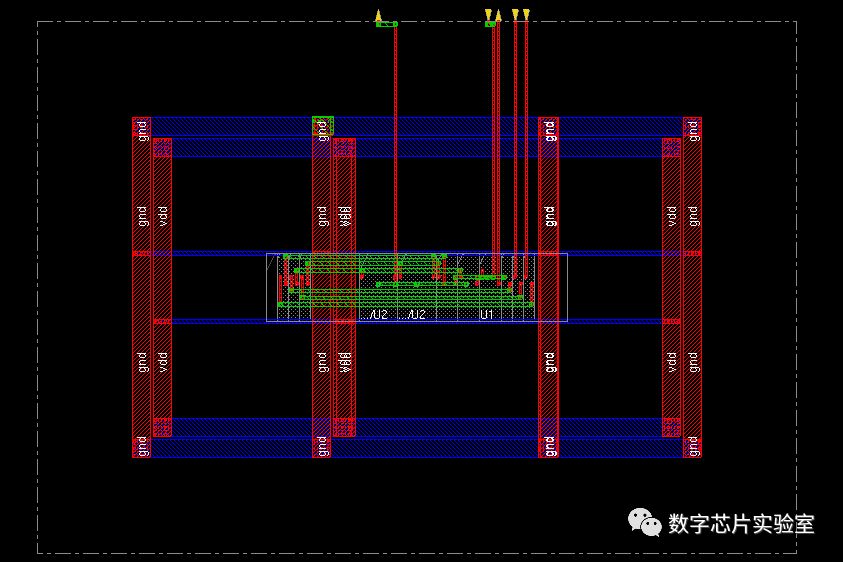

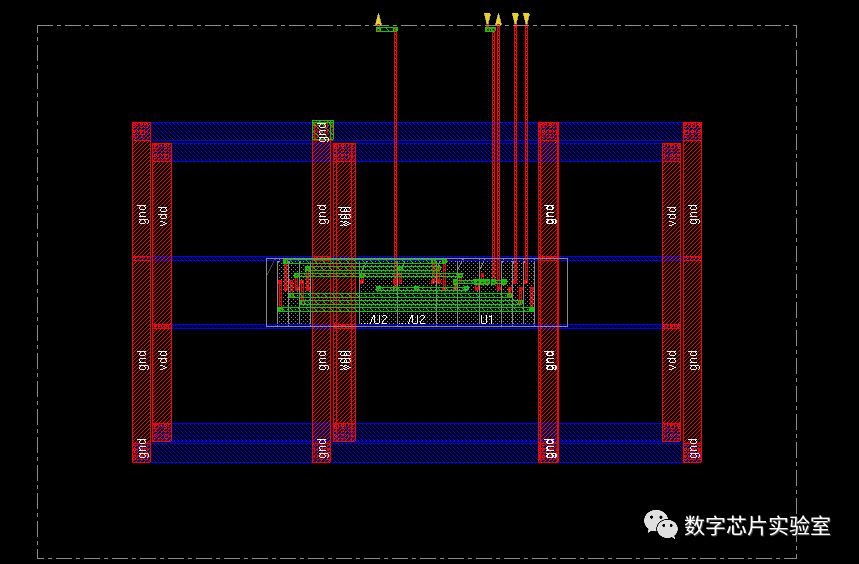

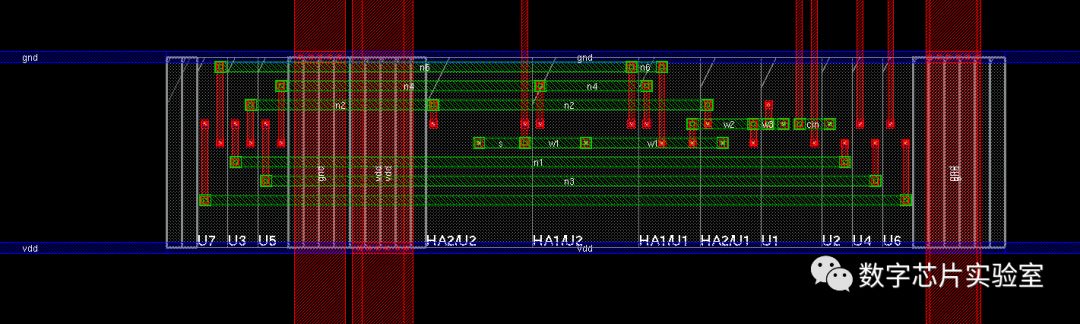

放置Standard Cells后,在innovus窗口中更改为“Physical View”以查看placement结果

Routing

在innovus工具菜单栏中,选择Route->NanoRoute->Route,点击Ok

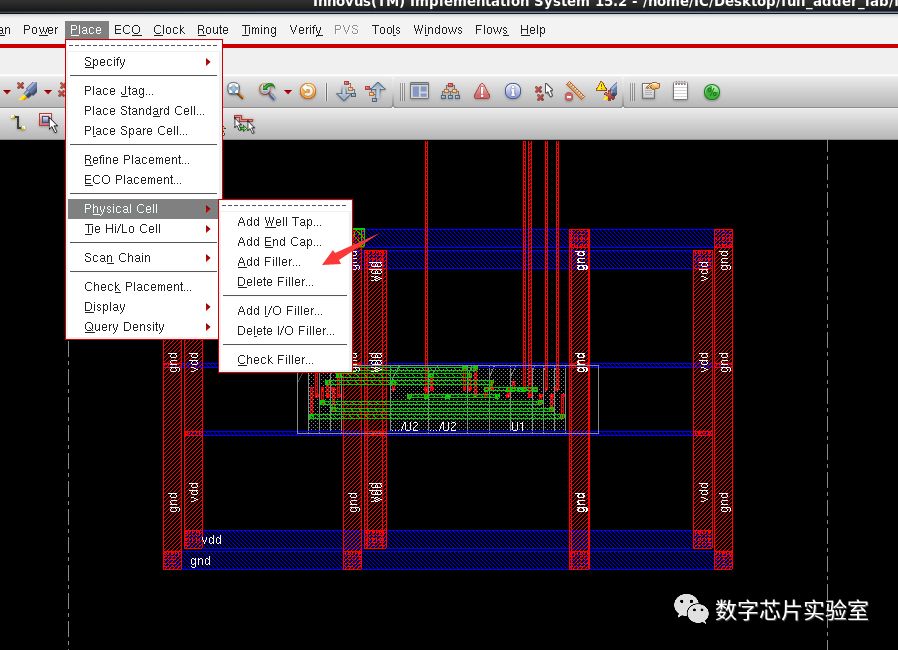

添加Filler Cells

现在我们已完成我们设计的placement和routing,我们将添加Filler Cells。选择Place->Physical Cell->Add Filler。

在Add Filler窗口中,输入Cell Name “FILL”并选中Mark Fixed。单击ok。

推荐阅读

想了解更多内容,欢迎关注芯片数字实验室专栏,由于工具,你可以专注在更重要的事情上。