在IC 圆桌派群,每每提及power 都会说到glitch power, 数字电路实现中有许多重名的概念,如DRC 可回顾《数字电路实现中的DRC》如Glitch.

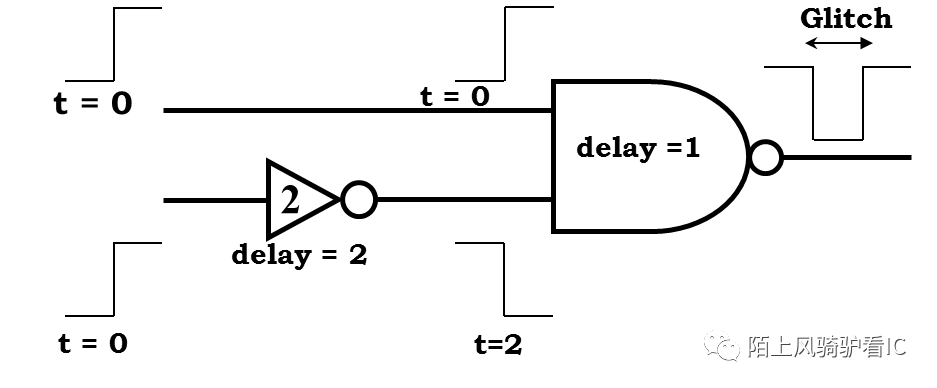

Glitch 在数字电路实现中,其一是指由于不同信号到达组合逻辑单元输入端的时间差引起的组合逻辑输出端的无效翻转;其二是指由于耦合电容导致的串扰引起的glitch, 关于这种glitch 请回顾《论STA | 数字电路中的串扰》。

组合逻辑无效翻转Glitch

这种Glitch (下文称为逻辑glitch)是由于组合逻辑单元输入信号到达时间不同而产生的虚假翻转,这些翻转不是逻辑运算所需要的。理想情况,在每个时钟周期内,组合逻辑的输出信号最多翻转一次,但实际中,组合逻辑的输出信号在每个时钟周期内都不止翻转一次,这些不必要的翻会导致额外的功耗,这类功耗就是所谓的『Glitch power』, 据统计在16nm 以下的工艺中,Glitch power 占总动态功耗的20%\~30% 是非常可观的;而且这些无效翻转,会导致意外峰值电流,这些峰值电流发生在很短的时间内会导致很大的IR-Drop, 从而影响电路的性能和可靠性。

逻辑 Glitch 因为有百害而无一利,所以一直是研究热点,到目前为止C 家综合工具跟P&R 工具在读入activity 文件做Dynamic power 优化时都会尽量去优化Glitch power, 但到目前为止也没有什么办法完全消除Glitch power. 一些文献里提出了若干方法,有兴趣的可以自行查阅:

- Delay balancing: In this method the inputs are made to arrive at the same time by inserting extra delay buffers on selected paths[2].

- Hazard filtering: In this method the gate delay is made greater than the differential delay at the inputs of the gate to filter the glitch[3].

- Gate s****izing: In this method every gate is assumed to be an equivalent inverter[4].

- Transistor sizing: This method treats every transistor’s size as a variable and tries to find glitch-free design[5].

- Linear programming: In this method the gate delays are treated as variables and optimum delays are found by solving a linear program (LP)[6,7] which is implemented using AMPL programming method[8].

- Variable input delay method: Raja in[1] proposed variable input delay method which involves insertion of “permanently on” series transistor at the input of logic gate for glitch free digital circuits.

解决峰值瞬态IR-Drop 最常用的方法是在芯片中撒入去耦电容 ( Decap cell ), 这些Decap 充当局部电荷储存器,从而减少峰值IR-Drop 对临近电路的影响。 然而,从90nm 开始,Decap cell 会造成显著的栅极隧穿漏电流,对于90nm 之后的工艺由于栅氧进一步变薄,Decap cell 造成的栅极隧穿漏电流会更大,至于Decap 对FinFet 工艺的作用与影响,待老驴研读后再搬来,

参考文献:

http://article.sapub.org/10.5923.s.msse.201302.04.html

【1】T.Raja, V.D.Agarwal “Variable input delay CMOS logic for low power design”, IEEE Trans. Circuits syst.,vol.-17,no.10,October 2009.

【2】K. Roy and S. C. Prasad, Low-Power CMOS VLSI Circuit Design. New York: Wiley, 2000.

【3】V. D. Agrawal, “Low power design by hazard filtering,” in Proc. 10th Int. Conf. VLSI Des., Jan. 1997, pp. 193–197.

【4】M. Berkelaar and E. T. A. F. Jacobs, “Gate sizing using a statistical delay model,” in Proc. Des. Autom. Test Eur. Conf., Paris, France, Mar. 2000, pp. 283–290.

【5】V. Sundararajan, S. Sapatnekar, and K. Parhi, “Fast and exact transistor sizing based on iterative relaxation,” IEEE Trans. Comput.-Aided Des. Circuits Syst., vol. 21, no. 5, pp. 568–581, May 2002.

【6】T. Raja, “A reduced constraint set linear program for low-power design of digital circuits,”M.S. thesis, Dept. ECE, Rutgers Univ., Piscataway, NJ, 2002.

【7】T. Raja, V. D. Agrawal, and M. L. Bushnell, “Minimum dynamic power CMOS circuit design by a reduced constraint set linear program,” in Proc. 16th Int. Conf. VLSI Des., Jan. 2003, pp. 527–532.

【8】R. Fourer, D. M. Gay, and B. M. Kernighan, AMPL:A Modeling Language for Mathematical Programming. South San Francisco, California: The Scientific Press, 1993.

作者:陌上风骑驴

来源:https://mp.weixin.qq.com/s/aQYeffJkp4mBVIjlbXjSHw

作者微信公众号

相关文章推荐

•从EDA使用,捋数字芯片设计实现流程 | 验证

•人物访谈:因为热爱而努力拼搏的Jessica

更多IC设计技术干货请关注IC设计技术专栏。