接着《从EDA 使用,捋数字芯片设计实现流程 | 上》捋,实际项目中验证跟综合从RTL coding 开始就会交叉进行,反复迭代。

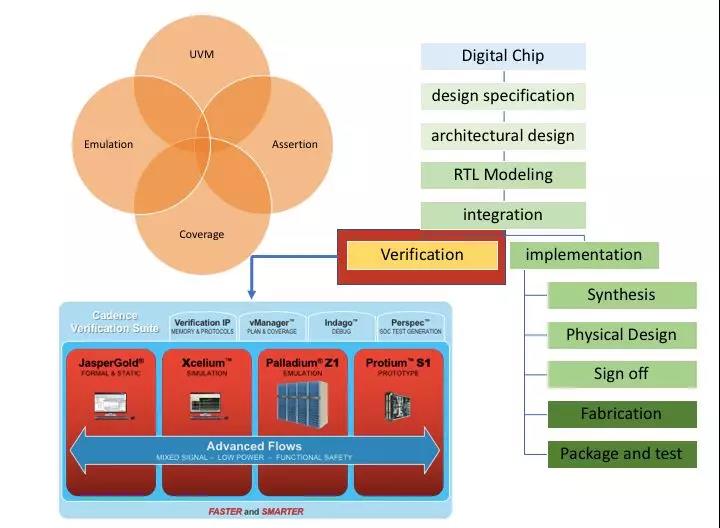

验证在数字芯片设计中占很大比例,近些年在设计复杂度的推动下验证方法学跟验证手段在不断更新,从OVM 到UVM, 从Dynamic verification 到Static verification, 从FPGA 到Emulator, 所有革新目的可概括为:快速、完备、易调试。验证涉及到许多方面,验证工程师一方面要对相关协议算法有足够了解,根据架构、算法工程师设定的目标设计仿真向量;另一方面要对设计本身足够了解,以提高验证效率,缩短验证时间。验证工程师需要掌握许多技术,需要使用许多工具。

- 语言:各种脚本语言之外,C/C++, SystemVerilog, Verilog.

- 协议:各种接口协议,各种通信协议,各种总线协议;

- 工具:动态仿真工具,静态仿真工具,FPGA, Emulator.

数字验证领域,依旧是C, S, M 三家几乎全霸,老驴已不做验证多年,对S, M 两家验证相关工具除了VCS, Verdi, Modelsim 其他几乎无知,此处拿C 家验证全套为例。

- Static Verification: Jasper Gold 是C 家新近推出的静态验证工具,驴所理解的静态验证是基于断言的验证方法学,所谓静态即不需要输入测试激励,验证过程是纯数学行为。

- Dynamic Verification: Xcelium 是C 家的动态验证工具,驴所理解的动态验证是基于UVM 的验证方法学,通过输入测试激励,监控仿真结果,分析覆盖率完成功能验证。

- Emulator: 硬件仿真加速器,粗暴理解:有debug 功能的集成了丰富接口的巨型可编程阵列;特点:超高速验证、支持系统软件调试。帕拉丁是C 家在验证领域的明星产品,是行业翘楚,据说常有钦差莅临硅厂在帕拉丁前驻足良久,赏其外形之美,赞其功能之强。

- Verification IP: 验证需要各种验证模型,各种IP, 各种总线,各种高速接口。

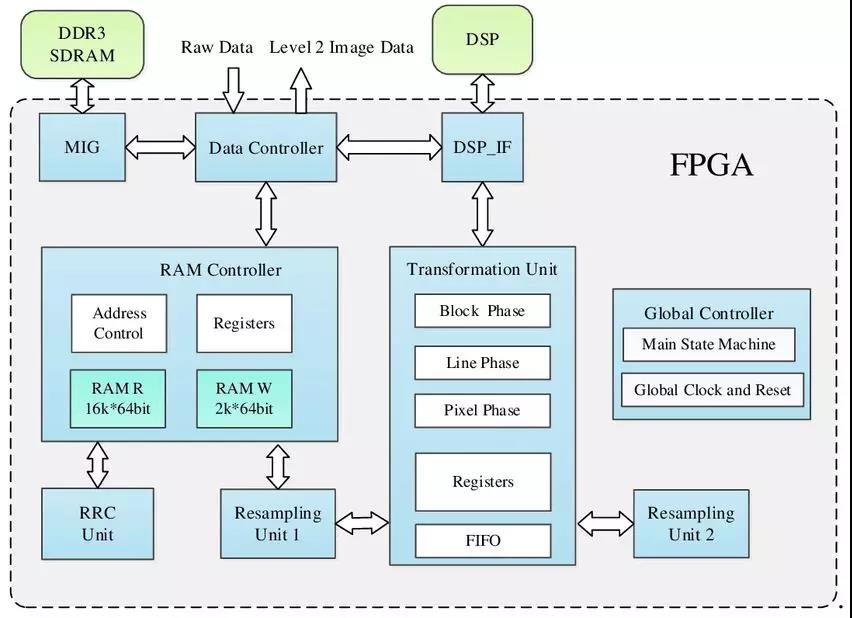

FPGA 的一大应用是验证,故提一嘴。在世上曾经有两家牛逼闪闪的FPGA 公司,一家是Altera 另一家是Xilinx, 后来Altera 像Mentor 一样找了个大爷把自己卖了。FPGA 内除了可编程逻辑之外,通常还会集成各种IP, 如CPU, DSP, DDR controller 等。每家FPGA 都有各种配置,根据集成的IP, 可编程逻辑的规模,可达到的速度,价格相差极大。相对于ASIC, FPGA 也有一套对应的EDA 工具,用于综合、布局布线、烧录、调试。如:Synplify, Quartus.

国内现状:Static Verification, Dynamic Verification, Emulator 几乎空白;国内有一些FPGA 公司,在中低端领域已经做得非常不错,但是高端领域几乎空白。任重而道远,不矫饰,脚踏实地干!

声明:老驴不做验证多年,文中难免偏误,恳请各位驴友指正补充。

作者:陌上风骑驴

来源:https://mp.weixin.qq.com/s/VylYz71usfrQxJRm3V3\_1A

作者微信公众号

相关文章推荐

•人物访谈:因为热爱而努力拼搏的Jessica

•论功耗:低功耗检查

更多IC设计技术干货请关注IC设计技术专栏。