真是骑驴看唱本,想起一出是一出,STA 之前的若干文还没收尾,就又想挖一大坑。撩一把SI. 数字电路中的串扰,是个庞大艰深的话题,Signal Integrity (SI) 分析是STA 中重要且复杂的部分。数字电路是01 的世界,用『攻受』来理解数字电路的串扰很合适。

在数字电路中,任何两条相邻的线之间都可能『私通』,私通的通道是『耦合电容』。如果用基佬世界的『攻受』来对应,那任何一条net 都是0.5 只要『时间窗口』对,都进可攻退可受,如东方不败一般,

通常,在STA 中将被分析的net 称为"victim" 此处对应为"受",把跟被分析net 私通的所有其他net 称为"Attacker/ Aggressor" \<C 家跟S 家攻的英文名儿竟然不一样!>此处对应为"攻"。

不是有了私通通道,攻就可以攻击到受,还需要看:

- 攻的强弱:Strength of attacker.

- 受的强弱:Strength of Victim.

- 私通通道的多少: the amount of cross-coupled capacitance;

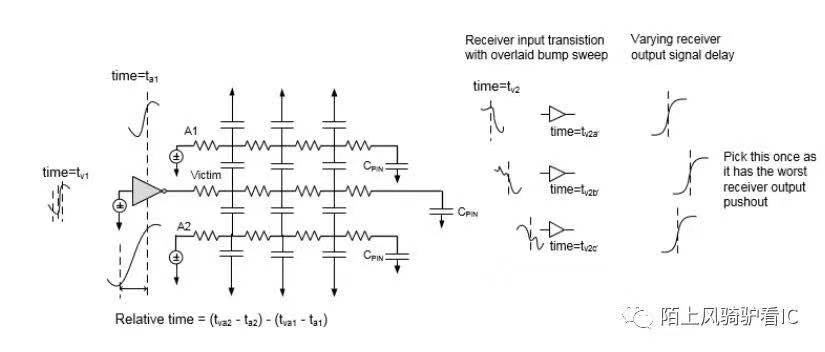

- 时间窗口:relative time and the transition rate of the sinal transitions.

- 翻转方向:the switching directions.

- 攻的联合:the combination of effects from multiple attacker.

理想数字电路跟理想世界一样,只有纯粹的01 要消除一切0.5. 但串扰不同于基佬,基佬可以使世界变得更美好,串扰却总是具有破坏性。串扰的破坏性根据『受』所处的『动静』状态体现于两方面:

- Delta delay.

- Glitch.

Delta Delay

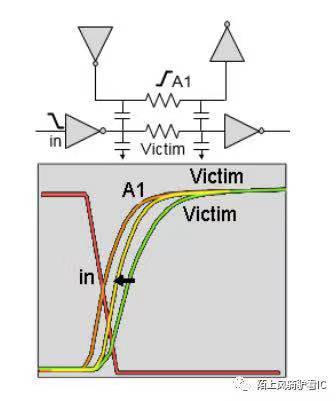

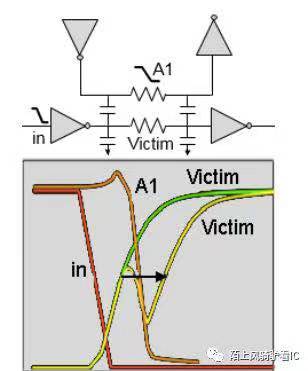

体现『受』翻转时,『攻』对其进行的骚扰,『攻』与『受』同向翻转时,『攻』会加快『受』的翻转,使得『受』的延时变短。

『攻』与『受』异向翻转时,『攻』会减缓『受』的翻转,使得『受』的延时变长。

攻受的翻转方向是随机的,在当前STA 分析中,保险起见,对于同一条net 如果是计算early delay 则认为攻受同向,如果是计算late delay 则认为攻受异向。

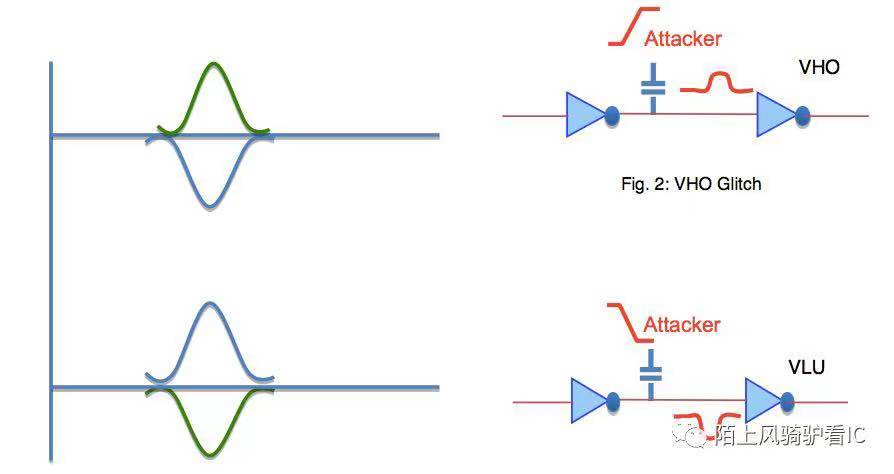

Glitch

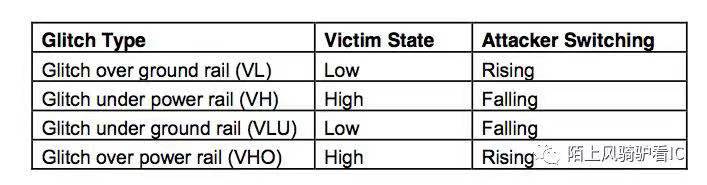

体现『受』静止时,『攻』对其进行的骚扰,这个骚扰如果严重会引起逻辑功能失效。根据『受』所处的电平不同,『攻』对其造成的影响可被分为如下四类:

- VHO:『受』处于高电平,『攻』正向翻转;

- VH: 『受』处于高电平,『攻』反向翻转;

- VLU: 『受』处于低电平,『攻』反向翻转;

- VL: 『受』处于低电平,『攻』正向翻转;

Delta Delay 跟Glitch 是对串扰的两种表征,都属于STA 范畴,分析时大部分计算过程一致,只是最后衡量的方式不同。

破个题,挖个坑,待驴慢慢填。

作者:陌上风骑驴

来源:https://mp.weixin.qq.com/s/cFBU3uJzVhj\_iCSYCVxU0Q

作者微信公众号

相关文章推荐

•曲线们 | 学习曲线预测单个晶体管的成本收益

•从EDA使用,捋数字芯片设计实现流程 | 上

更多IC设计技术干货请关注IC设计技术专栏。