题记:在《论综合:为什么做physical aware synthesis》中聊到了为什么要做physical aware synthesis,今天来聊如何做physical aware synthesis 及做physical aware synthesis 时需要注意的点。

方法学上,感谢DEF 架起了前后端之间的桥梁,DEF 将 floorplan 的信息传递给综合工具,使其可以在逻辑优化时考虑真实的『物理信息』,并根据DEF 的约束做placement 及global route , 依据global route的结果估算net delay,与此同时也做congestion 优化,完成所谓的 physical aware synthesis。

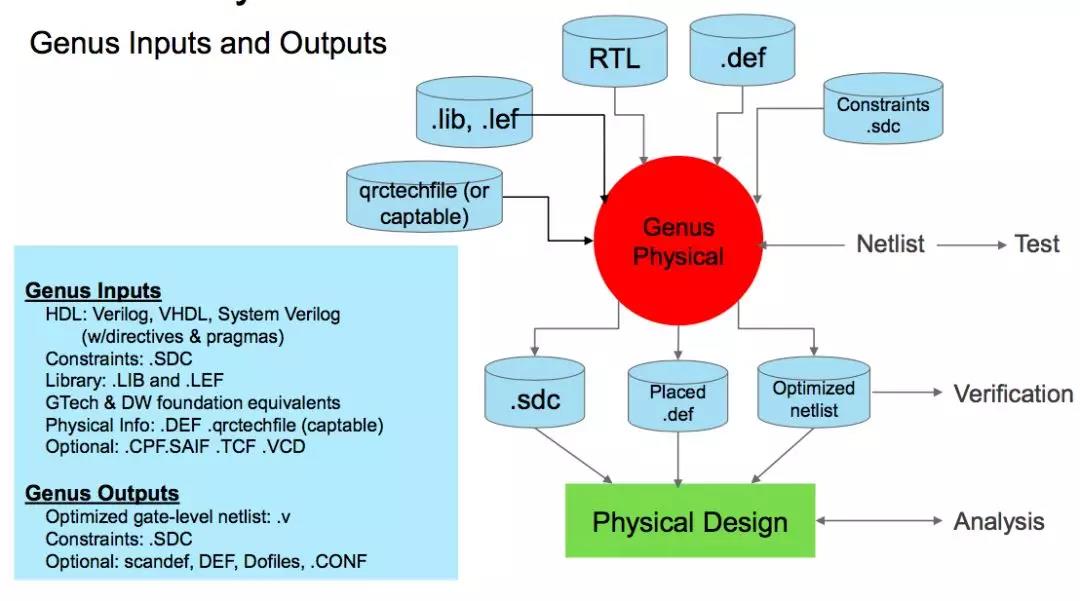

工具端,C跟S都跳脱不出方法学,只是实现方式上有所差别而已,S家的physical synthesis 除了要设physical 相关的变量之外,大概还需要额外三个东西(此处完全凭不靠谱的记忆,如有谬误请指正):1) dc\_shell -topo; 2) create MilkWay DB; 3) compile\_ultra -spg。本文将以C 家的Genus 为例来陈诉如何做physical aware synthesis。讲工具的套路都是从输入跟输出说起,然后再一一展开,下图是从Genus physical RAK上抠的图(RAK是一系列简单的lib,C家每个工具都有多个RAK, 在C家网站上可以下载到,强烈建议下载学习)。

Genus physical 的输入除了 lib/rtl/sdc 之外,还必须要有tech lef/ std cell lef/ macro cell lef; DEF; QRC tech file。

LEF: tech lef/std cell lef/ RAM lef 由foundry 提供,sub-block lef 由后端提供。

- 用命令:set\_attribute lef\_library $lef\_files 读入,必须将tech lef 放在lef file list的首位;必须要读全用到的所有cell 的lef,否则在log 中会看到警告:『由于某个cell 的物理信息不可用,所以该cell 被设成了不可用。』

- Genus 从LEF 中读入如下信息:

- CAPACITANCE CPERSQ

- EDGECAPACITANCE

- RESISTANCE RPERSQ

- SITE

- WIDTH

- Coupling capacitance

- Capacitanceper unit of area

- Fringing capacitance

QRC: QRC由foundry 提供,是个加密文件。

- 用命令:set\_attribute qrc\_table\_file $qrc\_files 读入.

- Genus 从QRC 中读入如下信息:

- PROCESS\_VARIATION

- BASIC\_CAP\_TABLE

- width

- Cc

- Carea

- Cfrg

DEF: floorplan 信息,由后端提供,后端大佬们说这是P&R 的灵魂所在,是基石是一切成功的基础。

- 在Innovus 用Defout -floorplan -NoStdCell写出一个包含以下部分的DEF,此处有注释。

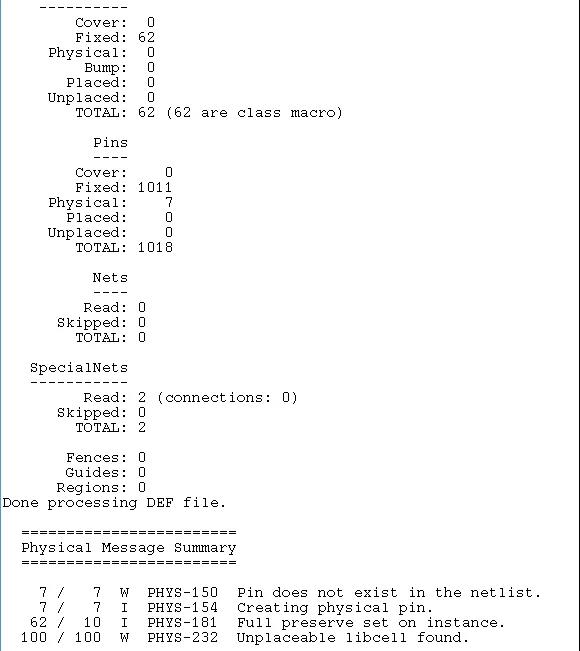

- 在Genus 中用命令read\_def 读入DEF file. Genus在读DEF 时会check DEF 的Quality 并会报出相关的warning, 读完DEF 后会生成一个如下的summary 报告,请修正需要修正的Error 跟Warning。

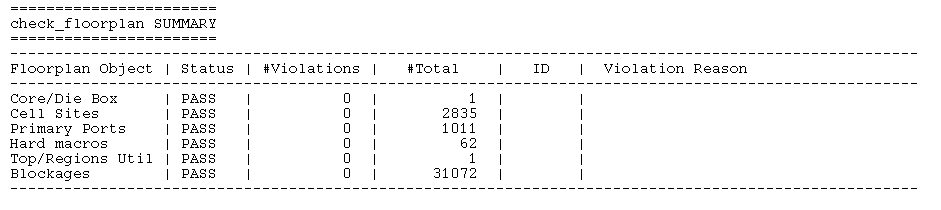

- 读完DEF 后用命令 check\_floorplan 进一步check DEF 的quality, 并及时修正Error 跟 Warning。

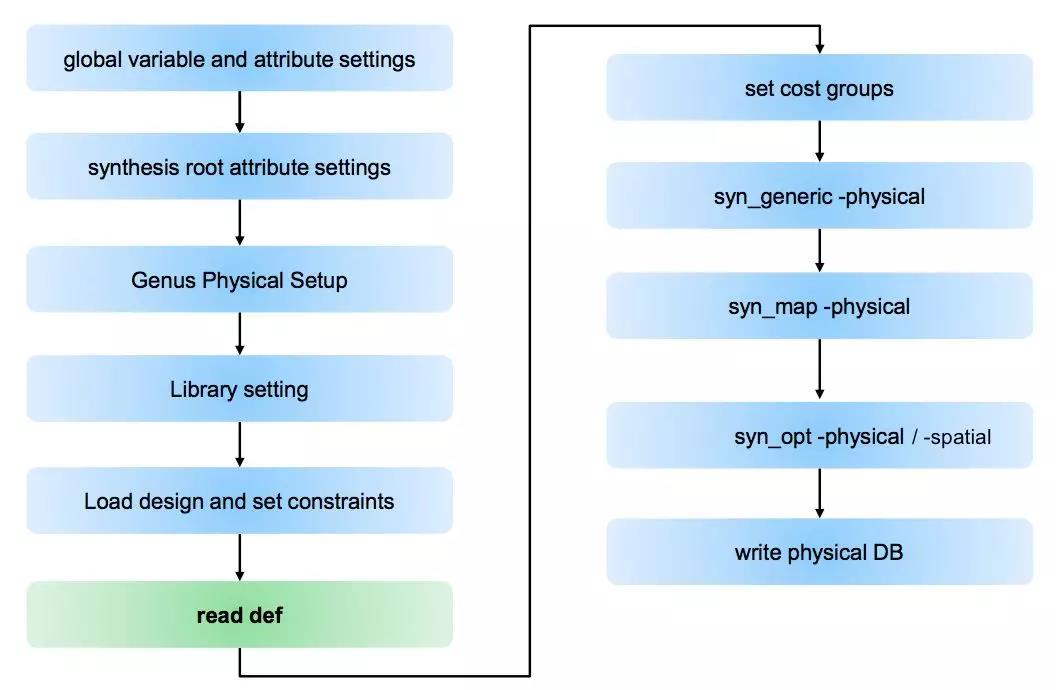

在输入干净了之后就可以命令工具开始做带物理信息的逻辑优化了,Genus 采用的是early physical,即从最开始就带着physical 信息做优化。Genus physical整个优化过程由syn\_gen -physical, syn\_map -physical, syn\_opt -physical/ spatial 三步构成。建议在做完每一步优化后就写一个db 出来,在debug 的时候可以根据需求读入不同阶段的db, 比如debug 前后端module placement 的 correlation, 可以读入syn\_gen 后的DB 起GUI highlight module place 跟Innovus 的module place 对比。

Genus physical 有两种flow, 两个flow 的区别是:

- syn\_opt 所用option 不同,一种是:syn\_opt -physical. 另一种是:syn\_opt -saptial。

- syn\_opt -physical 会调用Innovus 来做placement 跟global route,结果是legalize 的,后端如果吃入Genus 写出的netlist + DEF 则只需要run place\_opt\_design -incr 即可。

- syn\_opt -spatial 用Genus 内嵌的placement 引擎做placement 跟 global route,结果不是legalize 的,后端需要run full place\_opt\_design.

- 两个flow 的相关变量有差别,用户可以根据自己的设计、工艺跟团队构成选择相应flow。

综合完成后,需要check 综合的quality,对于physical aware synthesis 除了PPA 还需要关注 overflow,此处说两点:

- 用report\_timing -physical -gui 可以在layout 中highlight 出完整的timing path,是debug timing最基本的一招而且十分有效,可以看数据流、看走线,看bufferring.

- report congestion可以report 出overflow,打开congestion map 去看congestion 是由什么引起的,然后对症下药。如:跟macro 相关的congestion 需去找后端确认floorplan 是否需要调整;跟结构相关的congestion 是否在综合时需要对这些结构设置map\_to\_mux, 以使其保持mux 结构而非替换成大量的OAI/ AOI; 如是cell堆积引起的congestion,找AE 确认是否有变量让工具可以将congestion 严重区域的cell 推散。

跋:本着去繁就简的原则,本文以Genus 为例简单陈诉了做physical aware synthesis 三个关键的大点,中间很多细节没有涉及到,如各种变量的设置,这些东西在guide 上都可以找到。欢迎驴友补充探讨更正。

作者:陌上风骑驴

来源:https://mp.weixin.qq.com/s/eJ8fYRJBR1E9XbfH95OUOg

作者微信公众号

相关文章推荐

更多IC设计技术干货请关注IC设计技术专栏。