作者:硅谷老李

来源:https://mp.weixin.qq.com/s/EDAjjVJzzyKstI10fqv6Lw

老李今天分享一道Nvidia面试题,是当年老李去面他家onsite的时候被问到的一个面试题。题目放在最后,其实今天这篇推送内容主要是用来记录一下在数字芯片设计中比较常见到的三个握手协议。这三个协议不是复杂的网络传输协议例如TCP三次握手协议,而主要是不同模块之间传输数据的最基本协议。

01 Valid-Ready Handshake

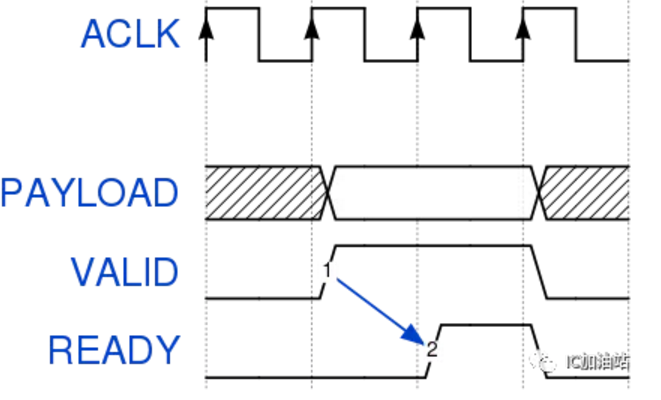

Valid-Ready是非常常见的握手协议,我们熟悉的AXI总线的核心就是Valid-Ready协议。Valid-Ready协议的时序图如下图

Sender 来驱动valid信号和payload也就是data信号,Receiver接受valid和data,返回给Sender ready信号。当Sender有数据要传输的时候,Sender就把valid拉高,并且保持住,valid为高期间要传输的data必须保持稳定,等到Receiver拉高了ready,保持至少一个周期,那么我们就说握手完成,数据从Sender传输到了Receiver。 简单来说,只有当valid和ready同时为高的时候,数据在这个周期传过去。

Valid-Ready是适合高性能传输的协议,只要Receiver可以持续接收数据,那么可以一直将ready拉高,而如果Sender也持续有数据发送,那么可以在看到ready为高之后的周期继续驱动valid为高来传输下一个数据,这样相当于每一个周期都可以有数据从Sender传至Receiver,中间可以没有bubble。这也就是为什么AXI总线选择了Valid-Ready握手协议。

Valid-Ready在设计中有一点要注意:

对于Sender来说,不能依据ready来决定要不要拉高valid;

对于Receiver来说,不能依据valid来决定要不要拉高ready;

也就是说,对于Sender来说,只要你有数据要传输,你就应该拉高valid,而不要管ready是不是1。同理,对于Receiver来说,只要你可以接收数据,你就应该拉高ready,而不要管valid是不是1。如果不满足上面的要求,你很可能遇见Sender和Reciever互相等待彼此而数据无法传输的死锁现象。老李当年就犯过这个错误,很不幸,和老李设计模块通信的另一个模块也犯了这个错误,发生了如下的对话:

老李:你ready为0,说明你没准备好接受啊,那我就不给你valid信号;

老陈:我ready为0又不是说我真没有准备好,你只要有data给我,我只要看到你valid为高我的ready自然就立刻为高了。

老李:。。。

看到了吗,我们之间的距离那么近,可是彼此都不愿意迈出那一步,最后的结果就是谁都干等在那里,错过彼此(怎么画风有点奇怪,咳咳咳。。。)

所以这个时候要反思自己,也要怼同事让他们改正。

02 4-phase Handshake

4-phase handshake其实源自asynchronous design这个大的领域,简单说就是没有时钟驱动,数据的传输都是基于握手。但是老李在实际工作中发现,4-phase handshake其实在有时钟的IP设计中也经常用到,是一个常见且很robust的握手协议。P.S 老李的一个同事当年面硅谷一家手机公司的芯片部门就被问到了这个协议。

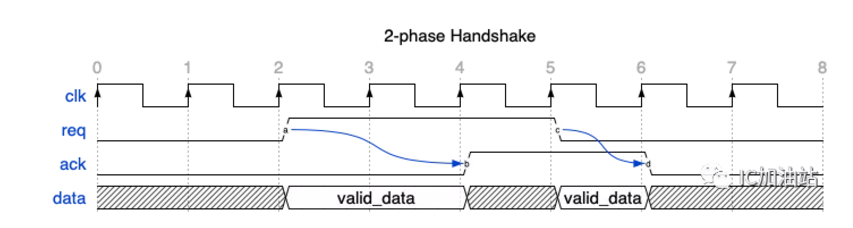

这个握手协议的时序图如下,方便描述,我这里还是画出了时钟clock

其中Sender来驱动req和data,Reciever来驱动ack。之所以叫4-phase,是指以下4个phase:

phase1: sender和receiver都是idle状态,req和ack都为0;如上图的cycle 0, 1

phase2: sender拉高req,等待receiver的ack为高,同时驱动要传输的数据,并保持住; 如上图的cycle 2, 3

phase3: receiver拉高ack,此时req和ack同时为高;表示receiver已经接受到了数据;如上图的cycle 4

phase4: sender看到了ack,知道数据传输完成,于是拉低req。如上图cycle 5

最后receiver看到req被拉低,从而也拉低ack,回到phase1,即上图的cycle 6, 7。

也就是每一次传输数据,都需要经过a->b, b->c, c->d的顺序变化。和valid-ready协议有相似点,但是也有不同点。

相似点:req(valid)变高的时候,sender就需要drive valid data

不同点:valid-ready的valid在传输完一个数据之后可以不拉低,在下一个周期紧接着传输下一个数据,但是4-phase handshake必须要走完4个phase,即看到ack为1了之后必须要将req拉低,否则receiver的ack也不会拉低,receiver也不会认为一个新的传输开始。

由于4-phase handshake必须要走完4个phase,每次完整的握手只能传输一次数据,所以这种握手协议并不适用需要高速高吞吐率的数据传输。适用的场合更多的是对于数据传输延时要求不高,但是对于稳定性要求高的场合,即不能错过data。其实有的时候其实也不需要传输真正的data, req/ack本身可以自带一个握手的意义,表示完成一次握手,req/ack可以用来直接控制sender和receiver的状态机。

03 2-phase Handshake

理解了4-phase handshake, 2-phase handshake就很直观,直接上图

区别在于,2-phase handshake没有了phase3, phase4。当ack为1时,就认为第一次传输结束了。这个时候sender不需要drop req。只有当sender要继续发下一个数据的时候,才需要drop req,而receiver同样以toggle ack来表示数据接收成功。

这样我们看到,其实每一次req的翻转表示一次传输,不论是从0变到1,还是从1变到0。和4-phase handshake相比,在一个完整的4个phase里可以传输2次数据。

由于4-phase 要求req/ack握手结束后都要回到0,所以也称作RTZ(Return- to-Zero)协议。而2-phase的一次握手结束req/ack并不会回到0,所以也称作NRZ(Non-Return-to-Zero)。

2-phase尽管传输速度快,但是设计起来稍微复杂一点,因为要进行edge detection,同时由于每次req 翻转都代表了一个新的传输,所以sender和receiver的初始复位关系要很仔细地设计,否则容易产生一个不期望的garbage传输。

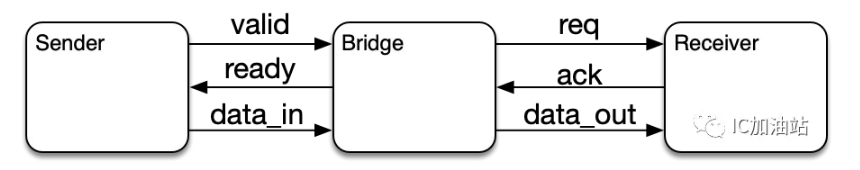

好了,终于到了题目开始说的Nvidia的面试题了。题目其实不复杂,就是要设计一个valid/ready到4-phase handshake的一个转换器。画出框图如下

设计中间这个bridge模块,它本身是valid/ready的slave,又是4-phase handshake的master,要求在40分钟内画出状态机,写出完整的verilog code。

Follow up question: 给定sender的数据产生burst速率,以及receiver的接收burst速率,如何来确定bridge里的FIFO的深度。

如果你熟悉了上面的握手协议,那么你可能可以直接开始思考设计,否则的话要让面试官给你讲解清楚两个协议可能还要花掉10分钟左右的面试时间。好了,这个题目就留作大家自己的练习吧。

相关文章推荐

更多IC设计技术干货请关注IC设计技术专栏。