内容预警:本文仅从技术方面讨论数字后端新人的成长建议,大量内容包含作者的主观感受,如有不同意见欢迎留言讨论!文章较长需要些时间,请保持耐心。

初学者遇到问题如何分析?

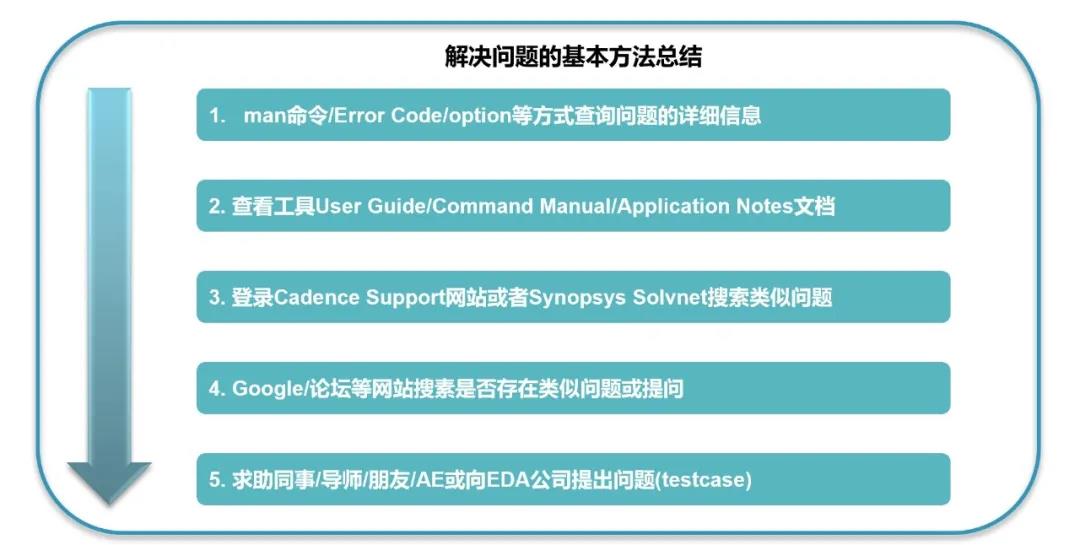

很多人刚开始工作时对遇到的问题几乎都是束手无策,这本来是十分正常的事,但自己心里难免还是会有压力。本质原因还是学校中的知识与工作所需的知识不匹配,导致我们刚开始工作后的短暂时期内对工作所需的基础知识还处于很匮乏的状态,再加上数字后端本身也具有知识点较零碎对初学者不太友好的特点,更会加重这种烦恼。尽管如此,我们还是能够从一些非常基本的原理和步骤出发试图找到一些解决办法来缓解大家的焦虑,也帮助大家更快地适应工作环境。我通常将常见的分析查找问题的方法分成以下几个步骤:

我们举两个个非常常见的例子大家来感受一下:

问题: 跑任务的时候遇到了一个或多个Error或者整个任务直接crash跑不下去怎么办?

分析:一般工具报出的error都会有唯一的error code,这类error的通常解决方案是通过man命令查看详细的内容,搜solvnet或者cadence support,如果没有网站的账号可以搜user guide, command reference manual, error/warning guide等文档,最后就是搜google。但仅仅是这几个步骤也有相当一部分人根本不想去做,很多人遇到问的第一反应就是问别人,先不说长期这样做对方作何感受,单就对自己本身的成长而言并不是最好的方法。对于crash问题,解决起来会更复杂一些。一般来说先要逐个查看crash前出现的error,不少crash问题和error息息相关;error之外的warning也要关注,有的时候一两个奇怪的warning展现的信息非常有价值;另外还需要对比没有crash的任务和crash的任务在哪些地方有区别,发生变化的地方很可能是导致crash的原因;最后就是求助于AE看看是否有类似的案例经验。当然AE最常见给出的办法就是升级版本,因此我们自己也可以尝试更换工具版本来确认是否可以解决以及问题能否复现。

上述过程可以对一般问题提供解决思路,但是对于一些经验化的问题可能并没有那么简单,网上的各种资源也不一定能够帮上忙,因为这类问题和设计本身都有很大关系,不可能大家都拿到网上来一一记录。比如下面这个栗子:

问题:发现place opt之后出现局部congestion怎么办?

分析:首先我们应该理解congestion代表的是绕线资源不足。对此很直接的想法就是定位congestion的位置物理,通常可以通过congestion map来查看。接下来可以选择看看到底哪(些)层绕线资源不足,icc2中可以支持分层查看congstion。然后一般会出现几种典型的情形:在macro的channel中、在macro或者floorplan的拐角处、在纯std cell分布区域。如果是前两种情形,解决办法就相对简单了,你可以快速判断出是由于空间不够引起的。我们可以单纯地调整floorplan,在拐角处加blockage等都可能有效,如果这些办法你完全不知道甚至可以去请教身边的人。如果是第三种情况,需要你进一步分析一下出现congestion区域的std cell都属于哪个或者哪几个module,哪些方向的走线可能导致了congestion的问题。因为即使你要去求助其他人,这些信息也是对方最先需要知道的内容。

平时有很多向我求助并迫切地表示想要快速提高的新人同学,有不少人可以比较准确地描述自己的问题,并且告诉我他做过什么尝试,但是对于更多的人我很难感受到他们在解决问题上做出了什么尝试。很多人去论坛上,去群里或者其他网站上到处提问已经是他们做过的最大努力,但是正如我们上篇文章所讲,很多人的提问方式是注定不会得到答案的。想要真正实现自我技能的充分积累,自己主动地学习、项目中的积累和与其他人的交流是缺一不可的。很多人过于注重后面两项甚至只重视第三项,而完全忽略的自己学习的过程。

如何积累知识和技能?

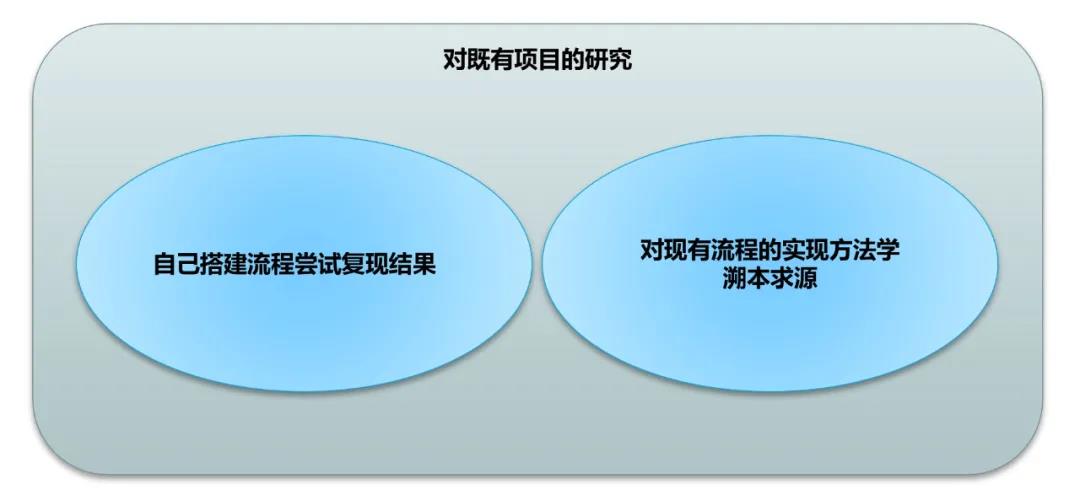

首先,自己手头有项目的务必好好研究。很多初学者觉得已经做完的项目没有挑战性,那么请尝试在不使用公司现有流程的前提下复现相同的结果,你可能会遇到几种结果:太顺利了以至于根本不需要任何调整,这种情况请看看你加的约束和原始项目是否完全一致;另一种情况就是你根本做不下去,以至于完全复现不出来;更多的时候其实我们会发现在复现的过程中会遇到相当多的问题,很多问题甚至你从来都没想到会出现,这也恰恰是流程存在的意义,它帮助你绕过了很多前人踩过的坑,而大多数人常常完全忽视了这部分的价值。因此在通过尝试复现结果也可以充分理解设计,约束和流程,积累到原来接触不到的知识和技能。

其次,对已经做过的项目要尽力做到知其然也要知其所以然。比如我们知道某些macro起到ESD防护的作用,那么我们在有时间和精力的前提下应该深挖ESD的成因以及在怎样的情况下会发生;ESD防护的原理是什么以及针对当前工艺和项目ESD的防护策略是如何制定的。

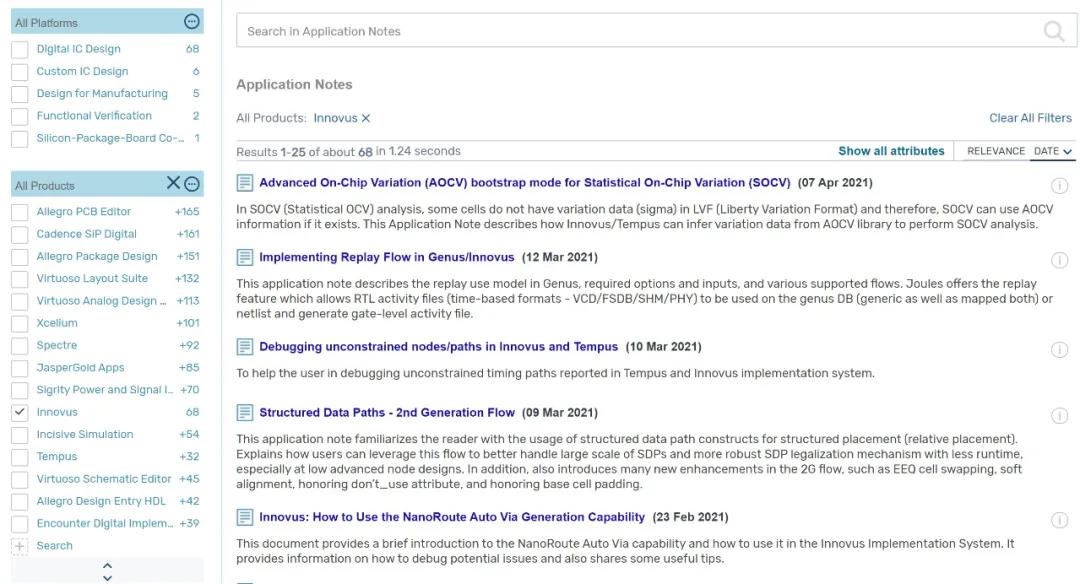

如果手头没有项目可以研究,那么看书、文档和文章是一个很好的途径。很多人找我推荐书籍,但是后端专业的书籍并不多,中文的更少,少数几本经得过时间考验的也基本被人提烂了,我更建议看一些英语书籍和原装的user guide,这方面synopsys在很多概念的解释方面其实比较到位,cadence的文档也质量也在逐渐提高,看多了也更容易积累。

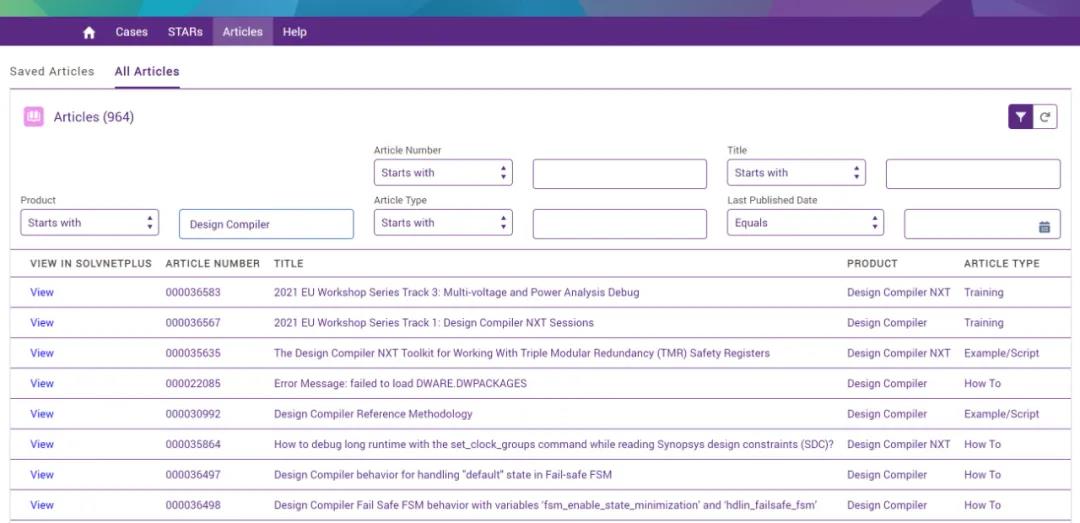

solvnet和cadence support上的有大量资源可以利用,最直接的资源解释各类工具的文档,入口分别如下:

### SolvNet

https://solvnetplus.synopsys.com/s/

### Cadence Support

https://support.cadence.com/apex/HomePage如果你还不知道那就已经错过了太多资源。在这两个网站中,个人认为最有价值的东西其实是各类实用经验笔记(application notes)和问题解决方法(trouble shooting)。以SolvNet为例,通过下面的界面可以访问到众多文章,文档甚至视频,不仅可以获取很多重要的小技巧,也可以随时对工具的最新功能和实践结果有比较深入的了解。通过工具类型、文章标题等筛选所需要的内容可以让搜寻过程事半功倍。

Cadence Support可以找到类似的功能和文章,不过个人感觉在积累的数量和质量上还不能和SolvNet相比,但是相信随着Cadence方案的逐渐推广,整个数字设计解决方案的相关文档也会更加丰富起来。

通过这样不间断地积累掌握各种问题的解决方案,可以积累到非常多的经验和技巧。

除了EDA厂商的网站,用Google搜索英文网站也是一个很好的办法。你会发现很多外国人对基本概念的诠释相当到位,你所需要做的的只是积累一点点专业词汇,然后就可以通读绝大部分文章。很多英文文章和视频都是印度人做的,现实中大家可能感觉他们中间的很多人干活可能不行,但是在外网上能够持续输出的人在讲述基本原理的时候可能比很多工程师要深入浅出得多,尤其是配图完善的文章读起来也更容易理解。当然很多个人写的东西也需要带着怀疑的态度去看,不可能每个人写的所有东西都是准确无误的,此时交叉对比阅读加上自己的思考可能会更有收获。

最后就是一些学术论文的研究,很多时候对于设计方法学的改善会有很大启发。IEEE上通过关键字的搜索可以找到很多和后端设计相关的论文,如果你对它的内容感兴趣可以尝试去下载下来读一读。当然下载这步可能需要一些技巧,但是相信熟练应用互联网的你应该能够找到办法,在此就不详细说了。

总结一下,在技术积累的过程中做项目是重要的却不是唯一的方法,尤其是做过几年之后项目带来的积累将慢慢变少,而不断坚持的自我学习将逐渐带来优势。

来源:https://mp.weixin.qq.com/s/Cp0b9uj3pKyFIgPL3TTWqg

推荐阅读

如果大家有任何后端技术与职业发展方面的问题,抑或关于数字后端感兴趣的技术话题想要了解和探讨,欢迎关注我的知乎专栏: 数字IC后端设计工程师修炼之路

同时欢迎关注微信公众号:数字后端芯讲堂,一起探讨技术,共同提升!

本极术专栏也会同步更新芯片设计后端的技术干货,也请关注数字IC后端设计工程师修炼之路。