之前的文章我们引入了不少低功耗设计的基本概念,同时也介绍过芯片的总体功耗计算方法,其中就包括internal power的定义。今天想深入挖掘internal power以及它在应用过程中有哪些细节需要大家注意。

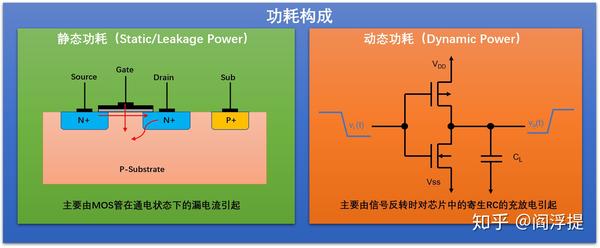

首先还是回顾一下关于数字芯片的功耗定义:主要由静态功耗(Static Power)和动态功耗(Dynamic Power)组成。二者的主要起因可以参考下图:

简而言之,静态功耗是芯片中的部分或全部电路在通电但不工作的状态下的功耗;动态功耗是芯片在正常工作时因信号翻转引起的功耗。而今天我们想要深挖的internal power,其实是动态功耗的一种。在数字电路中,动态功耗一般分为internal power和switching power,在此我们将重点介绍一下internal power。

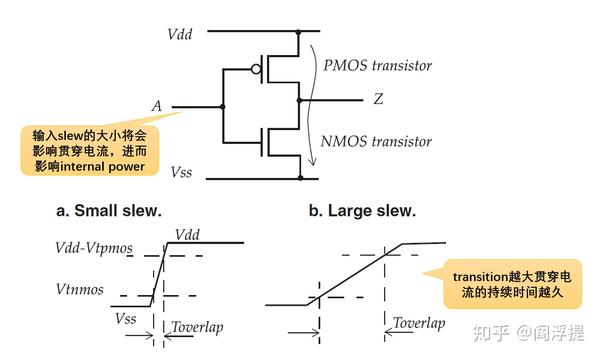

很多人都知道internal power的定义是在cell内部由于充放电而产生的功耗,每个cell的功耗数值都可以在.lib文件中通过特定的查表方式获取。其实贡献internal power的因素应该分为两个因素:一是信号翻转时由于NMOS和PMOS同时导通而产生的短暂但巨大的贯穿电流;二是给内部和外部负载充放电所消耗的能量。对于第一种贯穿电流可以参考下图:

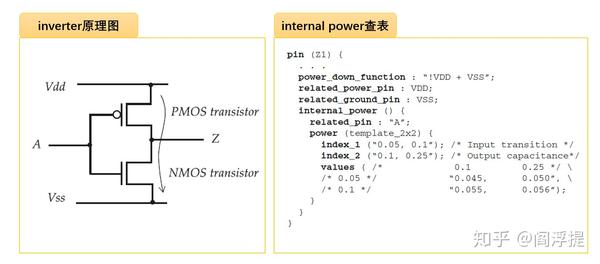

而对于第二种充放电引起的功耗,其实不同类型的cell的表现形式略有不同,internal power计算方式和在.lib中的表现形式也不尽相同。我们以三种主要的cell类型来说明:

第一种cell类型:单输入cell。 这类cell以inverter为代表,仅有一个输入和输出,它的internal power计算方式最为简单直接, 就是input transiton和output load的二维查表,而且需要注意,这里的internal power是定义在输出端的:

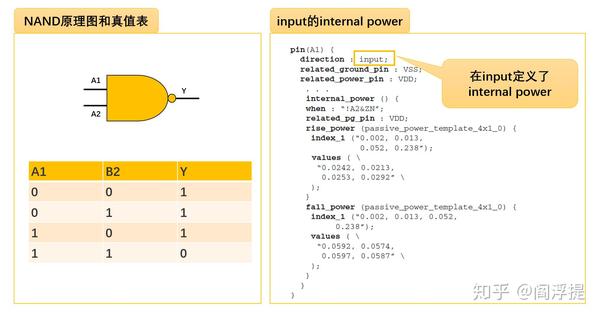

第二种是多输入的组合逻辑门如nand,xor等。 这类cell有一种共同点,那就是在特定条件下某一个或者几个pin的输入值对输出不造成影响,例如当nand的A1输入为0时,不管A2的输出是什么,最终输出都是1。此时尽管A2对输出没有贡献,但是它仍然会消耗一部分功耗,而这部分功耗会单独在.lib文件中有所体现:

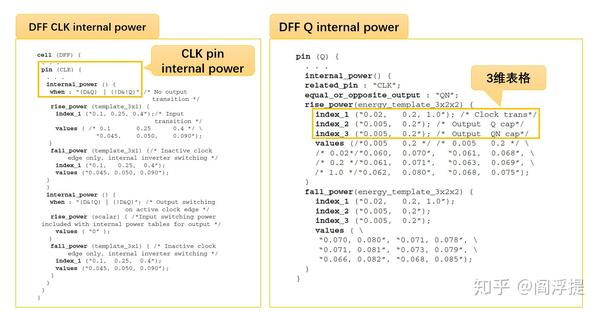

第三种就是时序逻辑门如DFF。 它的特殊之处主要有两点:一是输入的CLK pin即使在锁存的数值没有变化的时候仍然会消耗能量,具体原因大家可以参考DFF的内部结构;二是DFF一般都存在输出Q和取反值QN,每次Q的变化都会导致QN也发生变化,这部分QN的翻转也会消耗额外的能量,因此输出pin上的internal power会变成input, Q和QN负载的三维表格:

以上就是关于internal power的相关介绍,大家可以对照自己手中的项目去印证是否如此,如果有哪里不符合也请留言区告诉我一起讨论。

以上就是本篇的全部内容,如果你觉得学到了新知识,请点个赞再走~

重磅消息,粉丝福利!

近期小编开发了一台用于芯片设计的云服务器,和IC企业的设计环境相同,里面包含所有主流前后端EDA工具的最新/次新版本、几种开源45nm/32nm/14nm的工艺库和多个实验项目,非常适合初学者学习。每个人可以有一个独立账号可以随时随地用VNC远程访问服务器,里面的所有资源包括我开发的一些脚本和小工具都免费使用,只需分担一下云服务器的购置费用和服务器开发维护费用即可。小编会带着有需要的同学从头做一个小项目来帮助大家深入理解后端的工作和工具使用方法,而且不会是跑流程就能完成的,需要大家用原生命令一点点把设计做起来。目前首批开放的10个账号已用完,第二批又开放10个账户就等你来!有兴趣的同学可以在知乎私信小编咨询,10个账号先到先得!

推荐阅读

如果大家有任何后端技术与职业发展方面的问题,抑或关于数字后端感兴趣的技术话题想要了解和探讨,欢迎关注知乎专栏: 数字IC后端设计工程师修炼之路同时欢迎关注微信公众号:数字后端芯讲堂,一起探讨技术,共同提升!

本极术专栏也会同步更新芯片设计后端的技术干货,也请关注数字IC后端设计工程师修炼之路。